# IN THE UNITED STATES DISTRICT COURT FOR THE WESTERN DISTRICT OF TEXAS WACO DIVISION

BiTMICRO LLC,

Plaintiff,

Civil Action No.: 6:22-cv-335

v.

INTEL CORPORATION,

Defendant.

JURY TRIAL DEMANDED

## **COMPLAINT FOR PATENT INFRINGEMENT**

Plaintiff BiTMICRO LLC ("Plaintiff" or "BiTMICRO"), through its attorneys, for its Complaint against Intel Corporation ("Intel" or "Defendant"), demands a trial by jury and alleges as follows:

#### **FACTUAL INTRODUCTION**

- 1. The novel inventions disclosed in the Asserted Patents in this matter were invented by BiTMICRO Networks, Inc. ("BNI"). BNI was founded in 1995 and was a leader in enterprise storage for mission-critical computing, particularly for military applications. BNI's storage devices are best known for exceeding the extreme performance and data integrity required for enterprise, industrial, and military environments.

- 2. BNI made critical advances in the solid state drive ("SSD") and integrated circuit technology that is embodied in the Asserted Patents. The Asserted Patents in this case are the result of the work from 15 different BNI engineers and developers, spanning a period of over a decade.

3. Innovation was one of the keys to the success at BNI. The company was involved with research and development projects in the SSD industry for about 20 years, over which time it accumulated over 50 U.S. patents, all of which are now owned by BiTMICRO.

# **THE PARTIES**

- 4. BiTMICRO is the current owner and assignee of the Asserted Patents and holds all rights necessary to bring this action.

- 5. BiTMICRO is a Delaware limited liability company with its principal place of business located at 11921 Freedom Drive, Suite 550, Reston, Virginia 20190.

- 6. Defendant Intel Corporation is a Delaware corporation with its principal place of business at 2200 Mission College Boulevard, Santa Clara, California 95054.

- 7. Intel is registered to do business in the State of Texas and has been since at least April 1989. Defendant may be served by serving its registered agent, C T Corporation System, 1999 Bryan St., Ste. 900, Dallas, TX 75201-3136.

- 8. Intel has places of business at 9442 N. Capital of Texas Hwy., Bldg. 2, Suite 600, Austin, Texas 78759; and 1300 S. Mopac Expressway, Austin, Texas 78746.

### **JURISDICTION AND VENUE**

- 9. This action arises under the patent laws of the United States, Title 35 of the United States Code. Subject matter jurisdiction is proper in this Court pursuant to 28 U.S.C. §§ 1331 and 1338(a).

- 10. This Court has personal jurisdiction over Intel in accordance with due process and/or the Texas Long Arm Statute because, in part, Intel "[r]ecruits Texas residents, directly or through an intermediary located in this state, for employment inside or outside this state." *See* Tex. Civ. Prac. & Rem. Code § 17.042.

- 11. This Court also has personal jurisdiction over Intel because it has committed and continues to commit acts of direct and/or indirect infringement in this judicial district in violation of at least 35 U.S.C. §§ 271(a) and (b). In particular, on information and belief, Intel has made, used, offered to sell, and/or sold the accused products in this judicial district, and has induced others to use the accused products in this judicial district.

- 12. This Court also has personal jurisdiction over Intel because, *inter alia*, Intel (1) has substantial, continuous, and systematic contacts with this State and this judicial district; (2) owns, manages, and operates facilities in this State and this judicial district; (3) enjoys substantial income from its operations and sales in this State and this judicial district; (4) employs Texas residents in this State and this judicial district; and (5) solicits business and markets products, systems and/or services in this State and judicial district including, without limitation, those related to the infringing accused products.

- 13. Venue is proper in this District pursuant to at least 28 U.S.C. § 1319(b)-(c) and § 1400(b), at least because Intel, either directly or through its agents, has committed acts within this judicial district giving rise to this action, and continue to conduct business in this District, and/or has committed acts of patent infringement within this District giving rise to this action.

### **FACTUAL ALLEGATIONS**

# **BiTMICRO Patents**

14. The BiTMICRO inventions contained in the Asserted Patents in this case relate to groundbreaking improvements to memory controllers, mapping tables for memory devices, storage device security, memory saving during power loss, microchip configuration, and system booting as will be further described below.

#### **U.S. Patent No. 7,826,243**

- 15. On November 2, 2010, the U.S. Patent and Trademark Office duly and lawfully issued United States Patent No. 7,826,243 ("the '243 Patent"), entitled "Multiple chip module and package stacking for storage devices." A true and correct copy of the '243 Patent is attached hereto as **Exhibit A**.

- 16. BiTMICRO is the owner and assignee of all right, title, and interest in and to the '243 Patent, including the right to assert all causes of action arising under said patent and the right to any remedies for infringement of it.

- 17. The '243 Patent describes, among other things, module stacking and packaging for electronic devices. Specifically, multiple modules, such as semiconductor dies, are stacked together and connected to create a stacked module. A stacked module creates a package with specific functions or a range of memory capacity. Multiple packages can be stacked to create a desired memory capacity or different packages can be stacked to create a desired functionality. The stacking techniques described in the '243 Patent allow large capacity storage and high functionality devices to be implemented in a smaller package, saving space on an integrated circuit board and thus allowing smaller devices to include memory capacity or functionality that may otherwise be unachievable. The '243 Patent further describes interconnections and signal routing between two or more of the plurality of modules. The signal paths described in the '243 Patent may be used to test stacked modules to ensure proper function. Furthermore, the signal paths may be used in the operation of a stacked module.

- 18. Prior to the inventions in the '243 Patent, processing and memory chips in computer systems were typically arranged as separate packages within a device, with electrical connections between the packages to facilitate communications between the packages. For example, in an

electronic storage device, separate packages were necessary for an interface controller, a DMA controller, a processor, and the memory modules. This type of design required a significant amount of physical space within the device and therefore presented an obstacle to miniaturization of the device. The inventions in the '243 Patent solved this problem by providing a way for processing and memory chips to be stacked on top of each other to minimize the amount of space that the chips occupy within the device while maintaining reliable interconnectivity between the chips. (*See* Ex. A at 1:6-2:2).

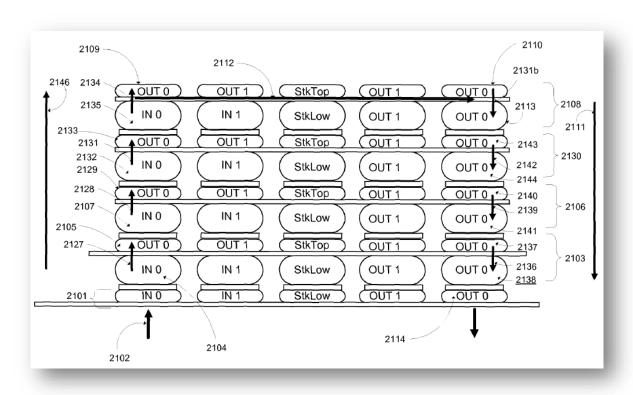

19. An exemplary embodiment of the '243 inventions is depicted in Figure 21a of the '243 Patent as follows:

20. As shown in Figure 21a, a main board 2101 has multiple chip modules 2103, 2106, 2130, and 2108 stacked on top of it. The modules are electrically connected to each other through a series of ball and pad connections. For example, an input signal 2102 can be passed from the main

board through the IN ball 2104 to the OUT pad 2105 of base module 2103. From there the input signal can be passed through the IN balls and OUT pads of the other modules stacked above in a serial chain until the signal reaches the end module 2108. In the end module, the signal can be routed internally through the module via connection 2112 to another pad 2110 on the end module. The signal can then be passed back down through the stack of modules to the main board through a similar serial chain of ball and pad connections between the modules. (*See* Ex. A at 9:61-10:35).

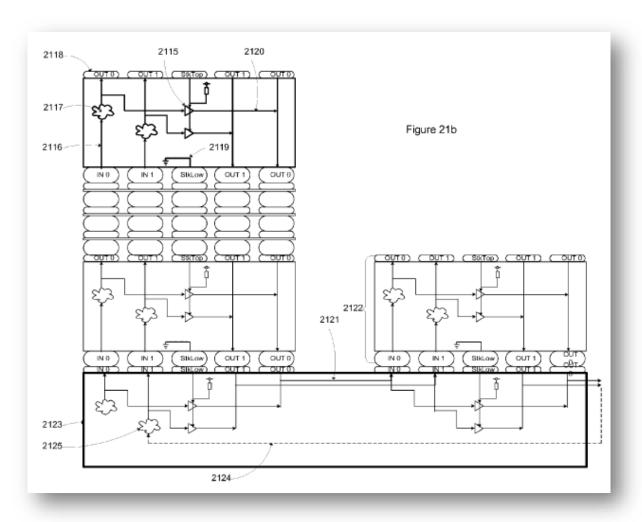

21. Figure 21b in the '243 Patent provides an example of how the end module can be configured to receive the incoming serial chain signal and route the signal to other pads:

(See also Ex. A at 10:8-35).

22. The novel features of the '243 inventions are recited in the claims. For example, claim 1 of the '243 Patent recites:

A stacked module comprising a plurality of modules each comprising:

one or more active ports for carrying one or more active signal;

one or more passive ports for passing through the one or more active signals;

a first serial chain route that includes at least one serial chain connection, the serial chain connection including: a serial chain circuit, a serial chain input, and serial chain output; said serial chain input coupled to said serial chain output through said serial chain circuit;

a second serial chain route and a control circuit for enabling a routing path that connects the first serial chain route with the second serial chain route within an end module;

and said control circuit is disposed to enable the routing path in response to a control input signal received from another module from the plurality of modules when the end module is coupled to the another module.

(Ex. A at 10:42-60). Claim 1 of the '243 Patent describes claim elements individually or as an ordered combination, that were non-routine and unconventional at the time of the inventions in 2005 and an improvement over prior art, as it provided a semiconductor stacking and packaging design (not previously available) that allowed signals to be carried and routed through multiple stacked modules via serial chain routes. (*See id.* at Abstract, 1:6-2:2).

#### U.S. Patent No. 9,135,190

23. On September 15, 2015, the U.S. Patent and Trademark Office duly and lawfully issued United States Patent No. 9,135,190 ("the '190 Patent"), entitled "Multi-profile memory controller for computing devices." A true and correct copy of the '190 Patent is attached hereto as **Exhibit B**.

- 24. BiTMICRO is the owner and assignee of all right, title, and interest in and to the '190 Patent, including the right to assert all causes of action arising under said patent and the right to any remedies for infringement of it.

- 25. The '190 Patent describes, among other things, a multi-profile memory controller for computing devices. Specifically, the '190 Patent describes a memory controller that can operate with memory locations, memory devices, or both which are associated with different memory attributes, different attribute qualifiers, or the like. For example, a non-volatile memory storage device may be portioned to allow a memory controller to treat a portion of the memory device as a temporary cache memory to store data prior to writing the data to a permanent storage location. This eliminates the need for a separate memory cache, often composed of volatile memory. This has the additional advantage of maintaining the temporary data in the non-volatile cache partition in the event of an unexpected power loss.

- 26. Prior to the inventions in the '190 Patent, memory controllers were designed to operate with memory locations and memory devices that all shared the same set of memory device characteristics, such as block size. Due to this limitation, there was no way of varying how a memory controller performed read and write operations on different memory locations or memory devices. The '190 Patent overcame this limitation by disclosing a novel multi-profile memory controller with the ability to operate differently with memory locations and memory devices based on differences between the attributes of particular memory locations and memory devices. (*See* Ex. B, at 1:20-60).

- 27. As described in the '190 Patent, a memory store includes multiple addressable memory locations, and each location is associated with a set of memory attributes, which can include, for example, the type of memory device in which the memory location is located, the data

size used by the memory device, or the memory protocol of the device. (*See* Ex. B, at 2:63-3:13). These attributes are organized into device profiles that can be used by a memory controller connected to the memory store to determine how memory transactions are to be performed with each memory location. (*See id.* at 3:14-4:25). By analyzing the requirements of the requested memory transaction and comparing those requirements to the device profiles, the memory controller selects the appropriate memory location for the memory transaction. The criteria used by the controller to select the optimal memory location for the memory transaction based on the stored attributes within the device profiles can be programmed in any number of ways. (*See id.* at 7:60-9:48).

28. The novel features of the '190 inventions are recited in the claims. For example, claim 59 of the '190 Patent recites:

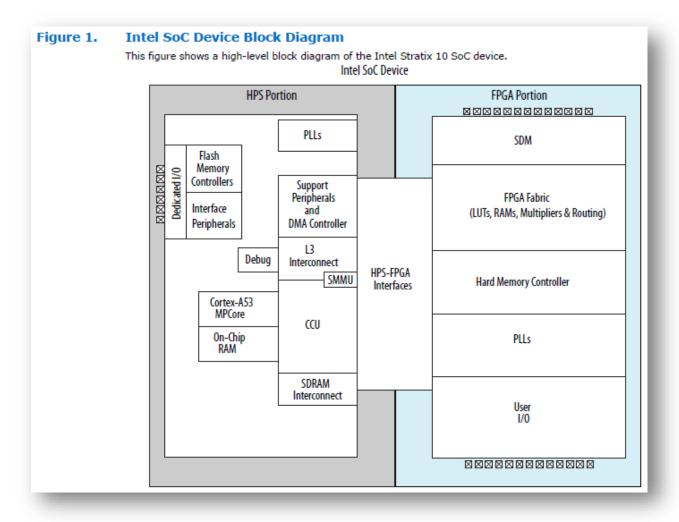

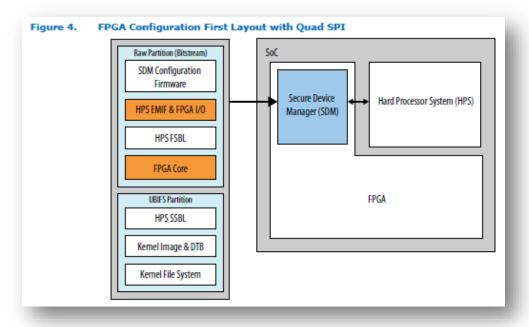

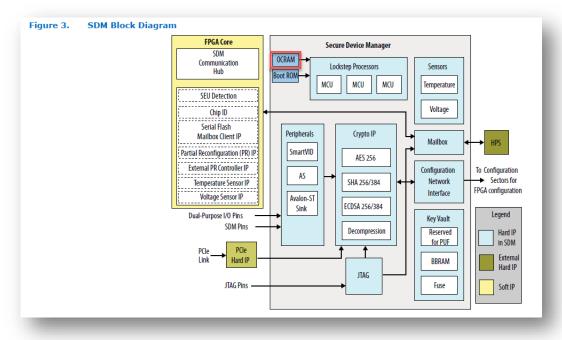

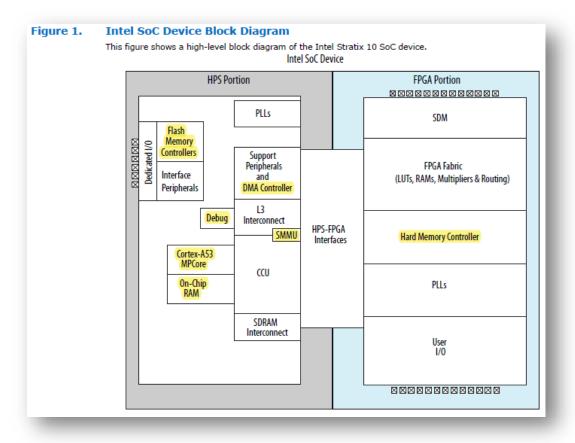

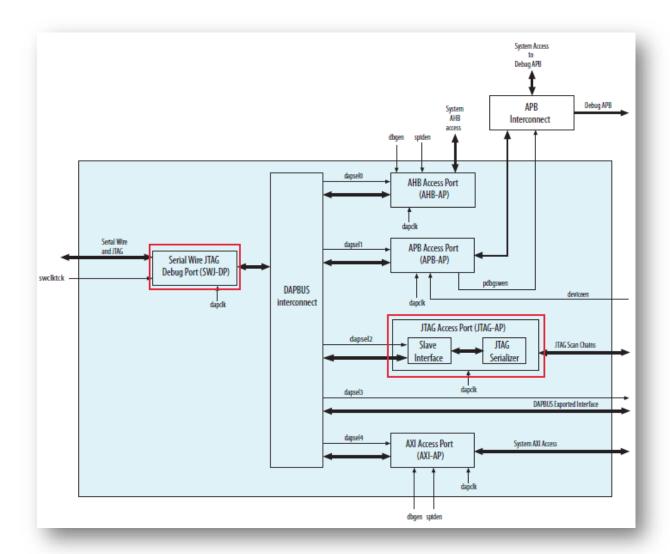

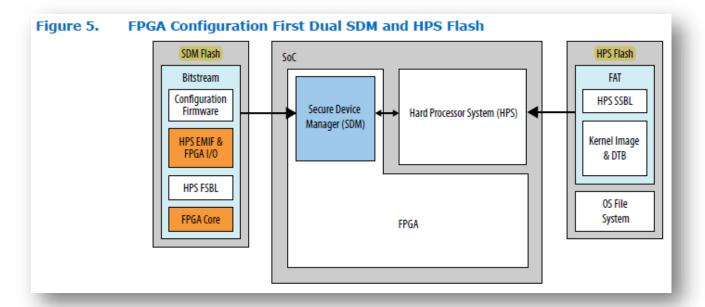

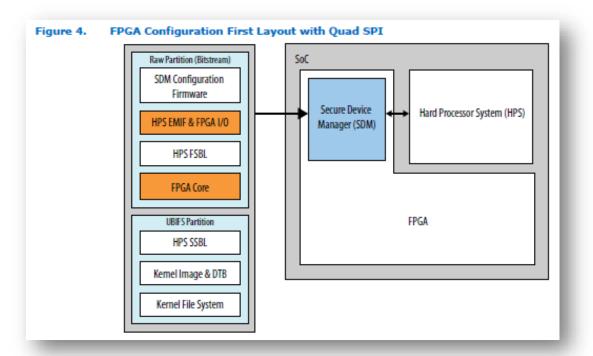

A memory controller comprising:

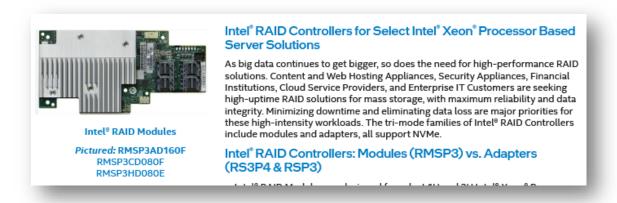

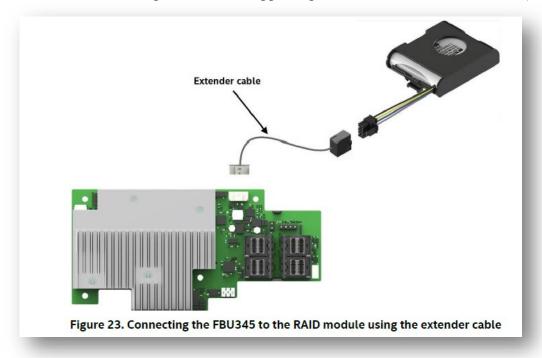

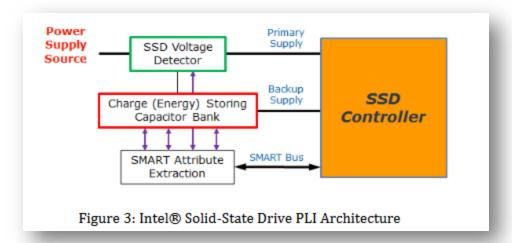

an interface controller coupled to a memory device interface and an input/output (IO) device interface;

a memory store;

wherein the memory device interface is directly coupled to the memory store;

said interface controller disposed to perform a memory transaction by addressing a first memory location in the memory store,

said first memory location and a second memory location respectively associated with a first device profile and a second device profile;

wherein said first device profile is optimal for a data type subject to the memory transaction, wherein said data type comprises one of a random data type or a sequential data type;

said interface controller identifies command details for causing the memory transaction to be performed, wherein said command details comprising the first memory device;

said device profile representing a first set of attributes of said first memory location, and said second device profile representing a second set of attributes of said second memory location, and a difference exists between said first and second device profiles;

said interface controller obtaining the first set of attributes after identifying the command details; and said addressing of said first memory location includes using said attributes from said first device profile;

and said addressing of said first memory location includes selecting a transfer size for the memory transaction, wherein the transfer size is a function of a data size of the memory transaction and the first set of attributes.

(Ex. B at 18:34-65). Claim 59 of the '190 Patent describes claim elements individually or as an ordered combination, that were non-routine and unconventional at the time of the inventions in 2009 and an improvement over prior art, as it provided a memory controller (not previously available) with an interface controller capable of performing memory transactions with different transfer sizes on different memory locations based on attributes associated with the different memory locations as defined in differing device profiles for those memory locations. (*See id.* at Abstract, 1:20-60, 2:41-62).

#### U.S. Patent No. 8,010,740

- 29. On August 30, 2011, the U.S. Patent and Trademark Office duly and lawfully issued United States Patent No. 8,010,740 ("the '740 Patent"), entitled "Optimizing memory operations in an electronic storage device." A true and correct copy of the '740 Patent is attached hereto as **Exhibit C**.

- 30. BiTMICRO is the owner and assignee of all right, title, and interest in and to the '740 Patent, including the right to assert all causes of action arising under said patent and the right to any remedies for infringement of it.

- 31. The '740 Patent describes, among other things, a mapping table for optimizing memory operations in an electronic storage device. Prior to the inventions in the '740 Patent,

memory operations in solid state storage devices were subject to a number of inefficiencies. As described in the '740 specification, SSDs such as those that include NAND flash memory "suffer from write cycle limitations and to a certain degree, bad blocks. In addition, flash drives use block addressing rather than byte addressing, and these flash drives use block addresses that are usually much larger than the block address used by the host. Block addressing may impose an additional level of complexity and additional processing cycles when performing a write operation, and which in turn, may increase write operation latency. This additional level of complexity may include performing a read-modify-write transaction to complete the write operation." (Ex. C at 1:42-53).

- 32. To address these issues and increase the speed and efficiency of memory operations in their products, SSD manufacturers tried solutions such as adding complex algorithms to handle the management of memory operations and adding more powerful processing devices to run these complex algorithms. (*See id.* at 1:54-2:10). These solutions, however, increased both the cost and design complexity of the SSDs. (*See id.*).

- 33. The '740 Patent overcame this problem by providing a solution that optimizes memory operations in a solid state storage device while minimizing the amount of additional cost and complexity to the design of the device. (*See id.* at 2:11-14). The '740 Patent achieves this through an improved mapping table that "increas[es] the likelihood that, in response to an I/O transaction initiated by a host, the operational load imposed on the storage device by these memory operations will be optimally distributed across different storage device resources, such as by interleaving or parallel memory operations, reducing memory operation latency, increasing operational device efficiency, or both." (*Id.* at 2:14-21; *see also id.* at 3:12-31). For example, the '740 Patent describes a mapping table that includes a set of logical fields that represent a plurality of logical block address (LBA) sets. The mapping table also includes a set of physical block

address (PBA) fields that represent a set of PBAs and access parameters for the PBAs, as well as information that associates the LBA sets with the PBA sets in a highly efficient manner. The mapping table enables the storage device to perform optimized memory operations on memory locations based on the information in the table regarding the relationship between the LBA and PBA sets and the access parameters. (*See id.* at 2:27-49).

34. The novel features of the '740 inventions are recited in the claims. For example, claim 1 of the '740 Patent recites:

A mapping table for optimizing memory operations performed by an electronic storage device in response to receiving an I/O transaction request initiated by a host, said mapping table comprising:

a set of logical fields, including a first logical field and a second logical field, and said logical fields respectively disposed for representing a plurality of LBA sets, including said first logical field disposed for representing a first LBA set and said second logical field disposed for representing a second LBA set, said first and second LBA sets each representing a set of consecutive LBAs;

a set of PBA fields, including a first PBA field and a second PBA field, said set of PBA fields respectively disposed for representing a set of PBAs, including a first PBA disposed for representing a first set of access parameters and a second PBA disposed for representing a second set of access parameters, said PBAs each associated with a physical memory location in a memory store, said set of logical fields and said set of PBA fields disposed to associate said first and second LBA sets with said first and second PBAs:

and wherein, in response to receiving the I/O transaction request, said mapping table causes the electronic storage device to perform optimized memory operations on memory locations respectively associated with said first PBA and said second PBA, if the I/O transaction request is associated with said first and second LBA sets.

(Ex. C at 9:64-10:24). Claim 1 of the '740 Patent describes claim elements individually or as an ordered combination, that were non-routine and unconventional at the time of the inventions in 2006 and an improvement over prior art, as it provided a mapping table (not previously available) that enables optimized memory operations in an electronic storage device through information

stored in a mapping table regarding logical fields, PBA fields, access parameters, and relationships between LBA and PBA sets. (*See id.* at Abstract, 2:27-49).

#### U.S. Patent No. 9,858,084 and U.S. Patent No. 10,120,694

- 35. On January 2, 2018, the U.S. Patent and Trademark Office duly and lawfully issued United States Patent No. 9,858,084 ("the '084 Patent"), entitled "Copying of power-on reset sequencer descriptor from nonvolatile memory to random access memory." A true and correct copy of the '084 Patent is attached hereto as **Exhibit D**.

- 36. BiTMICRO is the owner and assignee of all right, title, and interest in and to the '084 Patent, including the right to assert all causes of action arising under said patent and the right to any remedies for infringement of it.

- 37. On November 6, 2018, the U.S. Patent and Trademark Office duly and lawfully issued United States Patent No. 10,120,694 ("the '694 Patent"), entitled "Embedded system boot from a storage device." A true and correct copy of the '694 Patent is attached hereto as **Exhibit E**.

- 38. BiTMICRO is the owner and assignee of all right, title, and interest in and to the '694 Patent, including the right to assert all causes of action arising under said patent and the right to any remedies for infringement of it.

- 39. The '084 Patent and '694 Patent share the same specification, and both patents claim priority to U.S. Provisional Application No. 61/801,952, filed with the U.S. Patent and Trademark Office on March 15, 2013.

- 40. The '084 and '694 Patents describe, among other things, methods and systems for booting up and initializing an embedded system directly from a storage device.

- 41. As described in the '084 and '694 Patents, "[a]n embedded system refers to an apparatus that is made up of a single or multiple controller chips interconnected to each other on a

printed circuit board" and can also refer to "a single CPU or a multiprocessor system." (Ex. D at 1:22-30; Ex. E at 1:20-28). Prior to the inventions in the '084 and '694 Patents, embedded systems relied on firmware (such as a boot code loader, a basic input/output system (BIOS), an operating system (OS), or application firmware) in order to boot up and initialize the system. As part of this process, the boot code loader would need to copy the BIOS, OS, or application firmware from an external mass storage device to the random access memory (RAM) of the embedded system, whereupon the system's central processing unit (CPU) would read and execute the copied BIOS, OS, or application firmware to perform further initialization and diagnostic tasks before the system could proceed to normal operations. The boot up process for embedded systems therefore required the transfer and loading of large amounts of data before the system could begin normal operations, and there was no ability for the system to self-check the integrity of the BIOS, OS, or application firmware transferred into the RAM. (See Ex. D at 1:31-55; Ex. E at 1:29-53).

42. The inventions in the '084 and '694 Patents addressed this problem by providing more efficient and reliable ways of handling the boot up process of an embedded system using a novel power-on reset (POR) sequencer stored in the nonvolatile memory of the embedded system. By way of example and without limitation, a POR sequencer descriptor may contain data necessary for setting up the configuration registers and managing other initialization processes in the system. Upon power-up of the system, the POR sequencer in the system attempts to retrieve a POR sequencer descriptor from the nonvolatile memory. If a POR sequencer descriptor is detected, the POR sequencer transfers it to the system RAM. The POR sequencer may then perform an integrity check of the POR sequencer descriptor to determine if there are any errors. If no error is detected, the POR sequencer can use the POR sequencer descriptor to, among other things, initialize the

configuration registers as well as coordinate further data transfers necessary for the initialization process with any DMA controllers in the system. (*See* Ex. D at 2:13-4:4; Ex. E at 2:10-4:2).

43. The novel features of the inventions of the '084 and '694 Patents are recited in the claims. For example, claim 19 of the '084 Patent recites:

An article of manufacture, comprising:

a non-transitory computer-readable medium having stored thereon instructions operable to permit an apparatus to perform a method comprising:

releasing components of an embedded system from reset; detecting a power-on reset (POR) sequencer descriptor in a nonvolatile memory;

wherein the POR sequencer descriptor comprises information to initialize configuration registers of the embedded system, Direct Memory Access (DMA) descriptors used to fetch other POR sequencer descriptor fragments, and a system firmware;

copying the POR sequencer descriptor from the nonvolatile memory to a random access memory;

verifying an integrity of the POR sequencer descriptor; and

detecting any error in the POR sequencer descriptor.

(Ex. D at 10:49-65). Claim 19 of the '084 Patent describes claim elements individually or as an ordered combination, that were non-routine and unconventional at the time of the inventions in 2013 and an improvement over prior art, as it provided methods of starting up an embedded system (not previously available) using a novel POR sequencer descriptor stored in nonvolatile memory whose integrity is verified and is checked for any errors before start up. (*See id.* at Abstract, 1:16-2:60).

44. As another example, claim 6 of the '694 Patent recites:

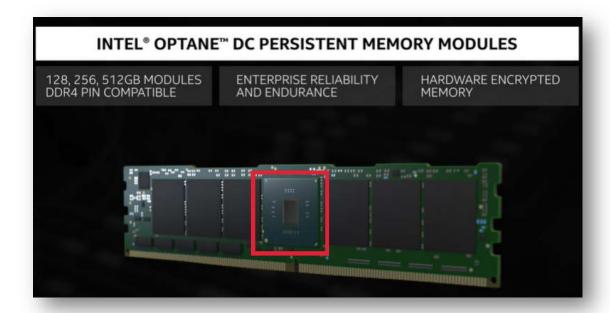

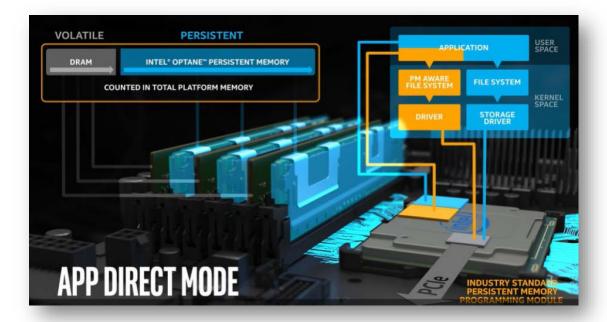

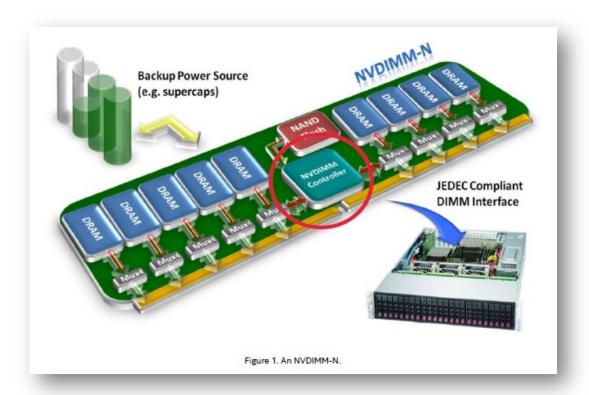

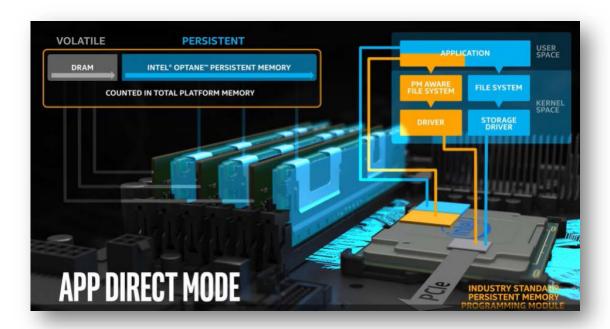

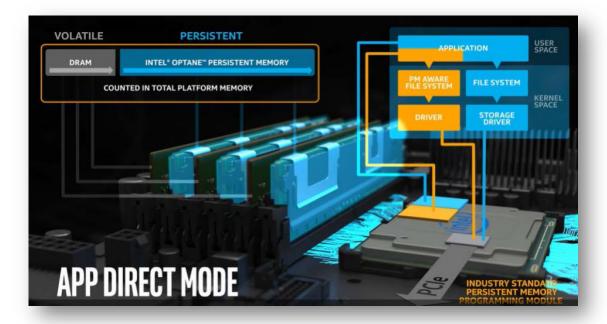

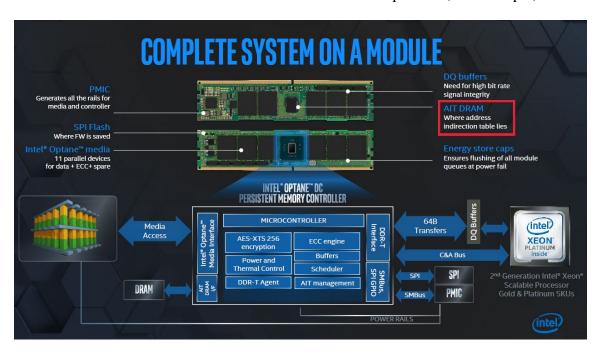

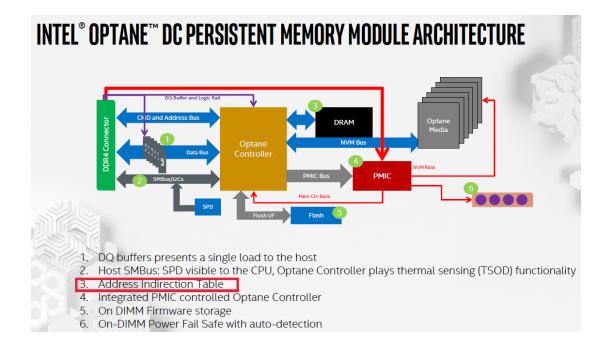

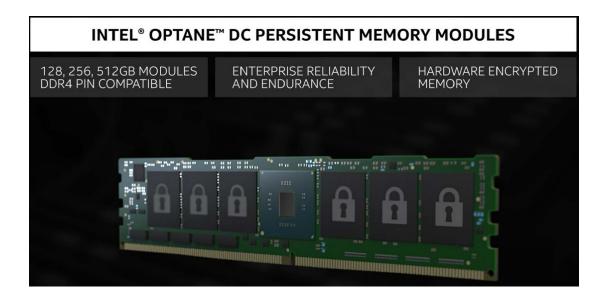

An apparatus, comprising:

an embedded system comprising one or more processors, a reset controller, a storage device controller, one or more direct memory access (DMA) controllers, a

random access memory (RAM) and a memory controller, a nonvolatile memory and a nonvolatile memory controller, a debug interface, and

a power-on reset (POR) sequencer, wherein the POR sequencer uses a POR sequencer descriptor which is a preassembled descriptor that is stored in the nonvolatile memory,

wherein the POR sequencer descriptor includes register information and DMA controller descriptors, and

wherein the POR sequencer reads and uses the register information to update configuration registers of the embedded system.

(Ex. E at 9:64-10:12). Claim 6 of the '694 Patent describes claim elements individually or as an ordered combination, that were non-routine and unconventional at the time of the inventions in 2013 and an improvement over prior art, as it provided an apparatus capable of starting up an embedded system (not previously available) using a minimal amount of data that is used by a novel POR sequencer to update the configuration registers of the system. (*See id.* at Abstract, 1:14-2:58).

# U.S. Patent No. 6,496,939

- 45. On December 17, 2002, the U.S. Patent and Trademark Office duly and lawfully issued United States Patent No. 6,496,939 ("the '939 Patent"), entitled "Method and system for controlling data in a computer system in the event of a power failure." A true and correct copy of the '939 Patent is attached hereto as **Exhibit F**.

- 46. BiTMICRO is the owner and assignee of all right, title, and interest in and to the '939 Patent, including the right to assert all causes of action arising under said patent and the right to any remedies for infringement of it.

- 47. The '939 Patent describes, among other things, systems and methods for controlling data in a computer or memory system when the system loses external power. (*See* Ex. F at Abstract). Specifically, the '939 Patent describes a plurality of capacitors configured to supply power to the computer or memory system, activating those capacitors to supply power in the event

of a sudden loss of external power, and reconfiguring the data in the computer or memory system while that auxiliary power is supplied. (*Id.*). Through the use of the systems and methods described by the '939 Patent, newly written and/or modified data can be stored (or flushed) from the volatile memory to the non-volatile memory in the event of a sudden power loss, and/or enable the data to be erased automatically or manually—in all cases, preserving the security of the stored data. (*Id.*).

- 48. Prior to the inventions in the '939 Patent, computing systems utilized various types of memory for storing and managing data, including volatile memory for main memory and cache, as well as mechanical disk drives for longer term storage. (*Id.* at 1:14-33). One disadvantage of volatile memory, however, is that it requires a constant source of power, or the data stored thereon will be lost. Consequently, when there is a sudden loss of power, there is insufficient time to safely write all the newly written and/or modified data from the volatile memory to the hard disk drive before the system shuts down resulting in data loss and insecurity. (*Id.* at 1:34-45). Batteries could be coupled to the internal power system, but those have a number of disadvantages, including a limited number of charge-drain cycles, large internal resistance, size, and weight. A battery-backed uninterruptable power supply (UPS) could be coupled to the external power supply of the computer system, but those systems suffer from the same or similar disadvantages. (*Id.* at 1:46-58). In addition, prior to the inventions of the '939 Patent, computing systems did not have a means for ensuring that the data to be securely erased when the system loses power. (*Id.* at 1:59-2:21).

- 49. The '939 Patent overcame these various limitations by disclosing novel systems and methods for controlling data in a computer system when the system loses power, comprised of a plurality of capacitors configured to supply power to the computer system, activating those capacitors to supply power in the event of a sudden loss of external power, and reconfiguring the

data in the computer system while that auxiliary power is supplied. (*Id.* at 2:24-37). In addition, these systems and methods allow the computing system to rapidly erase data from a non-volatile memory automatically, in the event of a sudden loss of power, and/or manually. (*Id.* at 2:37-43).

- 50. The novel features of the inventions of the '939 Patent are recited in the claims. For example, claim 10 of the '939 Patent recites:

- 1. A system for controlling data in a computer system when the computer system loses power, the computer system comprising a computer engine, comprising:

means for activating a plurality of super capacitors to supply power to the computing engine based upon power being removed from the computer system;

means for reconfiguring the data in the computing engine; and

means for deactivating the plurality of super capacitors to cut off power to the computing engine based upon the plurality of super capacitors discharging to a predetermined level.

(Ex. F at 7:20-31). Claim 10 of the '939 Patent describes claim elements individually or as an ordered combination, that were non-routine and unconventional at the time of the inventions in or before 1999 and an improvement over prior art, as it used a plurality of capacitors configured to supply power to the computer system when the system loses power, thereby preserving the security of the data stored in volatile memory therein. (*See* Ex. E at Abstract, 1:14-2:21, 2:24-43).

#### **Intel's Use of the Patented Technology**

51. Intel is a multinational technology company and the world's largest semiconductor chip manufacturer. Founded in 1968, Intel's products include processors, flash memory, SSDs, field-programmable gate arrays (FPGAs) and other products that are incorporated into servers, laptops, desktops, smart phones, and tablet computers, which infringe the Asserted Patents. The infringing products also include stacked electronic components such as those found in SDRAM memory, processor/DRAM packages, application processors, high-bandwidth memory, and

products (e.g., mobile phones, tablets, and watches) that incorporate those components or other stacked electronics components. Specific examples of infringing products made, sold, and/or offered for sale in the United States, and/or imported into the United States are discussed below.

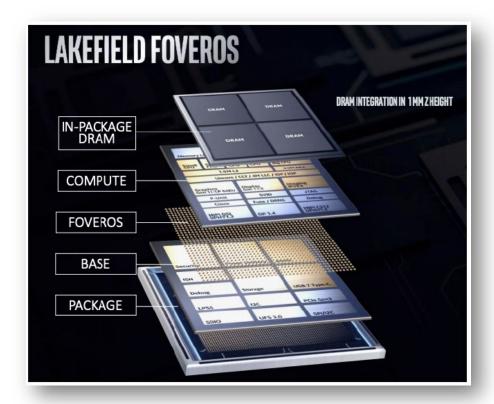

- 52. Intel makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States (or has made, used, sold, offered for sale, and/or imported into the United States) vertically stacked integrated circuits under the Foveros brand, which infringe one or more claims of the '243 Patent. Such products include the Lakefield Foveros product.

- 53. Intel makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States (or has made, used, sold, offered for sale, and/or imported into the United States) SSDs with SLC caching capabilities, which infringe one or more claims of the '190 Patent. Such SSDs include, for example, Intel's 545s Series, Pro 5450s Series, 600p Series, Pro 6000p Series, 660p Series, 665p Series, 670p Series, 760p Series, and Pro 7600p Series SSDs.

- 54. Intel makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States (or has made, used, sold, offered for sale, and/or imported into the United States) memory products under the term "persistent memory," which infringe one or more claims of the '190 Patent. Such products include Intel's Optane Persistent Memory and Persistent Memory 200 Series (PMem) modules.

- 55. Intel makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States (or has made, used, sold, offered for sale, and/or imported into the United States) Non-Volatile Memory Express (NVMe) SSDs, Optane SSDs, and Optane memory products, which infringe one or more claims of the '740 Patent. Such products include Intel's DC P3500, DC P3600, DC P3608, DC P3700, 600p, 660p, 665p, 670p, 760p, Pro 6000p, and Pro 7600p Series SSDs; Optane 800P, 900P, 905P, DC P4800X, DC P4801X, DC D4800X, DC P5800X, and

P1600X Series SSDs; and the Optane Persistent Memory and Persistent Memory 200 Series modules, Optane Memory M10, Optane Memory H10 with Solid State Storage, and Optane Memory H20 with Solid State Storage.

- 56. Intel makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States (or has made, used, sold, offered for sale, and/or imported into the United States) FPGA products, which infringe one or more claims of the '084 and '694 Patents. Such products include, for example, Intel's Stratix 10 line of FPGA products.

- 57. Intel makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States (or has made, used, sold, offered for sale, and/or imported into the United States) RAID Controllers, which include modules and adapters, along with RAID Maintenance Free Backup Units (RMFBU), which infringe one or more claims of the '939 Patent. Such products include, for example, Intel's Raid Controller RMSP3AD160F and the RMFBU AXXRMFBU.

- 58. Intel makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States (or has made, used, sold, offered for sale, and/or imported into the United States) SSDs with power loss protection, which infringe one or more claims of the '939 Patent. Such SSDs include, for example, at least the Intel SSD DC S3500 Series; SSD DC S3700 Series; Optane<sup>TM</sup> Memory H10 with Solid State Storage; Optane<sup>TM</sup> SSD DC D4800X Series; SSD D3-S4510 Series; SSD D3-S4610 Series; SSD D5-P4320 Series; SSD D5-P4326 Series; SSD D5-P4420 Series; SSD DC P4510 Series; SSD DC P4511 Series; SSD DC P4610 Series; SSD DC P4618 Series; SSD DC P3500 Series; SSD DC P3500 Series; SSD DC P3600 Series; SSD DC P3608 Series; SSD DC P3700 Series; SSD DC P4500 Series; SSD DC P4501 Series; SSD DC P4600 Series; SSD DC P4608 Series; SSD DC S3320 Series; SSD DC S3510

Series; SSD DC S3520 Series; SSD DC S3610 Series; SSD DC S3710 Series; SSD DC S4500 Series; SSD DC S4600 Series; SSD E 5410s Series; and SSD E 7000s Series.

59. On information and belief, in December 2021, Solidigm, a subsidiary of SK hynix Inc., acquired a portion of Intel's business relating to NAND SSDs, and as a result of that acquisition, some of the SSD products identified above are no longer being sold by Intel but instead are now being sold by Solidigm. To the extent Intel is no longer selling such SSD products, Intel is still liable for its past infringing manufacture, use, sale, offer for sale, and/or importation into the United States of such SSDs.

### **Notice and Marking**

- 60. As set forth below, Intel has been on constructive and/or actual notice of the Asserted Patents.

- 61. BiTMICRO has complied with 35 U.S.C. § 287 with respect to the Asserted Patents.

- 62. The previous owner of the Asserted Patents, BNI, also complied with 35 U.S.C. § 287, and thereby provided notice to the public, including but not limited to Intel, of the Asserted Patents. Specifically, to the extent BNI made, offered for sale, sold, or imported into the United States products covered by the Asserted Patents, BNI marked substantially all of such products with those patent numbers and provided an internet address at which BNI posted information associating the patented products with their corresponding patent numbers in compliance with 35 U.S.C. § 287.

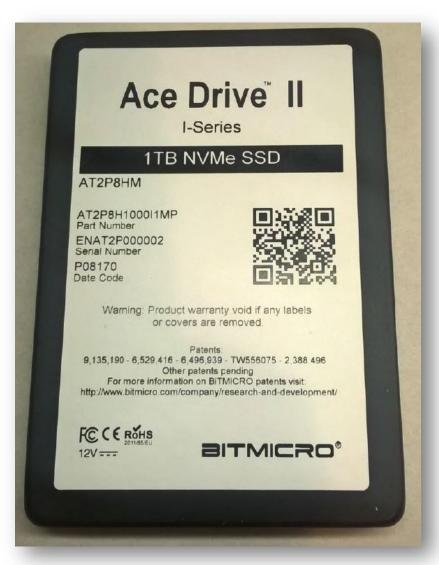

63. For example, BNI's Ace Drive II products, which BNI contended were covered by the '190 and '939 Patents, were sold by BNI with a label affixed on the products listing the '190 and '939 Patents, as well as an internet address at which BNI posted a listing of additional patents it contended were practiced by that product, as shown below:

64. BNI's other products similarly included product labels identifying specific patents by number and/or an internet address at which BNI posted a listing of the patents it contended were associated with each product, including but not limited to the '243, '190, '740, and '939 Patents.

- 65. BNI's product documentation, which was provided to customers and available to the general public, also identified by number specific patents that BNI contended were practiced by the products and included an internet address at which BNI posted a listing of other patents it contended were associated with the products, pursuant to 35 U.S.C. § 287.

- 66. On information and belief, BNI has never made, offered for sale, sold, or imported into the United States any products that are covered by the '084 or '694 Patents. Thus, there were no BNI products that would require marking of those patent numbers under 35 U.S.C. § 287.

- 67. BiTMICRO has not made, offered for sale, sold, or imported into the United States any products that are covered by any of the Asserted Patents. Thus, there are no BiTMICRO products that would require marking under 35 U.S.C. § 287.

- during the prosecution of other patents. For example, the '243 Patent has been cited in patents and/or applications by Apple, Mosaid, and other well-known industry participants. The '190 Patent has been cited in patents and/or applications by Western Digital, SanDisk, Micron, Huawei, Microsoft, and other well-known industry participants. The '740 Patent has been cited in patents and/or patent applications by Seagate and other well-known industry participants. The '084 and/or '694 Patents have been cited in patents and/or applications by NGD Systems, and other well-known industry participants. And the '939 Patent has been cited in patents and/or applications by Western Digital, Qualcomm, Samsung, SK hynix, HTC, IBM, Google, Avaya, and other well-known industry participants.

- 69. Indeed, the Asserted Patents have been used by the USPTO as a basis to reject patent applications filed by well-known industry participants under 35 U.S.C. § 102 and/or § 103. For example, the '243 Patent and its family members have served as the basis for § 102/103 rejections

at least ten times, including against IBM, Mosaid, Micron. The '190 Patent has served as the basis for § 102/103 rejections at least three times, including against SanDisk. The '740 Patent has served as the basis for § 102/103 rejections at least four times, including against Seagate and Samsung. The '084 Patent and/or '694 Patents have served as the basis for § 102/103 rejections at least twice, including against Samsung and SK hynix. And the '939 Patent has served as the basis for § 102/103 rejections at least ten times, including against Amazon, Marvell, and other well-known industry participants.

70. In addition, as set forth in greater detail below, Intel has had actual notice of the '243 and '190 Patents and the rest of the Asserted Patents since at least September 5, 2018 by virtue of its participation in a proceeding before the International Trade Commission involving those patents.

### **FIRST COUNT**

# (INFRINGEMENT OF U.S. PATENT NO. 7,826,243)

- 71. BiTMICRO incorporates by reference the allegations set forth in paragraphs 1-70 as though fully set forth herein.

- 72. On information and belief, Intel has directly infringed and continues to directly infringe one or more claims of the '243 Patent, including at least claim 1 of the '243 Patent, in the state of Texas, in this judicial district, and elsewhere in the United States by, among other things, making, using, selling, offering for sale, and/or importing into the United States products that embody one or more of the inventions claimed in the '243 Patent, including but not limited to the above-identified Lakefield Foveros product, and all reasonably similar products ("the '243 Accused Products"), in violation of 35 U.S.C. § 271(a).

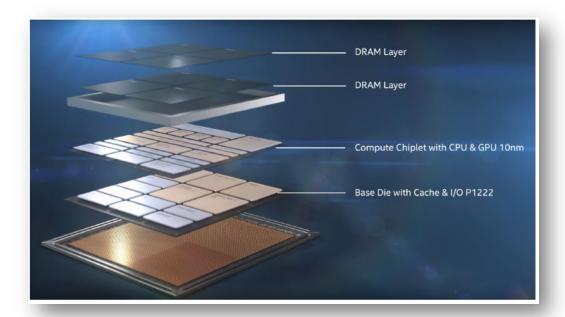

- 73. As an example, the '243 Accused Products, such as the Lakefield Foveros product, are "a stacked module comprising a plurality of modules." Specifically, the Lakefield Foveros

product consists of two layers of DRAM memory modules stacked on top of a compute module, which is in turn stacked on top of a base module, which is in turn stacked on top of a package module:

(Intel presentation, "Lakefield: Hybrid Cores in 3D Package," p. 13).1

$<sup>^{1}\</sup> Available\ at\ \underline{https://newsroom.intel.com/wp-content/uploads/sites/11/2019/08/Intel-\underline{Lakefield-HotChips-presentation.pdf.}$

(Intel video, "Intel Previews New Hybrid CPU Architecture with Foveros 3D Packaging").<sup>2</sup>

(Intel 2018 Architecture Day, Intel Architecture Directions presentation, p.19).<sup>3</sup>

<sup>&</sup>lt;sup>2</sup> Available at <a href="https://www.youtube.com/watch?v=-besHp8HLxo">https://www.youtube.com/watch?v=-besHp8HLxo</a>.

<sup>&</sup>lt;sup>3</sup> Available at <a href="https://wccftech.com/intel-architecture-day-2018-raja-koduris-commentary-and-vision-for-intel">https://wccftech.com/intel-architecture-day-2018-raja-koduris-commentary-and-vision-for-intel</a>.

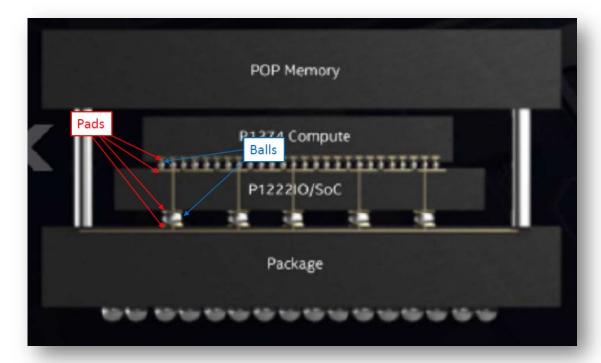

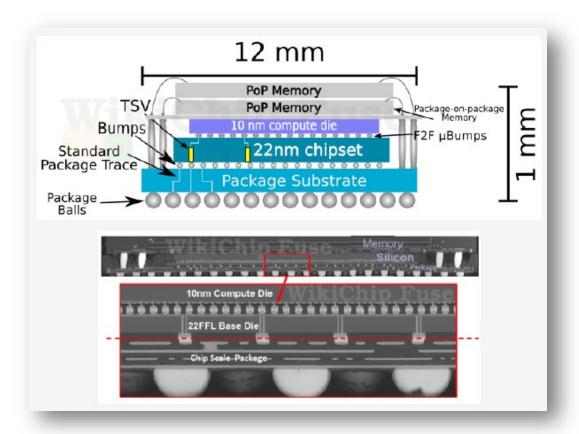

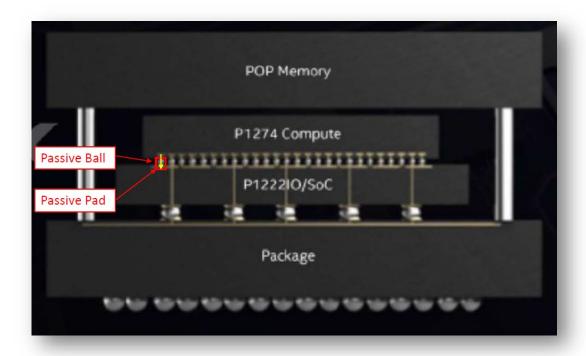

74. Multiple layers of the Lakefield Foveros product are connected by a ball and pad array, with a ball sandwiched between a top and bottom pad:

(Intel 2018 Architecture Day, Intel Architecture Directions presentation, p.19).<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> Available at <a href="https://wccftech.com/intel-architecture-day-2018-raja-koduris-commentary-and-vision-for-intel/">https://wccftech.com/intel-architecture-day-2018-raja-koduris-commentary-and-vision-for-intel/</a>.

(WikiChip article, "A Look at Intel Lakefield: A 3D-Stacked Single-ISA Heterogeneous Penta-Core SOC").<sup>5</sup>

<sup>&</sup>lt;sup>5</sup> Available at <a href="https://fuse.wikichip.org/news/3417/a-look-at-intel-lakefield-a-3d-stacked-single-isa-heterogeneous-penta-core-soc/">https://fuse.wikichip.org/news/3417/a-look-at-intel-lakefield-a-3d-stacked-single-isa-heterogeneous-penta-core-soc/</a>.

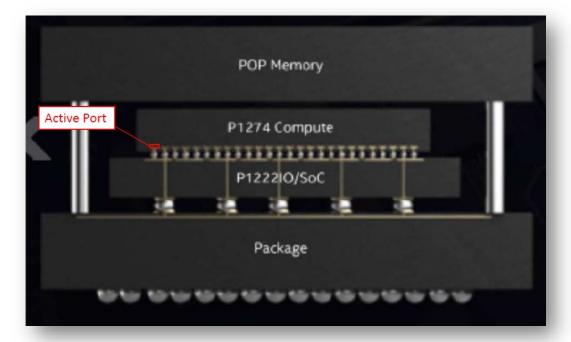

75. Intel's Lakefield Foveros product includes "one or more active ports for carrying one or more active signal." For example, the Lakefield Foveros product has pads that carry one or more active signals (and therefore constitute active ports) from the compute chip to the SoC chip:

76. The Lakefield Foveros product includes "one or more passive ports for passing through the one or more active signals." For example, as shown below, the Lakefield Foveros product has passive ports consisting of a passive ball on the bottom side of the compute chip and passive pad on the top of the base SoC chip. The passive ports pass through the active signals (*e.g.*, the signal depicted by the yellow arrow):

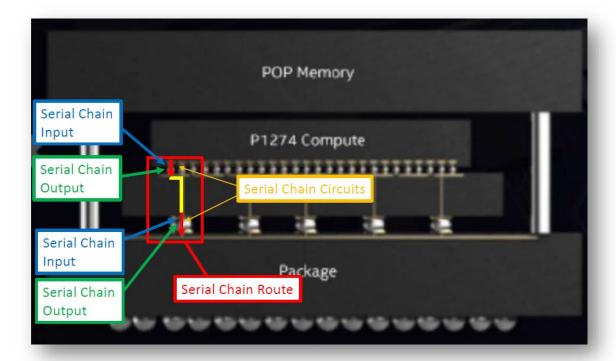

77. Intel's Lakefield Foveros product includes "a first serial chain route that includes at least one serial chain connection, the serial chain connection including: a serial chain circuit, a serial chain input, and serial chain output; said serial chain input coupled to said serial chain output through said serial chain circuit." For example, as shown in the figure below, the Lakefield Foveros product includes a serial chain circuit (the signal that couples the ball and pads between the compute module and the SoC module, identified by the top red arrow), a serial chain input (*e.g.*, an input for a signal on the pad on the bottom side of the compute module), and a serial chain output (*e.g.*, an output for a signal on the ball between the compute and SoC modules); said serial chain

input coupled to said serial chain output through said serial chain circuit (*e.g.*, the signal couples the serial chain input and the serial chain output). Thus, as depicted in the top red arrow, the serial chain circuit, serial chain input, and serial chain output form a serial chain connection.

78. Similarly, another serial chain connection exists between the SoC module and the package module, and is depicted in the bottom red arrow in the figure above. The bottom red arrow has corresponding components to the top red arrow (*e.g.*, a serial chain circuit, serial chain input, and serial chain output). The two serial chain connections designated by the top and bottom red arrows are connected to each other by a routing path (depicted in yellow above). The serial chain route includes both of the serial chain connections and their connection to each other through the routing path (*e.g.*, the route shown in the red rectangular label).

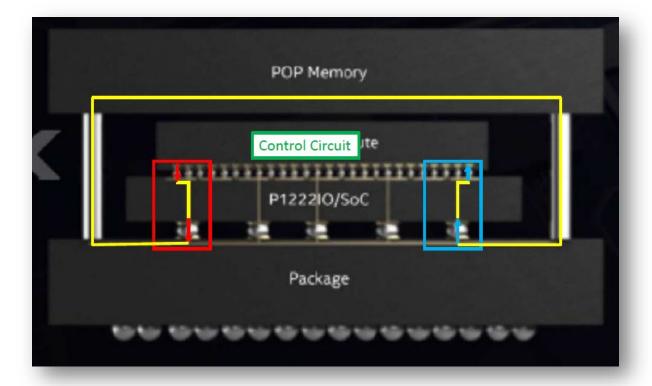

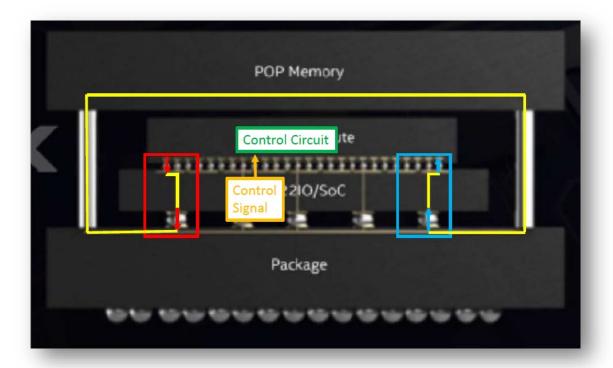

79. Intel's Lakefield Foveros product includes "a second serial chain route and a control circuit for enabling a routing path that connects the first serial chain route with the second serial chain route within an end module." For example, as shown in the figure below, the Lakefield Foveros product includes a second serial chain route, which includes at least two serial chain connections (*e.g.*, two serial chain connections depicted by the blue arrows). These serial chain connections include corresponding components to the serial chain connections described with respect to the first serial chain route. The second serial chain route follows the signal path depicted in the blue rectangle (*e.g.*, the signal path from the ball and pads between the package and SoC modules through the ball and pads between the SoC and compute modules). A routing path (depicted in yellow) through the PoP memory module, which constitutes an end module, connects

the first serial chain route with the second serial chain route. A control circuit within the compute module enables the routing path.

80. In Intel's Lakefield Foveros products, the "said control circuit is disposed to enable the routing path in response to a control input signal received from another module from the plurality of modules when the end module is coupled to the another module." For example, the POP memory module, compute module, SoC module, and package module are all coupled together through the stacking of the modules as discussed above. The control circuit in the compute module can enable the routing path in response to a control input received, for example, from the SoC module.

81. By making, using, offering for sale, and/or selling products in the United States and/or importing products into the United States, including but not limited to the '243 Accused Products, Intel has injured BiTMICRO and is liable to BiTMICRO for directly infringing one or more claims of the '243 Patent, including without limitation claim 1 pursuant to 35 U.S.C. § 271(a).

- 82. On information and belief, Intel has had knowledge of the '243 Patent since at least September 5, 2018, when BiTMICRO served a subpoena on Intel in connection with a proceeding before the International Trade Commission, *In the Matter of Certain Solid State Storage Drives, Stacked Electronics Components, and Products Containing Same*, Inv. No. 337-TA-1097 ("the ITC Action"). In the ITC Action, BiTMICRO alleged that various solid state computer drives ("SSDs") and electronic devices that incorporate stacked electronics components sold by Samsung Electronics, SK Hynix, and other electronic device manufacturers infringed four BiTMICRO patents, including the '243 Patent.

- 83. Intel responded to BiTMICRO's subpoena in the ITC Action by serving objections and responses to the subpoena, conferring with BiTMICRO's ITC counsel regarding the subpoena, and filing a motion in the ITC on September 14, 2018 for an extension of time to respond to the subpoena.

- 84. On information and belief, through its participation in the ITC Action as described above, Intel had knowledge of the '243 Patent and its relevance to the '243 Accused Products.

Despite this knowledge, Intel has continued to directly infringe one or more claims of the '243 Patent as described above. Thus, on information and belief, Intel's infringement of the '243 Patent has been willful.

- 85. On information and belief, Intel is also inducing and/or has induced infringement of one or more claims of the '243 Patent, including at least claim 1, as a result of, amongst other activities, instructing, encouraging, and directing its customers on the use of the '243 Accused Products in an infringing manner in violation of 35 U.S.C. § 271(b). Through its website, instructional guides, and manuals, Intel provides its customers with detailed explanations, instructions, and information on how to use and implement the '243 Accused Products which

demonstrate active steps taken to encourage direct infringement. (*See, e.g.*, Lakefield: Hybrid Cores in 3D Package).<sup>6</sup> On information and belief, Intel has had knowledge of the '243 Patent since at least September 5, 2018 as set forth above. Despite this knowledge, Intel has continued to engage in activities to encourage and assist its customers in the use of the '243 Accused Products. Thus, on information and belief, Intel (1) had actual knowledge of the patent; (2) knowingly induced its customers to infringe the patent; and (3) had specific intent to induce the patent infringement.

- 86. On information and belief, by using the '243 Accused Products as encouraged and assisted by Intel, Intel's customers have directly infringed and continue to directly infringe one or more claims of the '243 Patent, including at least claim 1. On information and belief, Intel knew or was willfully blind to the fact that its actions would induce its customers' direct infringement of the '243 Patent.

- 87. Intel's infringement of the '243 Patent has been and continues to be deliberate and willful, and this is therefore an exceptional case warranting an award of enhanced damages and attorneys' fees and costs pursuant to 35 U.S.C. §§ 284-285.

- 88. On information and belief, Intel will continue to infringe the '243 Patent unless enjoined by this Court.

- 89. As a result of Intel's infringement of the '243 Patent, BiTMICRO has suffered monetary damages, and seeks recovery, in an amount to be proven at trial, adequate to compensate for Intel's infringement, but in no event less than a reasonable royalty with interest and costs. Intel's infringement of BiTMICRO's rights under the '243 Patent will continue to damage BiTMICRO,

<sup>&</sup>lt;sup>6</sup> Available at <a href="https://newsroom.intel.com/wp-content/uploads/sites/11/2019/08/Intel-Lakefield-HotChips-presentation.pdf">https://newsroom.intel.com/wp-content/uploads/sites/11/2019/08/Intel-Lakefield-HotChips-presentation.pdf</a>.

causing irreparable harm for which there is no adequate remedy at law, unless enjoined by this Court.

## **SECOND COUNT**

# (INFRINGEMENT OF U.S. PATENT NO. 9,135,190)

- 90. BiTMICRO incorporates by reference the allegations set forth in paragraphs 1-89 as though fully set forth herein.

- 91. On information and belief, Intel has directly infringed and continues to directly infringe one or more claims of the '190 Patent, including at least claim 59 of the '190 Patent, in the state of Texas, in this judicial district, and elsewhere in the United States by, among other things, making, using, selling, offering for sale, and/or importing into the United States products that embody one or more of the inventions claimed in the '190 Patent, including but not limited to the above-identified SSDs with SLC caching and Optane Persistent Memory products, and all reasonably similar products ("the '190 Accused Products"), in violation of 35 U.S.C. § 271(a).

- 92. As an example, the 660p Series SSDs include "a memory controller." Specifically, the 660p Series SSDs includes a memory controller for handling read and write operations on the NAND memory cells on the drive. "Intel® SSD 660p, built using Intel® QLC NAND technology, enables 4-bits of storage per cell. The QLC NAND allows 33% more storage in the same area compared to TLC NAND. Compared to TLC NAND cell, the QLC NAND cell has a higher write and read latency. To mitigate the impact of higher latency of the QLC NAND in Intel® SSD 660p, Intel has designed and implemented an innovative SLC cache, which is variable based on available

unused capacity on the SSD, that delivers faster sequential and random data writes." (See Intel Solid State Drive 660p Series Evaluation Guide, at 6).<sup>7</sup>

93. The 660p Series SSDs include "an interface controller coupled to a memory device interface and an input/output (IO) device interface." For example, the 660p Series SSDs include an SMI 2263 controller chip that serves as an interface controller:

| Specifications        |                         |                         |                         |  |

|-----------------------|-------------------------|-------------------------|-------------------------|--|

| Product               | Intel SSD 660P 512GB    | Intel SSD 660P 1TB      | Intel SSD 660P 2TB      |  |

| Pricing               | \$64                    | \$97                    | \$204                   |  |

| Capacity (User / Raw) | 512GB / 512GB           | 1024GB / 1024GB         | 2048GB / 2048GB         |  |

| Form Factor           | M.2 2280 (single-sided) | M.2 2280 (single-sided) | M.2 2280 (single-sided) |  |

| Interface / Protocol  | PCIe 3.0 x4 / NVMe 1.3  | PCIe 3.0 x4 / NVMe 1.3  | PCIe 3.0 x4 / NVMe 1.3  |  |

| Controller            | SMI 2263                | SMI 2263                | SMI 2263                |  |

| DRAM                  | NANYA DDR3L             | NANYA DDR3L             | NANYA DDR3L             |  |

| Memory                | IMFT 64L 3D QLC         | IMFT 64L 3D QLC         | IMFT 64L 3D QLC         |  |

| Sequential Read       | 1,500 MB/s              | 1,800 MB/s              | 1,800 MB/s              |  |

| Sequential Write      | 1,000 MB/s              | 1,800 MB/s              | 1,800 MB/s              |  |

|                       | 90,000 IOPS             | 150,000 IOPS            | 220,000 IOPS            |  |

| Random Read           | 90,000 1023             | 130,000 1013            | 220,000 101 3           |  |

<sup>&</sup>lt;sup>7</sup> Available at <a href="https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf">https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf</a>.

("Intel SSD 660p 2TB Review: a QLC Bargain (Update)").8

<sup>&</sup>lt;sup>8</sup> Available at <a href="https://www.tomshardware.com/reviews/intel-ssd-660p-qlc-nvme,5719.html">https://www.tomshardware.com/reviews/intel-ssd-660p-qlc-nvme,5719.html</a>.

94. The SMI 2263 controller chip is connected to at least one memory bus, which serves as a memory device interface. The controller chip is also connected to a PCIe interface, which serves as an input/output interface with a computing device:

| Product               | Intel SSD 660P 512GB    | Intel SSD 660P 1TB      | Intel SSD 660P 2TB      |

|-----------------------|-------------------------|-------------------------|-------------------------|

| Pricing               | \$64                    | \$97                    | \$204                   |

| Capacity (User / Raw) | 512GB / 512GB           | 1024GB / 1024GB         | 2048GB / 2048GB         |

| Form Factor           | M.2 2280 (single-sided) | M.2 2280 (single-sided) | M.2 2280 (single-sided) |

| Interface / Protocol  | PCIe 3.0 x4 / NVMe 1.3  | PCIe 3.0 x4 / NVMe 1.3  | PCIe 3.0 x4 / NVMe 1.3  |

| Controller            | SMI 2263                | SMI 2263                | SMI 2263                |

| DRAM                  | NANYA DDR3L             | NANYA DDR3L             | NANYA DDR3L             |

| Memory                | IMFT 64L 3D QLC         | IMFT 64L 3D QLC         | IMFT 64L 3D QLC         |

| Sequential Read       | 1,500 MB/s              | 1,800 MB/s              | 1,800 MB/s              |

| Sequential Write      | 1,000 MB/s              | 1,800 MB/s              | 1,800 MB/s              |

| Random Read           | 90,000 IOPS             | 150,000 IOPS            | 220,000 IOPS            |

| Random Write          | 220,000 IOPS            | 220,000 IOPS            | 220,000 IOPS            |

("Intel SSD 660p 2TB Review: a QLC Bargain (Update)").9

95. The 660p Series SSDs include "a memory store." For example, the 660 Series SSDs include 64-layer QLC NAND memory, which constitutes a memory store. As advertised by Intel, "Intel® SSD 660p, built using Intel® QLC NAND technology, enables 4-bits of storage per cell." (*See* Intel Solid State Drive 660p Series Evaluation Guide, at 6).

<sup>&</sup>lt;sup>9</sup> Available at <a href="https://www.tomshardware.com/reviews/intel-ssd-660p-qlc-nvme,5719.html">https://www.tomshardware.com/reviews/intel-ssd-660p-qlc-nvme,5719.html</a>.

- 96. In the 660p Series SSDs, "the memory device interface is directly coupled to the memory store." For example, the memory bus connected to the controller chip is directly coupled to the QLC NAND memory store, thereby enabling the controller to handle read and write operations to the memory store.

- 97. In the 660 Series SSDs, "said interface controller [is] disposed to perform a memory transaction by addressing a first memory location in the memory store." For example, in the 660 Series SSDs, a portion of the QLC NAND memory store is reserved to act as an SLC cache. Data can be written to the SLC cache at a faster rate than to other portions of the QLC NAND memory store. As advertised by Intel, "[t]o mitigate the impact of higher latency of the QLC NAND in Intel® SSD 660p, Intel has designed and implemented an innovative SLC cache, which is variable based on available unused capacity on the SSD, that delivers faster sequential and random data writes. . . . Data writes from the host will be directed through the variable size, high speed SLC cache and offer faster data writes through the full span of the SLC cache. When the SLC cache is reaching its full capacity, the drive firmware moves the contents of the SLC cache into the available QLC cells." (See Intel Solid State Drive 660p Series Evaluation Guide, at 6). For write operations to the SLC cache, the controller chip performs a memory transaction by addressing a first memory location within the SLC cache.

- 98. In the 660 Series SSDs, "said first memory location and a second memory location [are] respectively associated with a first device profile and a second device profile." For example, a second memory location within the QLC NAND memory store is a QLC cell that is not a part of the SLC cache. The first memory location and second memory location are associated with a first

<sup>&</sup>lt;sup>10</sup> Available at <a href="https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf">https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf</a>.

device profile and a second device profile, respectively, that define how data is to be stored in those locations.

- 99. In the 660 Series SSDs, "said first device profile is optimal for a data type subject to the memory transaction, wherein said data type comprises one of a random data type or a sequential data type." For example, as advertised by Intel, the SLC cache "delivers faster sequential and random data writes." (*See* Intel Solid State Drive 660p Series Evaluation Guide, at 6).<sup>11</sup>

- 100. In the 660 Series SSDs, "said interface controller identifies command details for causing the memory transaction to be performed, wherein said command details comprising the first memory device." For example, for memory transactions with the first memory device such as writing data to the SLC cache, the controller chip identifies command details for causing the memory transaction to be performed in the first memory device.

- 101. In the 660 Series SSDs, "said device profile represent[s] a first set of attributes of said first memory location, and said second device profile represent[s] a second set of attributes of said second memory location, and a difference exists between said first and second device profiles." For example, the first device profile (e.g., the profile for the SLC cache) represents a first set of attributes (e.g., data size, memory protocol, device type) associated with the first memory location (e.g., a location within the SLC cache). The second device profile (e.g., the profile for the non-cache portion of the QLC NAND memory store) represents a second set of attributes (e.g., data size, memory protocol, device type) associated with the second memory location (e.g., a location within the non-cache portion of the QLC NAND memory store). The first and second device profiles are different because the SLC cache has attributes associated with a write protocol of one

<sup>&</sup>lt;sup>11</sup> Available at <a href="https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf">https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf</a>.

bit per cell, whereas the non-cache portion of the QLC NAND memory store has attributes associated with a write protocol of four bits per cell.

- 102. In the 660 Series SSDs, "said interface controller obtain[s] the first set of attributes after identifying the command details; and said addressing of said first memory location includes using said attributes from said first device profile." For example, after identifying command details specifying that data is to be written to the SLC cache, the controller chip obtains the first set of attributes (*e.g.*, data size, memory protocol, device type) associated with the memory location in the SLC cache.

- 103. In the 660 Series SSDs, "said addressing of said first memory location includes selecting a transfer size for the memory transaction, wherein the transfer size is a function of a data size of the memory transaction and the first set of attributes." As advertised by Intel, "[w]hen the SLC cache is reaching its full capacity, the drive firmware moves the contents of the SLC cache into the available QLC cells. The firmware also has an intelligent algorithm to opportunistically move the data from SLC cache to QLC cells during the drive idles. This feature allows the user to experience a smoother and refreshed experience from the SSD. The variable SLC adjusts in size bidirectionally based on the available capacity of drive." (See Intel Solid State Drive 660p Series Evaluation Guide, at 6). Thus, for example, after receiving a write transaction command, the controller chip obtains the attributes of the SLC cache profile and determines whether there is sufficient capacity within the SLC cache to write the data to the cache. The controller will select a transfer size to the SLC cache based on an analysis of the size of the data to be written, the remaining memory capacity within the SLC cache, and the attributes of the SLC cache profile.

<sup>&</sup>lt;sup>12</sup> Available at <a href="https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf">https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/consumer-ssds/Intel\_SSD\_660p\_EvaluationGuide337971.pdf</a>.

- 104. As another example, Intel's Optane Persistent Memory product includes "a memory controller." Specifically, the Optane Persistent Memory product includes a memory controller for handling read and write operations on the DRAM memory and persistent memory modules in the product. The persistent memory modules have properties similar to flash memory. As advertised by Intel, for example, "NVDIMM uses a dual in-line memory module (DIMM) package compatible with a standard DIMM slot, and communicates through a standard double data rate (DDR) bus. Considering the fact that it is nonvolatile and compatible with a traditional dynamic random-access memory (DRAM) interface, it is also called persistent memory (PMEM). . . . NVDIMM-P combines the features of DRAM and flash, supporting both block addressing and traditional DRAM-like byte addressing, with a possible terabyte capacity, like NAND flash. . . . Intel Corporation released Intel Optane DC persistent memory in April 2019. It can be seen as an instance of an NVDIMM-P implementation." (See Enabling Persistent Memory in the Storage Performance Development Kit (SPDK)). <sup>13</sup>

- 105. The Optane Persistent Memory product includes "an interface controller coupled to a memory device interface and an input/output (IO) device interface." For example, the Optane Persistent Memory product includes a controller that is connected to at least one memory bus, which serves as an interface with a memory device such as DRAM memory or persistent memory. The controller is also connected to an input/output interface which is designed to connect to a computing device via a standard DIMM slot.

<sup>&</sup>lt;sup>13</sup> Available at <a href="https://www.intel.com/content/www/us/en/developer/articles/technical">https://www.intel.com/content/www/us/en/developer/articles/technical</a> /enabling-persistent-memory-in-the-storage-performance-development-kit-spdk.html.

(Intel Optane DC Persistent Memory Technical Video). 14

<sup>&</sup>lt;sup>14</sup> Available at <a href="https://www.intel.com/content/www/us/en/design/products-and-solutions/memory-and-storage/pmem/optane-dc-persistent-technical-video.html">https://www.intel.com/content/www/us/en/design/products-and-solutions/memory-and-storage/pmem/optane-dc-persistent-technical-video.html</a>.

("Enabling Persistent Memory in the Storage Performance Development Kit (SPDK)"). 15

106. The Optane Persistent Memory product includes "a memory store." For example, the Optane Persistent Memory product includes both DRAM memory and persistent memory modules, which separately or in combination are a memory store:

<sup>&</sup>lt;sup>15</sup> Available at <a href="https://www.intel.com/content/www/us/en/developer/articles/technical/enabling-persistent-memory-in-the-storage-performance-development-kit-spdk.html">https://www.intel.com/content/www/us/en/developer/articles/technical/enabling-persistent-memory-in-the-storage-performance-development-kit-spdk.html</a>.

(Intel Optane DC Persistent Memory Technical Video). 16

<sup>&</sup>lt;sup>16</sup> Available at <a href="https://www.intel.com/content/www/us/en/design/products-and-solutions/memory-and-storage/pmem/optane-dc-persistent-technical-video.html">https://www.intel.com/content/www/us/en/design/products-and-solutions/memory-and-storage/pmem/optane-dc-persistent-technical-video.html</a>.

- 107. In the Optane Persistent Memory product, "the memory device interface is directly coupled to the memory store." For example, in the Intel Optane Persistent Memory product, the memory bus connected to the controller is directly coupled to the DRAM memory and persistent memory, thereby enabling the controller to handle read and write operations to the DRAM memory and persistent memory.

- 108. In the Optane Persistent Memory product, "said interface controller [is] disposed to perform a memory transaction by addressing a first memory location in the memory store." For example, a first memory location in the memory store is a location within the DRAM memory. The controller performs a memory transaction (*e.g.*, a write operation) by addressing a first memory location (*e.g.*, a location within the DRAM memory) in the memory store.

- 109. In the Optane Persistent Memory product, "said first memory location and a second memory location [are] respectively associated with a first device profile and a second device profile." For example, in addition to the first memory location within the DRAM memory, the Intel Optane Persistent Memory product also includes a second memory location within the persistent memory. The first memory location (*e.g.*, a location within the DRAM memory) is associated with a first device profile (*e.g.*, the profile for the DRAM memory). Similarly, a second memory location (*e.g.*, a location within the persistent memory) is associated with a second device profile (*e.g.*, the profile for the persistent memory). Separate profiles exist for the DRAM memory and the persistent memory in the Intel Optane Persistent Memory product. This is due to the fact that the Optane Persistent Memory product uses a different write protocol when writing to the DRAM memory than it does when writing to the persistent memory.

- 110. For example, as advertised by Intel, as an NVDIMM implementation the Optane Persistent Memory product "combines the features of DRAM and flash, supporting both block

addressing and traditional DRAM-like byte addressing, with a possible terabyte capacity, like NAND flash. . . . " ("Enabling Persistent Memory in the Storage Performance Development Kit (SPDK)"). 17 As also advertised by Intel, "Intel Optane PMem 200 series has multiple operating modes: Memory Mode delivers large memory capacity without application changes and with performance close to that of DRAM, depending on the workload. In Memory Mode, the CPU memory controller sees all of the Intel Optane PMem 200 series as volatile system memory (without persistence). The CPU uses DRAM as a fast cache to the Intel Optane PMem. . . . App Direct Mode enables large memory capacity and data persistence for software to access DRAM and persistent memory as two separate pools of memory. . . . In App Direct Mode, data is encrypted using a key stored on the module in a security metadata region, which can only be accessed by the Intel Optane PMem 200 series controller." (Data Center Intel Optane Persistent Memory 200 Series Product Brief). 18 Different device profiles are therefore necessary in order for the Intel Optane Persistent Memory to be able to know which protocol to use with the DRAM and persistent memory devices.

111. In the Optane Persistent Memory product, "said first device profile is optimal for a data type subject to the memory transaction, wherein said data type comprises one of a random data type or a sequential data type." For example, as advertised by Intel, as an NVDIMM implementation the Optane Persistent Memory product includes "memory that is nonvolatile and

<sup>&</sup>lt;sup>17</sup> Available at <a href="https://www.intel.com/content/www/us/en/developer/articles/technical/enabling-persistent-memory-in-the-storage-performance-development-kit-spdk.html">https://www.intel.com/content/www/us/en/developer/articles/technical/enabling-persistent-memory-in-the-storage-performance-development-kit-spdk.html</a>.

<sup>&</sup>lt;sup>18</sup> Available at <a href="https://www.intel.com/content/dam/www/public/us/en/documents/product-briefs/optane-persistent-memory-200-series-brief.pdf">https://www.intel.com/content/dam/www/public/us/en/documents/product-briefs/optane-persistent-memory-200-series-brief.pdf</a>.

allows for random access." ("Enabling Persistent Memory in the Storage Performance Development Kit (SPDK)"). 19

- 112. In the Optane Persistent Memory product, "said interface controller identifies command details for causing the memory transaction to be performed, wherein said command details comprising the first memory device." For example, for memory transactions with the first memory device (*e.g.*, the DRAM memory), the controller identifies command details for causing the memory transaction to be performed in the first memory device.

- 113. In the Optane Persistent Memory product, "said device profile represent[s] a first set of attributes of said first memory location, and said second device profile represent[s] a second set of attributes of said second memory location, and a difference exists between said first and second device profiles." For example, the first device profile (e.g., the profile for the DRAM memory) represents a first set of attributes (e.g., data size, memory protocol, device type, operating mode) associated with the first memory location (e.g., a location within the DRAM memory). The second device profile (e.g., the profile for the persistent memory) represents a second set of attributes (e.g., data size, memory protocol, device type, operating mode) associated with the second memory location (e.g., a location within the persistent memory). The first and second device profiles are different because DRAM and persistent memory are different types of memory with different parameters for reading and writing data.

- 114. In the Optane Persistent Memory product, "said interface controller obtain[s] the first set of attributes after identifying the command details; and said addressing of said first memory location includes using said attributes from said first device profile." For example, after identifying

<sup>&</sup>lt;sup>19</sup> Available at <a href="https://www.intel.com/content/www/us/en/developer/articles/technical/enabling-persistent-memory-in-the-storage-performance-development-kit-spdk.html">https://www.intel.com/content/www/us/en/developer/articles/technical/enabling-persistent-memory-in-the-storage-performance-development-kit-spdk.html</a>.

the command details specifying that data is to be written to the DRAM memory, the controller obtains the first set of attributes (*e.g.*, data size, memory protocol, device type) associated with the memory location in the DRAM memory.

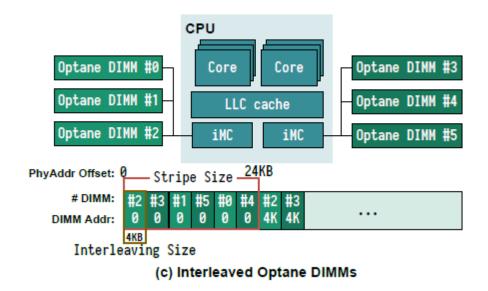

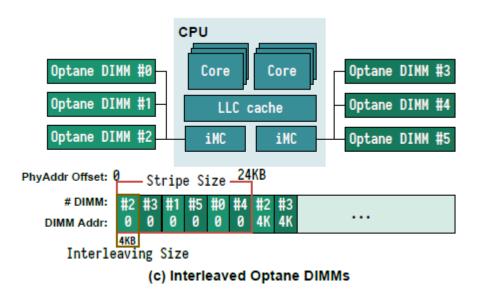

In the Optane Persistent Memory product, "said addressing of said first memory 115. location includes selecting a transfer size for the memory transaction, wherein the transfer size is a function of a data size of the memory transaction and the first set of attributes." For example, after receiving a write transaction command, the controller obtains the mode attributes and/or available data attributes associated with the first and second device profiles. As advertised by Intel, "[i]n Memory Mode, the DRAM acts as a cache for the most frequently accessed data, while the Intel Optane DC persistent memory provides large memory capacity. . . . In App Direct Mode, applications and the Operating System are explicitly aware there are two types of direct load/store memory in the platform and can direct which type of data read or write is suitable for DRAM or Intel Optane DC persistent memory. Operations that require the lowest latency and don't need permanent data storage can be executed on DRAM, such as database 'scratch pads'. Data that needs to be made persistent or structures that are very large can be routed to the Intel Optane DC persistent memory." (Intel Optane DC Persistent Memory Quick Start Guide, Revision 1.1 (June 2020), p. 3). <sup>20</sup> The Intel Optane Persistent Memory product can therefore receive a data size of the memory transaction from the write transaction command and select a transfer size to the DRAM memory based on the mode and available data attributes associated with the DRAM memory and persistent memory.

<sup>&</sup>lt;sup>20</sup> Available at <a href="https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/data-center-persistent-mem/Intel-Optane-DC-Persistent-Memory-Quick-Start-Guide.pdf">https://www.intel.com/content/dam/support/us/en/documents/memory-and-storage/data-center-persistent-mem/Intel-Optane-DC-Persistent-Memory-Quick-Start-Guide.pdf</a>.

- 116. By making, using, offering for sale, and/or selling products in the United States and/or importing products into the United States, including but not limited to the '190 Accused Products, Intel has injured BiTMICRO and is liable to BiTMICRO for directly infringing one or more claims of the '190 Patent, including without limitation claim 59 pursuant to 35 U.S.C. § 271(a).