Alexander P. McLaughlin (ISB No. 7977) Jason J. Blakley (ISB No. 9497) Givens Pursley LLP 601 West Bannock Street P.O. Box 2720 Boise, ID 83702 Phone: (208) 388-1200 Fax: (208) 388-1300 alexmclaughlin@givenspursley.com jasonblakley@givenspursley.com 16433341 [16428.4]

Attorneys for Plaintiff

## IN THE UNITED STATES DISTRICT COURT

## FOR THE DISTRICT OF IDAHO

BELL SEMICONDUCTOR, LLC

Plaintiff,

v.

MICRON TECHNOLOGY, INC.

Defendant.

Case No. \_\_\_\_\_

ORIGINAL COMPLAINT JURY TRIAL DEMANDED

Plaintiff Bell Semiconductor, LLC ("Bell Semic" or "Plaintiff") brings this Complaint against Defendant Micron Technology, Inc. ("Micron") for infringement of U.S. Patent No. 7,231,626 ("the '626 patent"). Plaintiff, on personal knowledge of its own acts, and on information and belief as to all others based on investigation, alleges as follows:

## **SUMMARY OF THE ACTION**

1. This is a patent infringement suit relating to Micron's unauthorized and unlicensed use of the '626 patent. The circuit design methodologies claimed in the '626 patent are used by Micron in the production of one or more of its semiconductor chips, including at least the

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 2 of 95

Micron 2200 MTFDHBA256TCK-1AS1AABYY 256GB NVMe PCIe3.0x4 TLC M.2 22x80mm SSD ("Micron Accused Product").

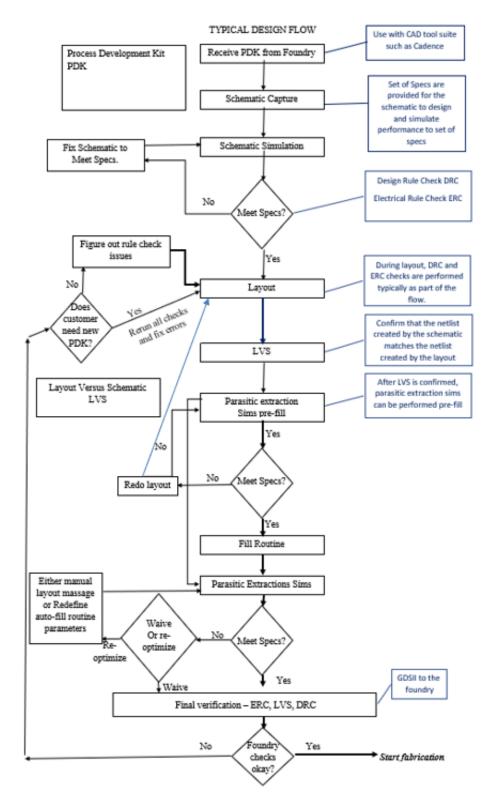

2. Traditionally, the process flow for IC design is highly linear, with each phase of the design process depending on the previous steps. Accordingly, when revisions to portions of the physical design are made, as typically happens numerous times during the design process, all the subsequent steps typically need to be redone in their entirety for at least the layer, if not the entire device. This is because regardless of the size or extent of the revision to the physical design, the changes must be merged into a much larger integrated circuit design and then the remaining steps of the design process flow re-run.

3. Before the inventions claimed in the '626 patent, the typical turnaround time for implementing a change to the physical design for cutting edge devices was approximately one week regardless of the size of the change. This is extremely inefficient in most instances where the change relates to only a small fraction of the overall design. See Ex. A at 3:16–18 & Fig. 1.

4. The '626 patent's inventors solved this problem by defining a window that encloses a change specified by the revision to physical design. The window defines an area that is less than the area of the entire circuit design. Only the nets within that window are routed pursuant to the revision, leaving the remaining nets in the design unaffected. Then, the results of that incremental routing are inserted into a copy of the original IC design to produce a revised IC design that effects the physical design change without needing to redo the entire process flow.

5. Semiconductor devices include different kinds of materials to function as intended. For example, these devices typically include both metal (*i.e.*, conductor) and insulator materials, which are deposited or otherwise processed sequentially in layers to form the final device. These layers—and the interconnects and components formed within them—have gotten much smaller

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 3 of 95

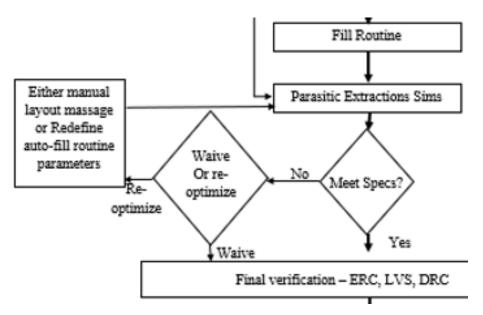

over time, increasing the performance of these devices dramatically. As a result, it has become even more important to keep the layers planar as the device is being built because defects and warpage can cause fabrication issues and malfunctioning of the device. Manufacturers use a process called Chemical Mechanical Planarization/Polishing ("CMP") to smooth out the surface of the device to prepare the device for further processing, such as deposition of another layer. This allows subsequent layers to be built and connected more easily with fewer opportunities for short circuits or other errors that render the device defective. CMP functions best when there is a certain density and variance of the same material on the surface of the chip. This is because different materials will be "polished" away at different rates, leading to erosion or dishing on the surface. To reduce this problem "dummy" material, also known as "dummy fill," is typically inserted into low-density regions of the device to increase the overall uniformity of the structures on the surface of the layer and reduce the density variability across the surface of the device. However, dummy fill can increase capacitance if it is placed too close to signal wires, which slows the transmission speed of signals and degrades the overall performance of the device.

6. Bell Semic brings this action to put a stop to Micron's unauthorized and unlicensed use of the inventions claimed in the '626 patent.

#### THE PARTIES

7. Plaintiff Bell Semic is a limited liability company organized under the laws of the State of Delaware with a place of business at One West Broad Street, Suite 901, Bethlehem, PA 18018.

8. Bell Semic stems from a long pedigree that began at Bell Labs. Bell Labs sprung out of the Bell System as a research and development laboratory, and eventually became known as one of America's greatest technology incubators. Bell Labs employees invented the transistor

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 4 of 95

in 1947 in Murray Hill, New Jersey. It was widely considered one of the most important technological breakthroughs of the time, earning the inventors the Nobel Prize in Physics. Bell Labs made the first commercial transistors at a plant in Allentown, Pennsylvania. For decades, Bell Labs licensed its transistor patents to companies throughout the world, creating a technological boom that led to the use of transistors in the semiconductor devices prevalent in most electronic devices today.

9. Bell Semic, a successor to Bell Labs' pioneering efforts, owns over 1,900 worldwide patents and applications, approximately 1,500 of which are active United States patents. This patent portfolio of semiconductor–related inventions was developed over many years by some of the world's leading semiconductor companies, including Bell Labs, Lucent Technologies, Agere Systems, and LSI Logic and LSI Corporation ("LSI"). This portfolio reflects technology that underlies many important innovations in the development of semiconductors and integrated circuits for high–tech products, including smartphones, computers, wearables, digital signal processors, IoT devices, automobiles, broadband carrier access, switches, network processors, and wireless connectors.

10. The principals of Bell Semic all worked at Bell Labs' Allentown facility, and have continued the rich tradition of innovating, licensing, and helping the industry at large since those early days at Bell Labs. For example, Bell Semic's CTO was a LSI Fellow and Broadcom Fellow. He is known throughout the world as an innovator with more than 300 patents to his name, and he has a sterling reputation for helping semiconductor fabs improve their efficiency. Bell Semic's CEO took a brief hiatus from the semiconductor world to work with Nortel Networks in the telecom industry during its bankruptcy. His efforts saved the pensions of tens of thousands of Nortel retirees and employees. In addition, several Bell Semic executives previously served as

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 5 of 95

engineers at many of these companies and were personally involved in creating the ideas claimed throughout Bell Semic's extensive patent portfolio.

11. On information and belief, Micron has its principal place of business and headquarters at 8000 South Federal Way, Post Office Box 6, Boise, ID 83707.

12. On information and belief, Micron develops, designs, and/or manufactures products in the United States, including in this District, according to the '626 patented processes/methodologies; and/or uses the '626 patented processes/methodologies in the United States, including in this District, to make products; and/or distributes, markets, sells, or offers to sell in the United States and/or imports products into the United States, including in this District, that were manufactured or otherwise produced using the patented process. Additionally, Micron introduces those products into the stream of commerce knowing that they will be sold and/or used in this District and elsewhere in the United States.

#### JURISDICTION AND VENUE

13. This is an action for patent infringement arising under the Patent Laws of the United States, Title 35 of the United States Code. Accordingly, this Court has subject matter jurisdiction under 28 U.S.C. §§ 1331 and 1338(a).

14. This Court has personal jurisdiction over Micron under the laws of the State of Idaho, due at least to its substantial business in Idaho and in this District. Micron has purposefully and voluntarily availed itself of the privileges of conducting business in the United States, in the State of Idaho, and in this District by continuously and systematically placing goods into the stream of commerce through an established distribution channel with the expectation that they will be purchased by consumers in this District. In the State of Idaho and in this District, Micron, directly or through intermediaries: (i) performs at least a portion of the infringements alleged herein; (ii) develops, designs, and/or manufactures products according to the '626 patented

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 6 of 95

process/methodology; (iii) distributes, markets, sells, or offers to sell products formed according to the '626 patented process/methodology; and/or (iv) imports products formed according to the '626 patented processes/methodologies.

15. On information and belief, venue is proper in this Court pursuant to 28 U.S.C. §§ 1391 and 1400 because Micron has committed, and continues to commit, acts of infringement in this District and has a regular and established place of business in this District. For example, Micron maintains a regular and established place of business at its headquarters, which is located in the District at 8000 S. Federal Way, Boise, Idaho. Micron current employs about 3,000 engineers in Idaho. See Search Results for Current Micron Employees, LinkedIn (available at https://www.linkedin.com/search/results/people/?currentCompany=%5B%223690%22%5D&ge oUrn=%5B%22102560739%22%5D&keywords=engineer&origin=FACETED\_SEARCH&sid= -Da) (last visited October 4, 2022). In addition, Micron is currently advertising 471 jobs in the Idaho Jobs Technology, (available Boise, area. See at Micron Micron at https://micron.eightfold.ai/careers?location=Boise%2C%20Idaho%2C%20United%20States%20 of%20America&pid=7598505&domain=micron.com&triggerGoButton=false&triggerGoButton =true) (last visited October 4, 2022). These positions include those that relate to the '626 patented technologies, such as positions for a Principal Design Engineer, Senior Design Engineer, Systems Design/Architect Engineer, and Senior Design Verification Engineer. Id.

16. Venue is also convenient in this District. This is at least true because of this District's close ties to this case—including the technology, relevant witnesses, and sources of proof noted above—and its ability to quickly and efficiently move this case to resolution.

17. On information and belief, Bell Semic's causes of action arise directly from Micron's circuit design work and other activities in this District. Moreover, on information and

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 7 of 95

belief, Micron has derived substantial revenues from its infringing acts occurring within the State of Micron and within this District.

#### <u>U.S. PATENT NO. 7,231,626</u>

18. Bell Semiconductor owns by assignment the entire right, title, and interest in the '626 patent, entitled "Method Of Implementing An Engineering Change Order In An Integrated Circuit Design By Windows."

19. A true and correct copy of the '626 patent is attached as Exhibit A.

20. The '626 patent issued to inventors Jason K. Hoff, Viswanathan Lakshmanan, Michael Josephides, Daniel W. Prevedel, Richard D. Blinne, and Johathan P. Kuppinger.

21. The application that resulted in issuance of the '626 patent, United States Patent Application No. 11/015,123, was filed December 17, 2004. It issued on June 12, 2007 and expires on July 26, 2025.

22. The '626 patent generally relates to "methods of implementing an engineering change order (ECO) in an integrated circuit design." Ex. A at 1:1–13.

23. The background section of the '626 patent identifies the shortcomings of the prior art. More specifically, the specification describes that the prior circuit design methodology was disadvantageous because "[i]n previous methods for implementing an engineering change order (ECO) request in an integrated circuit design, design tools are run for the entire integrated circuit design, even though the engineering change order typically is only a small fraction of the size of the integrated circuit design" Ex. A at 2:15–19.

24. The '626 patent elaborates that because "cell placement, routing, design rule check validation, and timing closure run times typically scale with the size of the entire integrated circuit design," Ex. A at 2:20–22, this produced a "typical turnaround time" of "about one week regardless

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 8 of 95

of the size of the engineering change order. . . . because although the engineering change order may only have a size of a few cells, it must be merged with an integrated circuit design that typically has a much greater size." *Id.* at 2:37–44. Certain of these steps "may be especially time consuming and resource intensive." *Id.* at 3:16–17.

25. The inventions disclosed in the '626 patent provide many advantages over the prior art. In particular, they provide a simple and efficient method for ensuring that revisions to the physical design of the IC do not unduly delay the completion of the design process. As the '626 patent explains, "significant savings in the resources required to perform routing, design rule check verification, net delay calculation, and parasitic extraction may be realized by creating windows in the integrated circuit design that include only the incremental changes to the overall integrated circuit design." Ex. A at 3:19–23.

26. As mentioned above, this is very beneficial because it substantially reduces the run time of the routing tools and related follow-on steps of the layout portion of the design process flow (such as calculation of net delay, design rule check, and parasitic extraction). Thus, it shortens the overall design timeline, and avoids cost overruns and delays, making it less costly to make changes later in the design process or more often. *See id*.

27. Given the aforementioned increased complexity of circuit designs and the corresponding delays from design changes, these efficiency gains have become more and more important in completing the design process without affecting time-to-market. These significant advantages are achieved through the use of the patented inventions and thus the '626 patent presents significant commercial value for chip designers.

28. In light of the drawbacks of the prior art, the '626 patent's inventors recognized the need for a circuit design methodology in which the time required to implement an ECO "depend[s]

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 9 of 95

on the number of net changes in the [ECO] rather than on the total number of nets in the entire integrated circuit design." Ex. A at 2:51–53. The inventions claimed in the '626 patent address this need.

29. The '626 patent contains two independent claims and 8 total claims, covering a method and computer readable medium for implementing a change order in an integrated circuit design. Claim 1 reads:

1. A method comprising steps of:

(a) receiving as input an integrated circuit design;

(b) receiving as input an engineering change order to the integrated circuit design;

(c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define an area that is less than an entire area of the integrated circuit design;

(d) performing an incremental routing of the integrated circuit design only for each net in the integrated circuit design that is enclosed by the window;

(e) replacing an area in a copy of the integrated circuit design that is bounded by the coordinates of the window with results of the incremental routing to generate a revised integrated circuit design; and

(f) generating as output the revised integrated circuit design.

30. This claim, as a whole, provides significant benefits and improvements to the function of the semiconductor device design process, *e.g.*, providing a novel and substantially more efficient process flow in which only the affected nets would be considered in the incremental routing. This results in substantial reduction in the expected time of the design portion of producing semiconductor devices.

31. The claims of the '626 patent also recite inventive concepts that improve the functioning of the fabrication process, particularly as to post-ECO routing. The claims of the

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 10 of 95

'626 patent disclose a new and novel solution to specific problems related to improving semiconductor fabrication. As explained in detail above and in the '626 patent specification, the claimed inventions improve upon the prior art processes by ignoring nets that are unaffected by an ECO in performing routing following the ECO. This has the advantage of substantially reducing the impact on design schedule of ECOs and other layout changes, thus increasing the efficiency of the design process and making it easier to improve the design and fix design errors without unduly delaying time-to-market. By making it easier to fix errors as they are found, and causing substantially less incremental delay upon finding and fixing errors, the claimed inventive processes also increase the performance and reliability of the finished product. Because of the claimed inventive processes, individual less impactful design issues that still impact design performance (albeit not on a critical scale) can be caught and fixed without costing the same delay as more substantial errors.

#### COUNT I – INFRINGEMENT OF U.S. PATENT NO. 7,231,626

32. Bell Semic re-alleges and incorporates by reference the allegations of the foregoing paragraphs as if fully set forth herein.

33. The '626 patent is valid and enforceable under the United States Patent Laws.

34. Bell Semic owns, by assignment, all right, title, and interest in and to the '626 patent, including the right to collect for past damages.

35. A copy of the '626 patent is attached at Exhibit A.

36. On information and belief, Micron has and continues to directly infringe pursuant to 35 U.S.C. § 271(a) one or more claims of the '626 patent by using the patented methodology to design one or more semiconductor devices, including as one example the Micron Accused Product, in the United States.

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 11 of 95

37. On information and belief, Micron employs a variety of design tools, for example, Cadence, Synopsys, and/or Siemens tools, to perform incremental routing in implementing an ECO (the "Accused Processes") as recited in the '626 patent claims. As one example, Micron's Accused Processes perform a method for only routing the nets affected by the ECO and merging that changed area into the overall circuit layout as required by claim 1 of the '626 patent. Micron does so by employing a design tool, such as at least one of a Cadence, Synopsys, and/or Siemens tool, to perform incremental routing as part of implementing an ECO for the Micron Accused Product to generate a revised integrated circuit design.

38. Micron's Accused Processes also calculate and perform a parasitic extraction only for each net in the IC design enclosed by the window defining the ECO. (This parasitic extraction is also how the Accused Processes further calculate a net delay only for each net in the IC design enclosed by the window defining the ECO.) Micron does so by employing a design tool, such as at least one of the Cadence, Synopsys, and/or Siemens tools, to perform the incremental routing during implementation of the ECO for the Micron Accused Product's circuit designs.

39. Micron's Accused Processes also perform a design rule check only for each net in the IC design enclosed by the ECO window. Micron does so by employing a design tool, such as at least one of the Cadence, Synopsys, and/or Siemens tools, perform the incremental ECO and automatically perform a DRC for those nets to ensure that the ECO did not violate any design rules when it fixed other issues.

40. An exemplary infringement analysis showing infringement of one or more claims of the '626 patent is set forth in Exhibit B. The declaration of Lloyd Linder, an expert in the field of semiconductor device design, is attached at Exhibit C and further describes Micron's infringement of the '626 patent.

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 12 of 95

41. Micron's Accused Processes infringe and continue to infringe one or more claims of the '626 patent during the pendency of the '626 patent.

42. On information and belief, Micron has and continues to infringe pursuant to 35 U.S.C. § 271, *et. seq.*, directly or indirectly, either literally or under the doctrine of equivalents, by using the Accused Processes in violation of one or more claims of the '626 patent. Micron has and continues to infringe pursuant to 35 U.S.C. § 271, *et. seq.*, directly or indirectly, either literally or under the doctrine of equivalents, by making, selling, or offering to sell in the United States, or importing into the United States products manufactured or otherwise produced using the Accused Processes in violation of one or more claims of the '626 patent.

43. Micron's infringement of the '626 patent is exceptional and entitles Bell Semic to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

44. Bell Semic has been damaged by Micron's infringement of the '626 patent and will continue to be damaged unless Micron is enjoined by this Court. Bell Semic has suffered and continues to suffer irreparable injury for which there is no adequate remedy at law. The balance of hardships favors Bell Semic, and public interest is not disserved by an injunction.

45. Bell Semic is entitled to recover from Micron all damages that Bell Semic has sustained as a result of Micron's infringement of the '626 patent, including without limitation and/or not less than a reasonable royalty.

#### **DEMAND FOR JURY TRIAL**

Plaintiff hereby demands a jury trial for all issues so triable.

### PRAYER FOR RELIEF

WHEREFORE, Bell Semic respectfully requests that this Court enter judgment in its favor as follows and award Bell Semic the following relief:

- (a) a judgment declaring that Micron has infringed one or more claims of the '626 patent in this litigation pursuant to 35 U.S.C. § 271, *et seq.*;

- (b) an award of damages adequate to compensate Bell Semic for infringement of the '626 patent by Micron, in an amount to be proven at trial, including supplemental post-verdict damages until such time as Micron ceases its infringing conduct;

- (c) a permanent injunction, pursuant to 35 U.S.C. § 283, prohibiting Micron and its officers, directors, employees, agents, consultants, contractors, suppliers, distributors, all affiliated entities, and all others acting in privity with Micron from committing further acts of infringement;

- (d) a judgment requiring Micron to make an accounting of damages resulting from Micron's infringement of the '626 patent;

- (e) the costs of this action, as well as attorneys' fees as provided by 35 U.S.C. § 285;

- (f) pre-judgment and post-judgment interest at the maximum amount permitted by law;

- (g) all other relief, in law or equity, to which Bell Semic is entitled.

Dated: October 5, 2022.

### GIVENS PURSLEY LLP

<u>/s/ Alexander P. McLaughlin</u> Alexander P. McLaughlin – Of the Firm Jason J. Blakely Attorneys for Plaintiff

# EXHIBIT A

Case 1:22-cv-00417-DCN Docume

US007231626B2

# (12) United States Patent

#### Hoff et al.

#### (54) METHOD OF IMPLEMENTING AN ENGINEERING CHANGE ORDER IN AN INTEGRATED CIRCUIT DESIGN BY WINDOWS

- (75) Inventors: Jason K. Hoff, Houston, TX (US);

Viswanathan Lakshmanan, Thornton, CO (US); Michael Josephides, Broomfield, CO (US); Daniel W.

Prevedel, Fort Collins, CO (US);

Richard D. Blinne, Ft. Collins, CO (US); Johathan P. Kuppinger, Windsor, CO (US)

- (73) Assignee: LSI Corporation, Milpitas, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 221 days.

- (21) Appl. No.: 11/015,123

- (22) Filed: Dec. 17, 2004

#### (65) **Prior Publication Data**

US 2006/0136855 A1 Jun. 22, 2006

- (51) Int. Cl.

- *G06F 17/50* (2006.01)

- (52) **U.S. Cl.** ...... **716/13**; 716/14; 716/9; 716/10; 716/10; 716/

See application file for complete search history.

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 5,416,717 A | 4 * | 5/1995  | Miyama et al 703/14  |

|-------------|-----|---------|----------------------|

| 5,761,080 A | 4 * | 6/1998  | DeCamp et al 716/5   |

| 5,847,967 A | 4 * | 12/1998 | Asao                 |

| 5,953,236 A | 4 * | 9/1999  | Hossain et al 716/6  |

| 6,014,506 A | 4 * | 1/2000  | Hossain et al 716/11 |

| 6,141,663 A | 4   | 10/2000 | Hunkins et al.       |

| 6,243,715 E | 31  | 6/2001  | Bogantz et al.       |

# (10) Patent No.: US 7,231,626 B2

## (45) **Date of Patent:** Jun. 12, 2007

| 6,317,865    | B1 *   | 11/2001 | Itoh 716/11             |

|--------------|--------|---------|-------------------------|

| 6,453,454    | B1 *   | 9/2002  | Lee et al 716/11        |

| 6,536,028    | B1 *   | 3/2003  | Katsioulas et al 716/17 |

| 6,651,239    | B1 *   | 11/2003 | Nikitin et al 716/18    |

| 6,922,817    | B2 *   | 7/2005  | Bradfield et al 716/1   |

| 7,051,307    | B2 *   | 5/2006  | Ditlow et al 716/7      |

| 7,168,055    | B2 *   | 1/2007  | Hoff et al 716/4        |

| 2004/0003366 | A1 $*$ | 1/2004  | Suzuki 716/11           |

| 2004/0199879 | A1*    | 10/2004 | Bradfield et al 716/1   |

#### (Continued)

#### OTHER PUBLICATIONS

Xiang et al., "ECO Algorithms for Removing Overlaps Between Power Rails and Signal Wires", IEEE/ACM International Conference on Computer Aided Design, Nov. 10, 2002, pp. 67-74.\*

Primary Examiner—Phallaka Kik (74) Attorney, Agent, or Firm—Eric J. Whitesell

#### (57) **ABSTRACT**

A method of implementing an engineering change order includes steps of: (a) receiving as input an integrated circuit design; (b) receiving as input an engineering change order to the integrated circuit design; (c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define an area that is less than an entire area of the integrated circuit design; (d) performing a routing of the integrated circuit design; (d) performing a narea in a copy of the integrated circuit design that is bounded by the coordinates of the window; (e) replacing an area in a copy of the integrated circuit design that is bounded by the coordinates of the window with results of the incremental routing to generate a revised integrated circuit design; and (f) generating as output the revised integrated circuit design.

#### 8 Claims, 5 Drawing Sheets

# US 7,231,626 B2 Page 2

### U.S. PATENT DOCUMENTS

| 2005/0015735 A | .1* 1/2005 | Tamura et al 716/2  |

|----------------|------------|---------------------|

| 2005/0125756 A | .1* 6/2005 | Ditlow et al 716/7  |

| 2005/0160391 A | .1* 7/2005 | Orita 716/13        |

| 2005/0166169 A | .1* 7/2005 | Kurzum et al 716/10 |

| 2005/0235240 | A1* | 10/2005 | Tien 716/11       |  |

|--------------|-----|---------|-------------------|--|

| 2006/0036982 | A1* | 2/2006  | Hoff et al 716/5  |  |

| 2006/0288322 | A1* | 12/2006 | Zhang et al 716/9 |  |

\* cited by examiner

**U.S.** Patent

Jun. 12, 2007

Sheet 2 of 5

US 7,231,626 B2

FIG. 2

| U.S. Patent Jun. 12, 2007 Sheet 4 of 5 US 7 | 7,231,626 B2 |

|---------------------------------------------|--------------|

|---------------------------------------------|--------------|

400 —

*FIG.* 4

U.S. Patent

Jun. 12, 2007

Sheet 5 of 5

US 7,231,626 B2

5

25

45

## 1

#### METHOD OF IMPLEMENTING AN ENGINEERING CHANGE ORDER IN AN INTEGRATED CIRCUIT DESIGN BY WINDOWS

#### BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates generally to the design of integrated circuits. More specifically, but without limitation <sup>10</sup> thereto, the present invention relates to methods of implementing an engineering change order (ECO) in an integrated circuit design.

2. Description of Related Art

In previous methods for implementing an engineering <sup>15</sup> change order (ECO) request in an integrated circuit design, design tools are run for the entire integrated circuit design, even though the engineering change order typically is only a small fraction of the size of the integrated circuit design. For example, cell placement, routing, design rule check <sup>20</sup> validation, and timing closure run times typically scale with the size of the entire integrated circuit design.

#### SUMMARY OF THE INVENTION

In one embodiment of the present invention, a method of implementing an engineering change order in an integrated circuit design by windows includes steps of:

(a) receiving as input an integrated circuit design;

- (b) receiving as input an engineering change order to the <sup>30</sup> integrated circuit design;

- (c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define <sup>35</sup> an area that is less than an entire area of the integrated circuit design;

- (d) performing a routing only for each net in the integrated circuit design that is enclosed by the window;

- (e) replacing an area in a copy of the integrated circuit <sup>40</sup> design that is bounded by coordinates of the window with results of the incremental routing to generate a revised integrated circuit design; and

- (f) generating as output the revised integrated circuit design. In another embodiment of the present invention, a com-

puter program product for implementing an engineering change order in an integrated circuit design by windows includes:

- a medium for embodying a computer program for input to a  $_{50}$  computer; and

- a computer program embodied in the medium for causing the computer to perform steps of:

- (a) receiving as input an integrated circuit design;

- (b) receiving as input an engineering change order to the 55 integrated circuit design;

- (c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define 60 an area that is less than an entire area of the integrated circuit design;

- (d) performing a routing of the integrated circuit design only for each net in the integrated circuit design that is enclosed by the window;

- (e) replacing an area in a copy of the integrated circuit design that is bounded by coordinates of the window with

2

results of the incremental routing to generate a revised integrated circuit design; and

(f) generating as output the revised integrated circuit design.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention is illustrated by way of example and not limitation in the accompanying figures, in which like references indicate similar elements throughout the several views of the drawings, and in which:

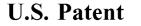

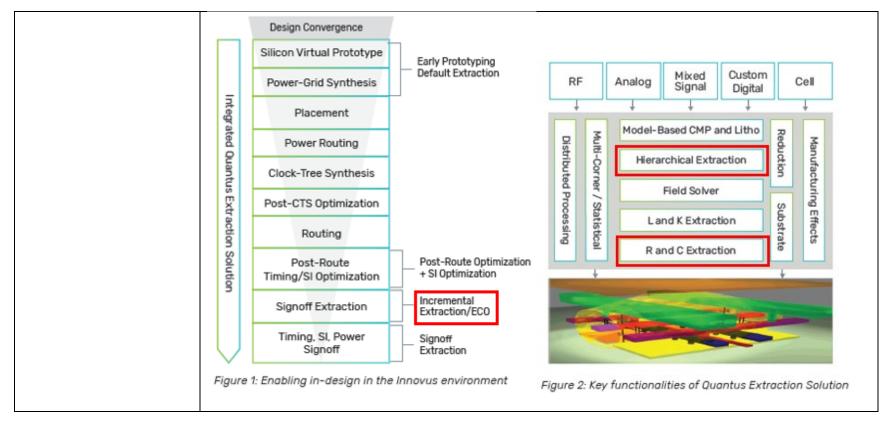

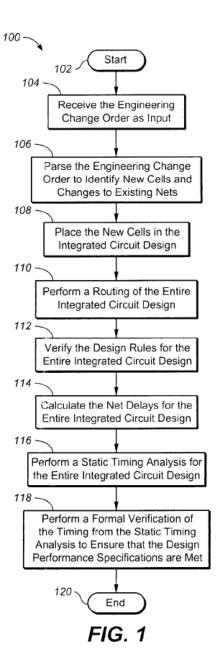

FIG. 1 illustrates a flow chart for a method of implementing an engineering change order in an integrated circuit design according to the prior art;

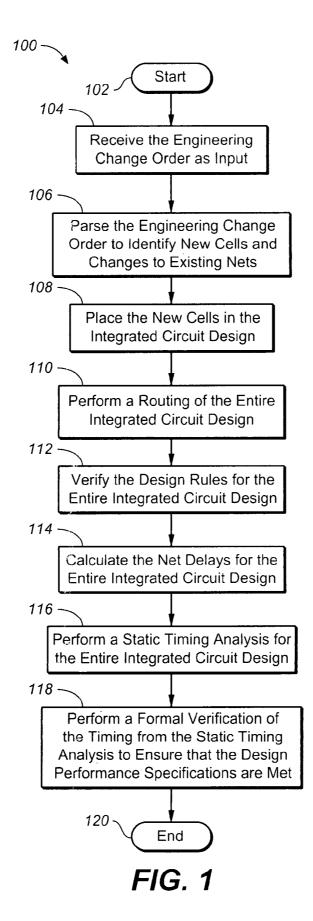

FIGS. 2A and 2B illustrate a flow chart for a method of implementing an engineering change order in an integrated circuit design by windows;

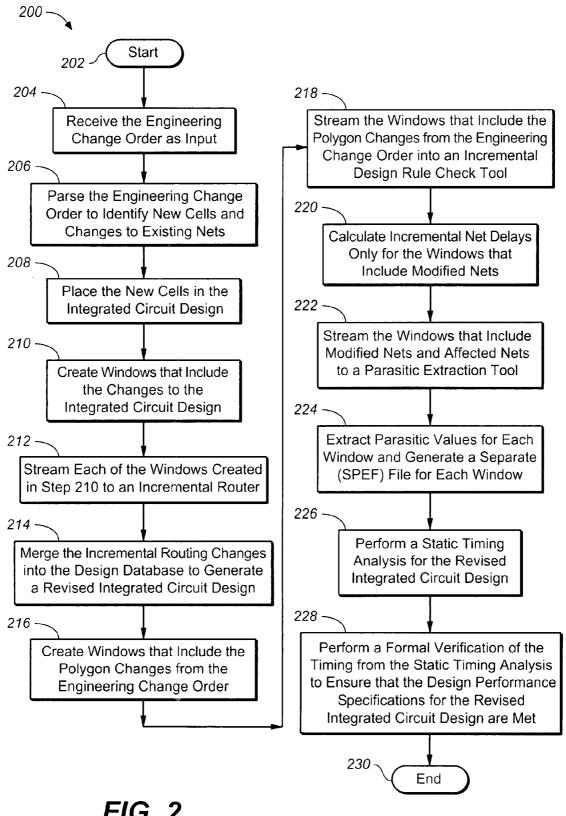

FIG. **3** illustrates a flow chart for creating an engineering change order window for FIGS. **2**A and **2**B;

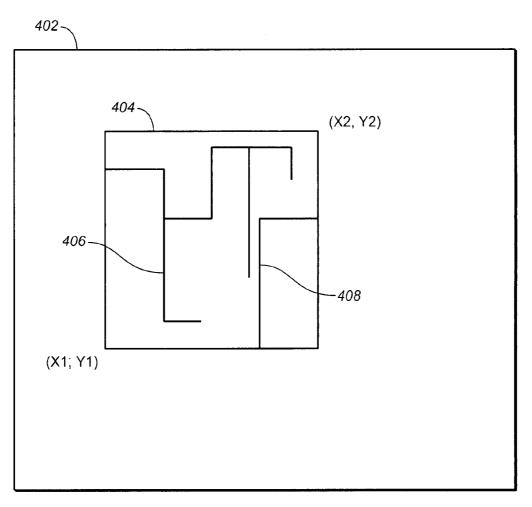

FIG. **4** illustrates a diagram of a window in an integrated circuit design;

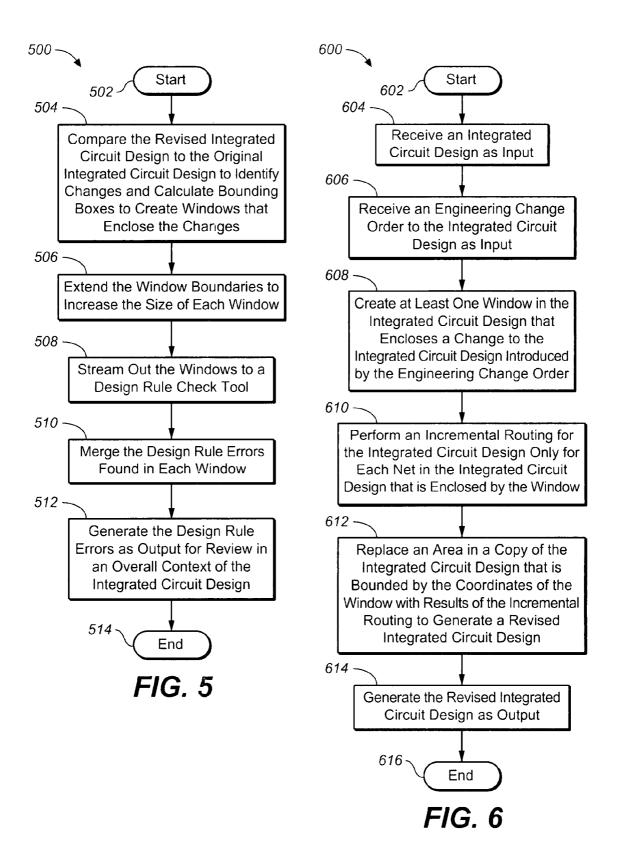

FIG. **5** illustrates a flow chart for performing an incremental design rule check for FIGS. **2**A and **2**B; and

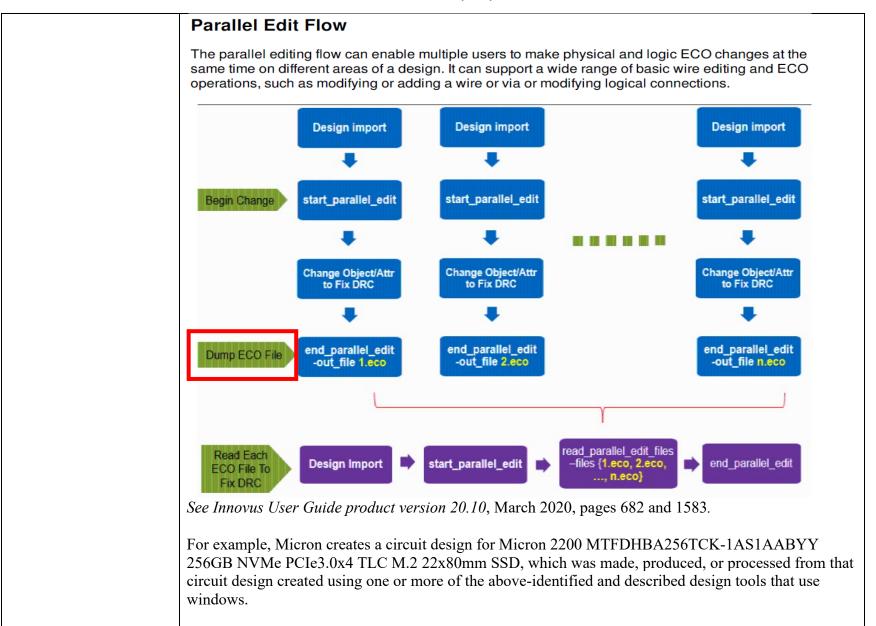

FIG. 6 illustrates a flow chart of a computer program for implementing an engineering change order in an integrated circuit design by windows.

Elements in the figures are illustrated for simplicity and clarity and have not necessarily been drawn to scale. For example, the dimensions of some elements in the figures may be exaggerated relative to other elements to point out distinctive features in the illustrated embodiments of the present invention.

#### DESCRIPTION OF THE ILLUSTRATED EMBODIMENTS

In previous methods for implementing a functional or timing engineering change order (ECO) to an integrated circuit design, the typical turnaround time is typically about one week regardless of the size of the engineering change order. This is because although the engineering change order may only have a size of a few cells, it must be merged with an integrated circuit design that typically has a much greater size. For example, if an engineering change order for five cells may be required for an integrated circuit design that includes five million cells. As a result, design tool run times generally scale with the size of the entire integrated circuit design for routing, design rule check verification, net delay calculation, and parasitic extraction. Preferably, the time required to implement an engineering change order should depend on the number of net changes in the engineering change order rather than on the total number of nets in the entire integrated circuit design.

FIG. 1 illustrates a flow chart 100 for a method of implementing an engineering change order according to the prior art.

Step 102 is the entry point for the flow chart 100.

In step 104, the engineering change order is received as input.

In step 106, the engineering change order is parsed to identify new cells and changes to existing nets.

In step **108**, the new cells are placed in the integrated circuit design by a software place and route design tool.

In step **110**, a routing of the entire integrated circuit design <sup>65</sup> is performed by the place and route design tool.

In step **112**, the design rules for the technology used to manufacture the integrated circuit are verified for the entire

integrated circuit design, for example, by design rule check software such as Mentor Calibre<sup>™</sup>.

In step 114, the net delays are calculated for the entire integrated circuit design.

In step 116, a parasitic extraction is performed for the 5 entire integrated circuit design to determine the values of net coupling capacitance and parasitic resistance.

In step 118, a static timing analysis is performed for the entire integrated circuit design to determine the effect of net delay including net parasitic capacitance and resistance on 10 the integrated circuit design.

In step 120, a formal verification of the timing is performed from the static timing analysis to ensure that the design timing specifications are met.

Step 122 is the exit point of the flow chart 100.

In the method of FIG. 1, steps 110, 112, 114 and 116 may be especially time consuming and resource intensive, depending on the complexity of the integrated circuit design. A significant savings in the resources required to perform routing, design rule check verification, net delay calculation, 20 and parasitic extraction may be realized by creating windows in the integrated circuit design that include only the incremental changes to the overall integrated circuit design as follows.

In one embodiment of the present invention, a method of 25 implementing an engineering change order in an integrated circuit design includes steps of:

(a) receiving as input an integrated circuit design;

- (b) receiving as input an engineering change order to the integrated circuit design;

- (c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define an area that is less than an entire area of the integrated 35 circuit design;

- (d) performing a routing only for each net in the integrated circuit design that is enclosed by the window;

- (e) replacing an area in a copy of the integrated circuit design that is bounded by coordinates of the window with 40 results of the incremental routing to generate a revised integrated circuit design; and

(f) generating as output the revised integrated circuit design.

FIGS. 2A and 2B illustrate a flow chart 200 for a method of implementing an engineering change order in an inte- 45 each window. grated circuit design by windows.

Step 202 is the entry point for the flow chart 200.

In step 204, the engineering change order is received as input as in FIG. 1.

In step 206, the engineering change order is parsed to 50 identify new nets and changes to existing nets that constitute the changes to the integrated circuit design in the same manner as in FIG. 1.

In step 208, the new cells are placed in the integrated circuit design, for example, by a software place and route 55 design tool in the same manner as FIG. 1.

In step 210, windows are created that include the new cells and the net changes that constitute the changes to the integrated circuit design that are to be routed. The term "window" as used herein is defined as a rectilinear boundary 60 that encloses an area of the integrated circuit design that is less than the entire area of the integrated circuit design. For example, a window may include a subset of nets that have been changed by the engineering change order. Alternatively, a window may include polygons that have been 65 introduced or changed by the engineering change order. The window boundaries are calculated from the coordinates of

4

the new polygons and the changed nets in the integrated circuit design database so that each of the changes to the integrated circuit design is enclosed by a window.

In step 212, each of the windows created in step 210 is streamed to an incremental router. The incremental routing may be performed by the same routing tool used in FIG. 1, however, only the nets that are modified by the engineering change order are routed, in contrast to routing the entire integrated circuit design as in FIG. 1. Windows that do not overlap may be routed in parallel, while windows that do overlap are routed serially so that any duplicated routing may be removed. If any nets in a window are found open, that is, not all of the net connections are included in the window, then the net is "frozen", which means that the net <sup>15</sup> may not be changed by the router. In addition, a partition manager is preferably included in the incremental router that allows the user to expand the size of the windows and merge overlapping windows.

In step 214, the incremental routing changes are merged into the design database, for example, by replacing the contents enclosed by the coordinates of each window in a copy of the original integrated circuit design by the contents of the window to generate a revised integrated circuit design.

In step 216, windows are created that include the polygon changes from the engineering change order.

In step 218, the windows that include the polygon changes from the engineering change order are streamed into an incremental design rule check tool. The incremental design rule check tool checks only the polygons that were changed, advantageously avoiding unnecessary re-checking of the all the polygons in the integrated circuit database.

In step 220, incremental net delays are calculated only for the windows that include modified nets, advantageously avoiding unnecessary re-calculation of all the net delays in the integrated circuit design.

In step 222, the windows that include modified nets and affected nets are streamed to a parasitic extraction tool. An affected net is a net that has a coupling capacitance with a modified net that exceeds a predefined coupling capacitance threshold

In step 224, parasitic values are extracted for each window, and a separate standard parasitic extraction format (SPEF) file is generated by the parasitic extraction tool for

In step 226, a static timing analysis is performed for the revised integrated circuit design in the same manner as in FIG. 1.

In step 228, a formal verification of the timing is performed from the static timing analysis to ensure that the design performance specifications for the revised integrated circuit design are met in the same manner as in FIG. 1.

Step 230 is the exit point of the flow chart 200.

FIG. 3 illustrates a flow chart 300 for creating an engineering change order window for FIG. 2.

Step 302 is the entry point of the flow chart 300.

In step 304, the port instances for each net changed by the engineering change order are identified. A net change may be, for example, a net that has moved or has different connections.

In step 306, a bounding box that includes the port instances for each net changed by the engineering change order is calculated from the net coordinates in the design database of the original integrated circuit design.

In step 308, port instances that changed from being connected to a net to being tied high or low are identified.

In step 310, a bounding box that includes the port instances that changed from being connected to a net to being tied high or low is calculated from the coordinates in the design database.

In step **312**, overlapping bounding boxes are merged, and 5 the contents of all the bounding boxes are copied into a new cell.

In step 314, any wire that crosses a boundary of the new cell is named as a pin of the new cell.

In step 316, the coordinates of the bounding boxes are 10 generated as output to define windows that enclose the changes introduced by the engineering change order.

Step 318 is the exit point of the flow chart 300.

FIG. 4 illustrates a diagram of a window in an integrated circuit design. Shown in FIG. 4 are an integrated circuit 15 (f) generating as output the revised integrated circuit design. design 402, a window 404, a changed net 406, and an affected net 408.

In FIG. 4, The window 404 is bounded by the coordinates (X1, Y1):(X2, Y2) that enclose the changed net 406 and the affected net 408. The area enclosed by the window 404 is 20 less than the entire area of the integrated circuit design 402, thereby reducing the number of calculations required to implement the engineering change order.

In this example, the changed net 406 has been moved, resulting in a coupling capacitance with the affected net 408 25 that exceeds a threshold coupling capacitance. The affected net 408 is therefore included in the window for calculating the incremental net delay and for performing the parasitic extraction.

incremental design rule check for FIGS. 2A and 2B

Step 502 is the entry point of the flow chart 500.

In step 504, the revised integrated circuit design is compared to the original integrated circuit design to identify changes, and bounding boxes are calculated to create win- 35 dows that enclose only the physical changes and not the entire nets.

In step 506, the window boundaries are extended to increase the size of each window, forming a halo margin or region around each window. The halo region allows the 40 design rule check software to examine objects that are nearby each window. The size of the halo margin may be determined, for example, by the design rule check tool or by the user to ensure that there is sufficient room for the spacing rules to work correctly.

In step 508, the windows are streamed out, for example, in GDSII format, to a design rule check tool, which may be the same as that used in FIG. 1.

In step 510, the design rule errors found in each window are merged together, removing any errors in the halo region. 50

In step 512, the design rule errors are generated as output for review in an overall context of the integrated circuit design.

Step 514 is the exit point of the flow chart 500.

The flow chart described above may also be implemented 55 by instructions for being performed on a computer. The instructions may be embodied in a disk, a CD-ROM, and other computer readable media according to well known computer programming techniques.

In another aspect of the present invention, a computer 60 program product for analyzing noise for an integrated circuit design includes:

- a medium for embodying a computer program for input to a computer; and

- a computer program embodied in the medium for causing 65 the computer to perform steps of:

- (a) receiving as input an integrated circuit design;

6

- (b) receiving as input an engineering change order to the integrated circuit design;

- (c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define an area that is less than an entire area of the integrated circuit design;

- (d) performing a routing only for each net in the integrated circuit design that is enclosed by the window;

- (e) replacing an area in a copy of the integrated circuit design that is bounded by coordinates of the window with results of the incremental routing to generate a revised integrated circuit design; and

- FIG. 6 illustrates a flow chart 600 of a computer program

- for implementing an engineering change order in an integrated circuit design by windows.

Step 602 is the entry point of the flow chart 600.

In step 604, an integrated circuit design is received as input.

In step 606, an engineering change order to the integrated circuit design is received as input.

In step 608, at least one window is created in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order. The window is bounded by coordinates that define an area that is less than an entire area of the integrated circuit design.

In step 610, an incremental routing is performed for the FIG. 5 illustrates a flow chart 500 for performing an 30 integrated circuit design only for each net in the integrated circuit design that is enclosed by the window, advantageously avoiding repeating calculations for nets that are not changed or affected by the engineering change order.

> In step 612, an area in a copy of the integrated circuit design that is bounded by the coordinates of the window is replaced with results of the incremental routing to generate a revised integrated circuit design.

> In step 614, the revised integrated circuit design is generated as output.

Step 616 is the exit point of the flow chart 600.

Although the methods illustrated by the flowchart descriptions above are described and shown with reference to specific steps performed in a specific order, these steps may be combined, sub-divided, or reordered without departing from the scope of the claims. Unless specifically indicated herein, the order and grouping of steps are not limitations of the claims.

The specific embodiments and applications thereof described above are for illustrative purposes only and do not preclude modifications and variations that may be made thereto by those skilled in the art within the scope of the following claims.

#### What is claimed is:

1. A method comprising steps of:

- (a) receiving as input an integrated circuit design;

- (b) receiving as input an engineering change order to the integrated circuit design;

- (c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define an area that is less than an entire area of the integrated circuit design;

- (d) performing an incremental routing of the integrated circuit design only for each net in the integrated circuit design that is enclosed by the window;

- (e) replacing an area in a copy of the integrated circuit design that is bounded by the coordinates of the window with results of the incremental routing to generate a revised integrated circuit design; and

- (f) generating as output the revised integrated circuit 5 design.

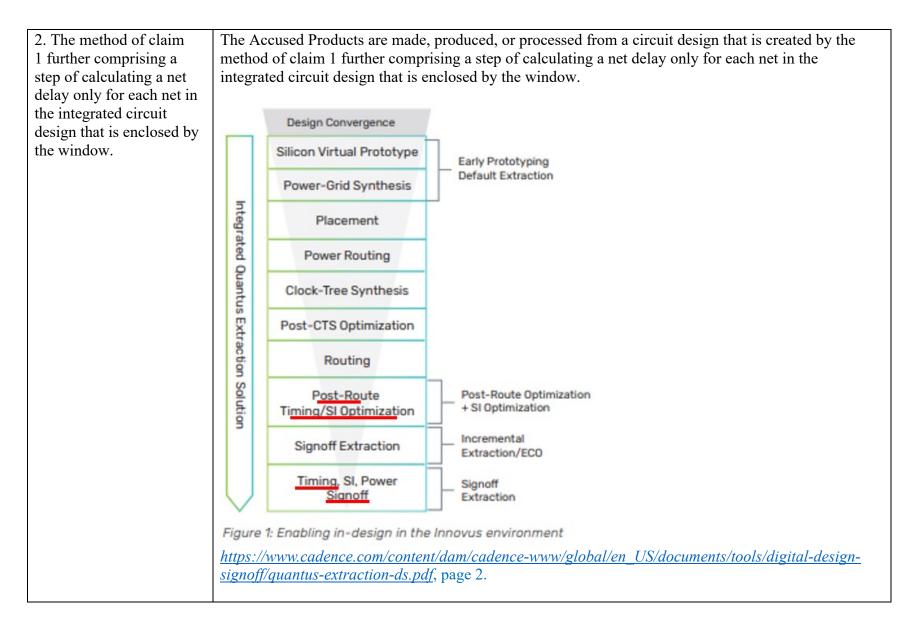

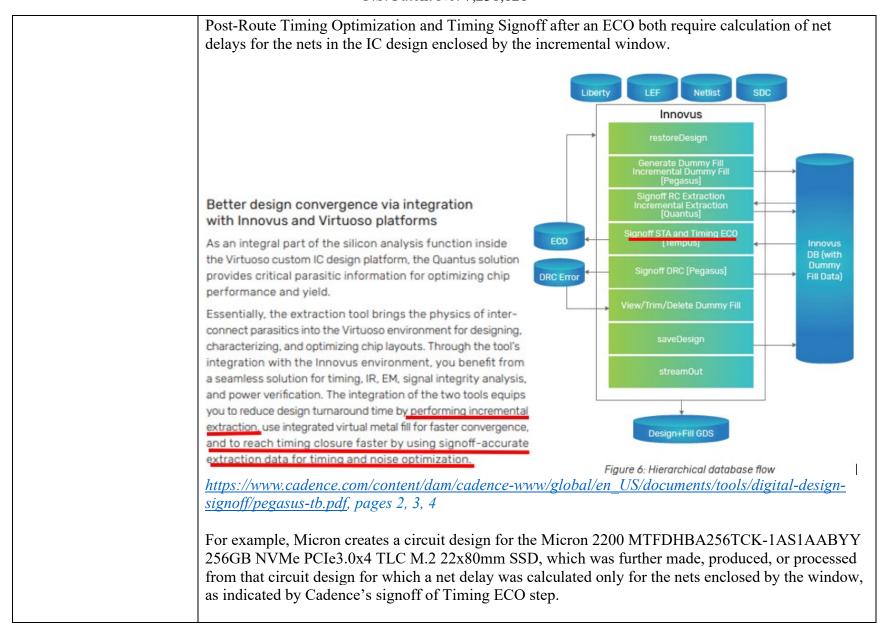

2. The method of claim 1 further comprising a step of calculating a net delay only for each net in the integrated circuit design that is enclosed by the window.

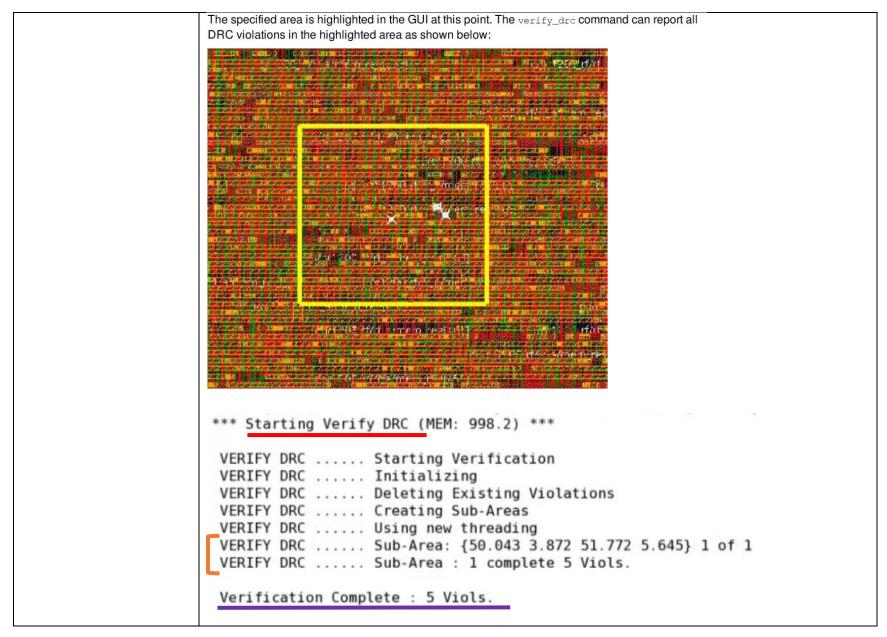

**3**. The method of claim **1** further comprising a step of 10 performing a design rule check only for each net in the integrated circuit design that is enclosed by the window.

4. The method of claim 1 further comprising a step of performing a parasitic extraction only for each net in the integrated circuit design that is enclosed by the window.

**5**. A computer readable storage medium tangibly embodying instructions for a computer that when executed by the computer implement a method for implementing an engineering change order in an integrated circuit design by windows, the method comprising steps of:

(a) receiving as input an integrated circuit design;

- (b) receiving as input an engineering change order to the integrated circuit design;

- (c) creating at least one window in the integrated circuit design that encloses a change to the integrated circuit 25 design introduced by the engineering change order

8

wherein the window is bounded by coordinates that define an area that is less than an entire area of the integrated circuit design;

- (d) performing an incremental routing only for each net in the integrated circuit design that is enclosed by the window;

- (e) replacing an area in a copy of the integrated circuit design that is bounded by coordinates of the window with results of the incremental routing to generate a revised integrated circuit design; and

- (f) generating as output the revised integrated circuit design.

6. The computer readable storage medium of claim 5 wherein the method further comprises a step of calculating15 a net delay only for each net in the integrated circuit design that is enclosed by the window.

7. The computer readable storage meduim of claim 5 wherein the method further comprises a step of performing a design rule check only for each net in the integrated circuit 20 design that is enclosed by the window.

**8**. The computer readable storage medium of claim **5** wherein the method further comprises a step of performing a parasitic extraction only for each net in the integrated circuit design that is enclosed by the window.

\* \* \* \* \*

# EXHIBIT B

#### Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 27 of 95 BELL SEMICONDUCTOR LLC'S ANALYSIS OF INFRINGEMENT

#### U.S. Patent No. 7,231,626

## Claims 1-4

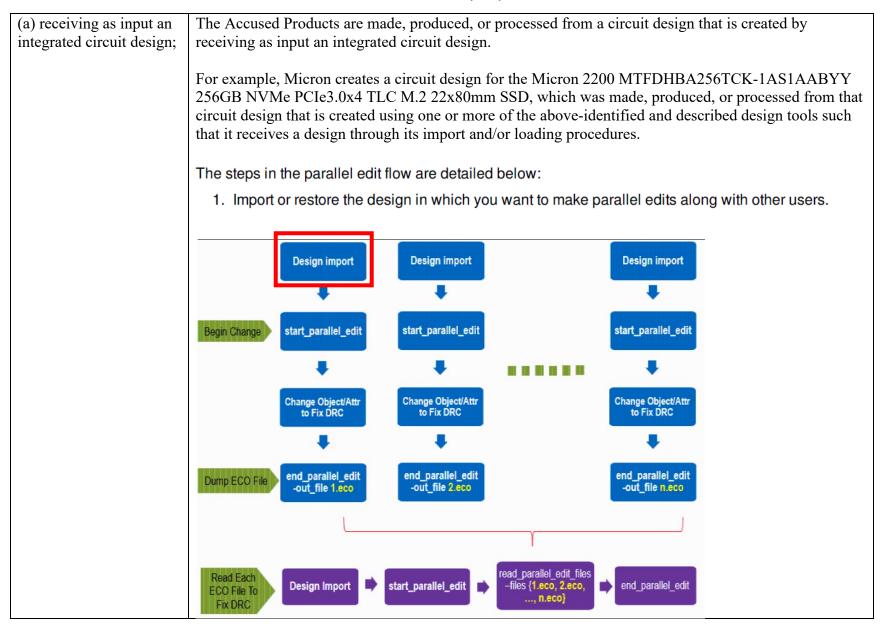

Bell Semiconductor, LLC ("Bell Semiconductor") provides evidence of infringement of exemplary claims 1-4 of U.S. Patent No. 7,231,626 ("the '626 patent") by the Micron 2200 MTFDHBA256TCK-1AS1AABYY 256GB NVMe PCIe3.0x4 TLC M.2 22x80mm SSD produced by Micron Technology, Inc. ("Micron"). In support thereof, Bell Semiconductor provides the following claim charts.

"Accused Products" as used herein refers to the Micron circuit designs and/or semiconductor products, including at least the Micron 2200 MTFDHBA256TCK-1AS1AABYY 256GB NVMe PCIe3.0x4 TLC M.2 22x80mm SSD, that are made, produced, and/or processed by a design tool, such as a Cadence Design Systems, Inc. ("Cadence") tool, by implementing an engineering change order through a window that is less than the entire area of the integrated circuit design. On information and belief, these design tools all function similarly with respect to the functionality described herein. For simplicity, the Cadence tool will be the primary tool cited herein to illustrate infringement of the claimed methods. These claim charts demonstrate infringement by comparing each element of the asserted claims to corresponding components, aspects, and/or features of the Accused Products. These claim charts are not intended to constitute an expert report on infringement. These claim charts include information provided by way of example, and not by way of limitation.

The analysis set forth below is based only upon information from publicly available resources regarding the Accused Products, as Micron and relevant third parties have not yet provided any non-public information. An analysis of non-public technical documentation may assist in further identifying all infringing features and functionality. Accordingly, Bell Semiconductor reserves the right to supplement this infringement analysis once such information is made available to Bell Semiconductor. Furthermore, Bell Semiconductor reserves the right to revise this infringement analysis, as appropriate, upon issuance of a court order construing any terms recited in the asserted claims or as other circumstances so merit.

Bell Semiconductor contends that each element of each claim asserted herein is literally met, and would also be met under the doctrine of equivalents, as there are no substantial differences between the Accused Products and the elements of the patent claims in function, way, and result. If Micron attempts to argue that there is no literal infringement and/or if Micron attempts to draw any distinction between the claimed functionality and the Accused Products, then Bell Semiconductor reserves the right to rebut the alleged distinction as a matter of literal infringement and/or as to whether any such distinction is substantial under the doctrine of equivalents.

Unless otherwise noted, the cited evidence applies across each of Micron's products that were made, produced, or processed from a circuit design using windows, including but not limited to Micron 2200 MTFDHBA256TCK-1AS1AABYY 256GB NVMe PCIe3.0x4 TLC M.2 22x80mm SSD. Bell Semiconductor reserves the right to amend this infringement analysis based on other products made, produced, or processed in the same or similar manner to that identified herein.

# Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 28 of 95

| Claim 1                          | Accused Product                                                                                                                                                                                                 |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. A method comprising steps of: | To the extent the preamble is limiting, the Accused Products are produced by performing the method steps outlined in the remaining claim elements.                                                              |

|                                  | Running ECO Routing                                                                                                                                                                                             |

|                                  | The NanoRoute router performs ECO routing by completing partial routes with added logic while maintaining the existing wire segments as much as possible. ECO routing is useful in cases such as the following: |

|                                  | <ul> <li>After the chip is initially routed, the customer or chip owner gives you a new netlist with minor changes.</li> </ul>                                                                                  |

|                                  | • After the chip is initially routed, buffers were added to repair setup or hold violations or DRVs during physical optimization.                                                                               |

|                                  | <ul> <li>Buffers were added or gates were resized during hand editing of a routed design.</li> </ul>                                                                                                            |

|                                  | <ul> <li>Antenna diodes were added interactively after routing to repair process antenna violations.</li> </ul>                                                                                                 |

|                                  | After metal fill is added to the design.                                                                                                                                                                        |

|                                  |                                                                                                                                                                                                                 |

## Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 29 of 95

## Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 30 of 95

# Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 31 of 95

|                                                                                               | <pre>Step 1 Load the entire chip into Innovus and use start_parallel_edit -region (Areal_coordinates) to specify the area in which ECO changes are required. After the relevant operation is completed, use the end_parallel_edit -out_file 1.eco command to record the changes to the chip in the 1.eco file. The specific example script and ECO file are as follows: Example script restoreDesign fullchip.enc.dat fullchip start_parallel_edit -area_restricted -region {0.0 0.0 104.04 102.976} ecoDeleteRepeater -inst instB/AOB_inst end_parallel_edit -out_file diff_1 exit See Innovus User Guide product version 20.10, March 2020, pages 1583 and 1590.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (b) receiving as input an<br>engineering change order<br>to the integrated circuit<br>design; | <ul> <li>The Accused Products are made, produced, or processed from a circuit design that is created by receiving as input an engineering change order to the integrated circuit design.</li> <li>Initialize parallel editing by using the start_parallel_edit command.</li> <li><u>The start_parallel_edit command is used to define the area where you need to perform</u></li> <li><u>DRC fixing or ECO operations</u>. The command draws a yellow square on the main window to indicate the edit area and saves the physical data, net attributes, via cell names, and Non-Default Rules (NDRs) to multiple binary files. Use the -region {x1 y1 x2 y2} parameter to specify the coordinates of the edit area. Specify the -area_restricted parameter to write out only the different objects inside or touching the specified edit area. This is a strict interpretation of the region, and ignores the changes made outside of the region. The other engineers should also initialize start_parallel_edit in their sessions separately to specify their own operating areas. Area overlap is not recommended because it might cause ECO conflicts.</li> </ul> |

## Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 32 of 95

# Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 33 of 95

| (c) creating at least one<br>window in the integrated<br>circuit design that<br>encloses a change to the                                                                                                                                                     | The Accused Products are made, produced, or processed from a circuit design that is created by creating at least one window in the integrated circuit design that encloses a change to the integrated circuit design introduced by the engineering change order wherein the window is bounded by coordinates that define an area that is less than an entire area of the integrated circuit design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| encloses a change to the<br>integrated circuit design<br>introduced by the<br>engineering change order<br>wherein the window is<br>bounded by coordinates<br>that define an area that is<br>less than an entire area of<br>the integrated circuit<br>design; | 2. Initialize parallel editing by using the start_parallel_edit command.<br>The start_parallel_edit command is used to define the area where you need to perform DRC fixing or ECO operations. The command draws a yellow square on the main window to indicate the edit area and saves the physical data, net attributes, via cell names, and Non-Default Rules (NDRs) to multiple binary files. Use the -region {x1 y1 x2 y2} parameter to specify the coordinates of the edit area. Specify the -area_restricted parameter to write out only the different objects inside or touching the specified edit area. This is a strict interpretation of the region, and ignores the changes made outside of the region. The other engineers should also initialize start_parallel_edit in their sessions separately to specify their own operating areas. Area overlap is not recommended because it might cause ECO conflicts. |

|                                                                                                                                                                                                                                                              | Area 1 Area 2<br>Area 3<br>In the above step, ECO changes were made in Area1 in the parallel editing mode. Similarly, ECO changes are made in Area2 and Area3, and then end_parallel_edit is used to write the modified physical and logical information in these areas to the 2.eco and 3.eco files, respectively.<br>See Innovus User Guide product version 20.10, March 2020, pages 1584 and 1590-91.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 34 of 95

| xample, Micron creates a circuit design for the Micron 2200 MTFDHBA256TCK-1AS1AABYY<br>B NVMe PCIe3.0x4 TLC M.2 22x80mm SSD, which was made, produced, or processed from that<br>it design that is created by a using a parallel edit command that draws a square to enclose the edit<br>for the ECO. The edit area is less than an entire area of the integrated circuit design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accused Products are made, produced, or processed from a circuit design that is created by mining an incremental routing of the integrated circuit design only for each net in the integrated it design that is enclosed by the window.<br>ake DRC fixes on ECO changes in your assigned area in the design. Multiple engineers an work simultaneously on different areas in the design in the parallel edit mode.<br>following example shows the report information generated by start_parallel_edit.<br>start_parallel_edit -region 0.0 0.0 500.4 431.6<br>g net attribute and regular wire/via information<br>g physical pin information<br>g pouting blockage information<br>g special wire/via informat |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 35 of 95

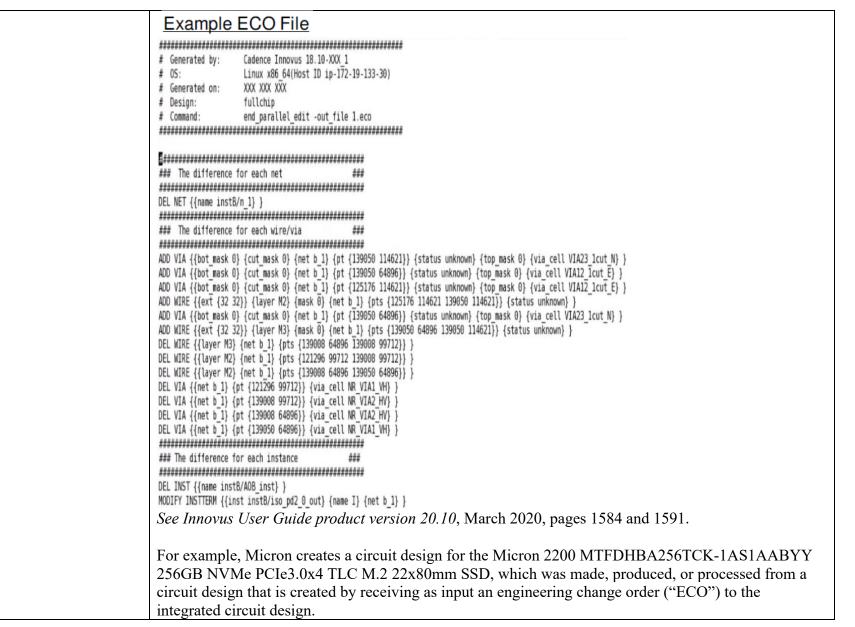

| <pre># Generated by: Cadence Innovus 18.10-XXX 1 # OS: Linux x86_64(Host ID ip-172-19-133-30) # Generated on: XXX XXX XXX # Design: fullchip # Command: end_parallel_edit -out_file 1.eco ####################################</pre> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>## The difference for each net ## ##################################</pre>                                                                                                                                                      |

# Case 1:22-cv-00417-DCN Document 1 Filed 10/05/22 Page 36 of 95

| (e) replacing an area in a<br>copy of the integrated<br>circuit design that is<br>bounded by the<br>coordinates of the<br>window with results of<br>the incremental routing<br>to generate a revised<br>integrated circuit design;<br>and | The Accused Products are made, produced, or processed from a circuit design that is created by replacing an area in a copy of the integrated circuit design that is bounded by the coordinates of the window with results of the incremental routing to generate a revised integrated circuit design. <b>Step 2</b> Load the entire chip first and then read the eco files generated in the previous step by using the read_parallel_edit_files command. All the changes in different areas will be reflected in the chip. See Innovus User Guide product version 20.10, March 2020, pages 1585 and 1591. For example, Micron creates a circuit design for the Micron 2200 MTFDHBA256TCK-1AS1AABYY 256GB NVMe PCIe3.0x4 TLC M.2 22x80mm SSD, which was made, produced, or processed from that circuit design that is created by replacing an area in a copy of the integrated circuit design that is bounded by the square of the edit area with results of the incremental routing to generate a revised integrated circuit design.                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|