## UNITED STATES DISTRICT COURT WESTERN DISTRICT OF TEXAS AUSTIN DIVISION

Vervain, LLC,

Plaintiff,

v.

Kingston Technology Company, Inc., Kingston Digital, Inc., and Kingston Technology Corporation, Civil Action No. 1:24-cv-254

JURY TRIAL DEMANDED

Defendants.

# **COMPLAINT FOR PATENT INFRINGEMENT**

Plaintiff Vervain, LLC ("Vervain") asserts the following claims for patent infringement against Defendants Kingston Technology Company, Inc., Kingston Digital, Inc., and Kingston

Technology Corporation (collectively "Defendants" or "Kingston"), and alleges as follows.

# NATURE OF THE ACTION

1. This is a civil action for infringement under the patent laws of the United States of America, 35 U.S.C. § 1 *et seq*.

2. Vervain is the owner of all rights, title, and interest in U.S. Patent Nos. 8,891,298;

9,196,385; 9,997,240; 10,950,300; 11,830,546; and 11,854,612 (collectively, the "Asserted Patents").

3. Defendants have infringed and continue to infringe one or more claims of Vervain's Asserted Patents by making, using, offering to sell, and selling within the United States, and importing into the United States, including in this District, certain flash memory products. Vervain seeks injunctive relief and monetary damages.

#### THE PARTIES

4. Plaintiff Vervain is a Texas limited liability company with its principal place of business located at 7424 Mason Dells Drive, Dallas, Texas 75230.

5. On information and belief, Defendant Kingston Technology Company, Inc. is a corporation organized under the laws of Delaware, with its principal place of business at 17600 Newhope Street, Fountain Valley, California 92708. Defendant Kingston Technology Company, Inc. can be served at the address for its agent for service, Tracy Chang, 17600 Newhope Street, Fountain Valley, California 92708.

6. On information and belief, Defendant Kingston Digital, Inc. is a corporation organized under the laws of Delaware, with its principal place of business at 17600 Newhope Street, Fountain Valley, California 92708. Defendant Kingston Digital, Inc. can be served at the address for its agent for service, Tracy Chang, 17600 Newhope Street, Fountain Valley, California 92708.

7. On information and belief, Defendant Kingston Technology Corporation is a corporation organized under the laws of California, with its principal place of business at 17600 Newhope Street, Fountain Valley, California 92708. Defendant Kingston Technology Corporation can be served at the address for its agent for service, Tracy Chang, 17600 Newhope Street, Fountain Valley, California 92708.

8. Kingston is "a world leader in memory products and technology solutions," and in the flash memory industry, it is the number-one third-party supplier of branded SSD modules.<sup>1</sup> It has been ranked as the 23<sup>rd</sup> largest private company in the U.S.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup> Ex. G, https://www.businesswire.com/news/home/20231115145037/en/Kingston-Digital-Leads-Channel-SSD-Shipments-in-2022

<sup>&</sup>lt;sup>2</sup> Ex. H, <u>https://www.kingston.com/en/company/press/article/68066</u>

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 3 of 82

9. Kingston sells a variety of flash memory products, including solid state drives (SSDs),<sup>3</sup> USB flash drives,<sup>4</sup> memory cards such as SD and microSD,<sup>5</sup> and embedded flash products like eMMC and UFS.<sup>6</sup> Kingston touts: "From SATA to NVMe, laptop to server, Kingston SSDs provide the speed and reliability you want."<sup>7</sup> To provide this speed and reliability, Kingston uses a variety of flash memory controllers from companies like Phison and Silicon Motion. These flash memory controllers manage the storage of data on Kingston's devices in a reliable, efficient way.<sup>8</sup>

10. Kingston and Phison work jointly on controller design, including in this district. Phison and Kingston have a "partnership" to make SSD controllers for Kingston products, and this partnership even "extends beyond SSDs." In November 2010, Phison and Kingston formed a joint venture to provide flash memory solutions in the mobile, Internet of Things, and embedded markets.<sup>9</sup>

11. Kingston and Phison, which act together in product design, marketing, manufacturing, and sales, have operated as agents of and for one another and have otherwise acted vicariously for each other as elements of the same business group and/or enterprise. They work together in concern and in orchestrated fashion, subject to agreements closer than arms' length, in order to implement a distribution channel of infringing products in the United States.

<sup>&</sup>lt;sup>3</sup> Ex. I, <u>https://www.kingston.com/en/ssd</u>

<sup>&</sup>lt;sup>4</sup> Ex. J, <u>https://www.kingston.com/en/usb-flash-drives</u>

<sup>&</sup>lt;sup>5</sup> Ex. K, <u>https://www.kingston.com/en/memory-cards</u>

<sup>&</sup>lt;sup>6</sup> Ex. L, <u>https://www.kingston.com/en/solutions/embedded-and-industrial</u>

<sup>&</sup>lt;sup>7</sup> Ex. I, <u>https://www.kingston.com/en/ssd</u>

<sup>&</sup>lt;sup>8</sup> Ex. M, <u>https://www.kingston.com/en/ssd/gaming/kingston-fury-renegade-nvme-m2-ssd</u> ("By leveraging the latest Gen 4x4 NVMe controller and 3D TLC NAND, Kingston FURY Renegade SSD offers blazing speeds up to 7,300/7,000MB/s read/write and up to 1,000,000 IOPS for amazing consistency and exceptional gaming experience.")

<sup>&</sup>lt;sup>9</sup> Ex. N, <u>https://www.phison.com/en/company/newsroom/press-releases/general/530-phison-and-kingston-collaborate-on-nvme-ssd-controller-to-accelerate-into-the-next-ssd-era-2</u>

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 4 of 82

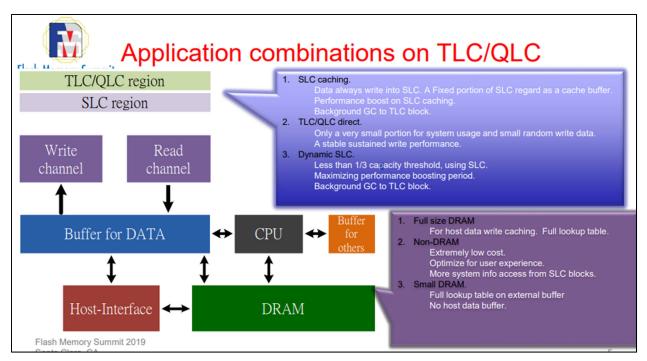

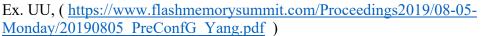

12. One of the key ways that Kingston's flash memory controllers manage the storage of data is through the use of SLC and MLC flash. For example, Phison makes many of the controllers that Kingston uses. As Imran Hirani, Phison's Director of Product Architecture, explained, the use of QLC (quad-level-cell) flash memory, a type of multi-level-cell ("MLC") flash memory, in combination with SLC (single-level-cell) memory is a key part of providing high capacity, high speed, and high endurance. "QLC NAND addresses the increased capacity requirement but comes with tradeoffs of slower throughput and lower endurance. One way to address slower throughput and lower endurance of QLC is to add a small SLC cache on the drive. Data from the host is written to the SLC cache first, and then data is moved to QLC."<sup>10</sup>

13. On information and belief, Mr. Hirani, who resides in Cedar Park, Texas, designs many of the controllers Kingston uses.<sup>11</sup>

14. Kingston has over \$16 billion in annual sales, and over 2,900 employees worldwide.<sup>12</sup>

15. Kingston sells its storage products not only to end users and customers throughout the U.S., but also to major computer and electronics manufacturers to provide the storage that manufacturers need for their products. Kingston states: "From big data, to laptops and PCs, to IoT-based devices like smart and wearable technology, to design-in and contract manufacturing, Kingston helps deliver the solutions used to live, work and play. The world's largest PC makers

<sup>&</sup>lt;sup>10</sup> Ex. O, (<u>https://phisonblog.com/qlc-nand-for-consumer-ssds-2/</u>)

<sup>&</sup>lt;sup>11</sup> Ex. P, (Imran Hirani LinkedIn profile, <u>https://www.linkedin.com/in/imran-hirani-721aa23/</u>).

<sup>&</sup>lt;sup>12</sup> Ex. Q, <u>https://media.kingston.com/kingston/company/pdf/Kingston-Technology-2022-GRI.pdf</u> at 11.

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 5 of 82

and cloud-hosting companies depend on Kingston for their manufacturing needs, and our passion fuels the technology the world uses every day."<sup>13</sup>

16. Kingston operates and owns the kingston.com website, and markets, offers, distributes, and provides technical support for its flash memory products throughout the United States including in this District.

17. Kingston develops, designs, manufactures, distributes, markets, offers to sell, or sells infringing products or services within the United States, including in this District, and otherwise purposefully directs infringing activities to this District in connection with its Austin, Texas sales staff; its kingston.com website; and its other places of business in Texas and the rest of the United States.

18. Kingston has employees in the state of Texas and this District–for example, Chuck Lantz, an Enterprise Field Account Manager based in Austin, Texas. Mr. Lantz's "[p]rimary responsibility is to identify the problems customers are facing and, most importantly, to recommend viable solutions."<sup>14</sup> On information and belief, Kingston directs Mr. Lantz to work in the Western District of Texas in order to serve Kingston's local customers in the Austin area, and to distribute products and product samples to Kingston's local customers.

19. Kingston has maintained an office at One Old Town Square, Round Rock, TX, in the Western District of Texas, and filed tax returns for its property in Texas.<sup>15</sup> In prior litigation, Kingston has declined to dispute that venue was proper in the Western District of Texas.<sup>16</sup>

<sup>&</sup>lt;sup>13</sup> Ex. Q, <u>https://media.kingston.com/kingston/company/pdf/Kingston-Technology-2022-GRI.pdf</u> at 10.

<sup>&</sup>lt;sup>14</sup> Ex. R, (<u>https://www.linkedin.com/in/chuck-lantz-a581b811/</u>).

<sup>&</sup>lt;sup>15</sup> Ex. S, (Sonrai WDTX Docket Nos. 37-24, 37-25, 37-26).

<sup>&</sup>lt;sup>16</sup> Ex. T, (Sonrai WDTX Docket No. 38 at 1, n.1).

### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 6 of 82

20. Defendants have been and are acting in concert, and are otherwise liable jointly, severally, or otherwise for relief related to or arising out of the same transaction, occurrence, or series of transactions or occurrences related to the making, using, selling, offering for sale, or otherwise distributing the flash memory products in this District.

21. In addition, this action involves questions of law and fact that are common to all Defendants. For example, Defendants are making, using, offering for sale, selling, or otherwise distributing at least some of the same flash memory products in this District.

## JURISDICTION AND VENUE

22. This is a civil action for patent infringement arising under the patent laws of the United States, 35 U.S.C. § 1 *et seq*. This Court has subject matter jurisdiction over the matters asserted in this Complaint under 28 U.S.C. §§ 1331 and 1338(a) and 35 U.S.C. §§ 271 *et seq*.

23. This Court has personal jurisdiction over Kingston in accordance with the Due Process Clause of the United States Constitution and the Texas Long Arm Statute (*see* Tex. Civ. Prac. & Rem. Code §§17.041 *et seq.*) because, among other things, (i) Kingston has done and continues to do business in Texas, (ii) Kingston "recruits Texas residents, directly or through an intermediary located in this state, for employment inside or outside this state," Tex. Civ. Prac. & Rem. Code § 17.042(3), and (iii) Kingston has committed and continues to commit, directly or through intermediaries (including subsidiaries, distributors, affiliates, retailers, suppliers, integrators, customers, and others), acts of patent infringement in this State and this District. Such acts of infringement include making, using, offering to sell, selling, and/or importing Accused Products in this State and this District. Kingston places its Accused Products into the stream of commerce through established distribution channels with the expectation and intent that such products will be sold to and purchased by consumers in the United States, this State, and this District; and with the knowledge and expectation that such products (whether in

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 7 of 82

standalone form or as integrated in downstream products) will be imported into the United States, this State, and this District.

24. Kingston, directly and through agents, regularly conducts, solicits, and transacts business in this District and elsewhere in Texas, including through its kingston.com website. For example, Defendants employ sales and marketing employees that regularly offer to sell, sell, or otherwise distribute flash memory products in this District and elsewhere in Texas.

25. In particular, Kingston has committed and continues to commit acts of infringement in violation of 35 U.S.C. § 271, and has made, used, marketed, distributed, offered for sale, and sold infringing products in Texas, including in this District, and engaged in infringing conduct within and directed at or from this District. The infringing flash memory products have been and continue to be distributed to and used in this District. Kingston's acts cause injury to Vervain, including injury suffered within this District.

26. Venue is proper in this District under 28 U.S.C. §§ 1391 and 1400(b) because a substantial part of the events or omissions giving rise to the claims occurred in this District, and because Defendants have committed acts of infringement in this District and have a regular and established place of business in this District.

27. In particular, Defendants each have regular and established places of business in this District located at the workplace of Chuck Lantz, and at their offices at located at One Old Town Square, Round Rock, TX. Furthermore, Defendants are registered to do business in Texas. Upon information and belief, Defendants instruct Mr. Lantz to work in the Western District of Texas so that he can easily meet with customers in the field, and Defendants distribute products and samples through Mr. Lantz.

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 8 of 82

28. Upon information and belief, Kingston Digital, Inc., and Kingston Technology Corporation are wholly-owned subsidiaries of Kingston Technology Company, Inc.

### **VERVAIN'S ASSERTED PATENTS**

29. U.S. Patent No. 8,891,298 (the "298 patent") is entitled "Lifetime Mixed Level Non-Volatile Memory System" and issued on November 18, 2014. A true and correct copy of the '298 patent is attached as Exhibit A to this Complaint. Vervain is the owner of all rights, title, and interest in and to the '298 patent, with the full and exclusive right to bring suit to enforce the '298 patent, including the right to recover for past infringement. The '298 patent is valid and enforceable under United States patent laws.

30. U.S. Patent No. 9,196,385 (the "385 patent") is entitled "Lifetime Mixed Level Non-Volatile Memory System" and issued on November 24, 2015. A true and correct copy of the '385 patent is attached as Exhibit B to this Complaint. Vervain is the owner of all rights, title, and interest in and to the '385 patent, with the full and exclusive right to bring suit to enforce the '385 patent, including the right to recover for past infringement. The '385 patent is valid and enforceable under United States patent laws.

31. U.S. Patent No. 9,997,240 (the "240 patent") is entitled "Lifetime Mixed Level Non-Volatile Memory System" and issued on June 12, 2018. A true and correct copy of the '240 patent is attached as Exhibit C to this Complaint. Vervain is the owner of all rights, title, and interest in and to the '240 patent, with the full and exclusive right to bring suit to enforce the '240 patent, including the right to recover for past infringement. The '240 patent is valid and enforceable under United States patent laws.

32. U.S. Patent No. 10,950,300 (the "300 patent") is entitled "Lifetime Mixed Level Non-Volatile Memory System" and issued on March 16, 2021. A true and correct copy of the '300 patent is attached as Exhibit D to this Complaint. Vervain is the owner of all rights, title,

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 9 of 82

and interest in and to the '300 patent, with the full and exclusive right to bring suit to enforce the '300 patent, including the right to recover for past infringement. The '300 patent is valid and enforceable under United States patent laws.

33. U.S. Patent No. 11,830,546 (the "'546 patent") is entitled "Lifetime Mixed Level Non-Volatile Memory System" and issued on November 28, 2023. A true and correct copy of the '546 patent is attached as Exhibit E to this Complaint. Vervain is the owner of all rights, title, and interest in and to the '546 patent, with the full and exclusive right to bring suit to enforce the '546 patent, including the right to recover for past infringement. The '546 patent is valid and enforceable under United States patent laws.

34. U.S. Patent No. 11,854,612 (the "'612 patent") is entitled "Lifetime Mixed Level Non-Volatile Memory System" and issued on December 26, 2023. A true and correct copy of the '612 patent is attached as Exhibit F to this Complaint. Vervain is the owner of all rights, title, and interest in and to the '612 patent, with the full and exclusive right to bring suit to enforce the '612 patent, including the right to recover for past infringement. The '612 patent is valid and enforceable under United States patent laws.

35. In addition, Vervain has pending continuations to the patents-in-suit, including application numbers 18/387,546 and 18/390,193. On January 22, 2024, application number 18/397,546 received a Notice of Allowance, and is published as US 2024-0071485 A1.<sup>17</sup> Vervain is the owner of all rights, title, and interest in and to these patent applications.

36. G.R. Mohan Rao is the sole inventor of the Asserted Patents.

37. Dr. Rao is the inventor of approximately 113 U.S. patents and the author of at least 15 technical publications spanning several decades.

<sup>&</sup>lt;sup>17</sup> Ex. XX, (Notice of Allowance); Ex. YY, (Claims).

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 10 of 82

38. Dr. Rao has been an innovator in the semiconductor industry since the 1960s. After receiving his Ph.D. in physics with a specialization in electronics in September 1968 from Andhra University in Waltair, India, near the village where he grew up, Dr. Rao traveled to the United States to attend a graduate program in physics at the University of Cincinnati, fulfilling his lifelong dream to study in the United States.

39. Shortly after beginning his studies at the University of Cincinnati, Dr. Rao found a bulletin indicating that Prof. William Carr of Southern Methodist University (SMU) was looking for a graduate assistant for his work on MOS transistors. Dr. Rao called Prof. Carr about the opportunity, and by December 1968, after completing the fall semester at the University of Cincinnati, Dr. Rao had received the assistantship with Prof. Carr, moved to Dallas, Texas, and enrolled in a Ph.D. program at SMU in electrical engineering.

40. At the laboratory at SMU, Dr. Rao was able to build MOS devices from scratch. In the 1969-1970 timespan, while attending SMU, Dr. Rao also worked in the SMU laboratory with Jack Kilby of Texas Instruments, a pioneering electrical engineer who would later receive a Nobel Prize for his work. In early 1972, Mr. Kilby set up an interview for Dr. Rao at Texas Instruments' Houston facility, then the home of Texas Instruments' MOS-related work.

41. Dr. Rao began working for Texas Instruments in June 1972. He would go on to work for the company for 22 years, until 1994. Dr. Rao rose through the ranks at Texas Instruments, starting in an Engineer position and ascending to the position of Senior Fellow one of 12 out of approximately 20,000 engineers at the company at the time. He then moved into a management position, starting as a Vice President in 1983 and becoming a Senior Vice President in 1985.

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 11 of 82

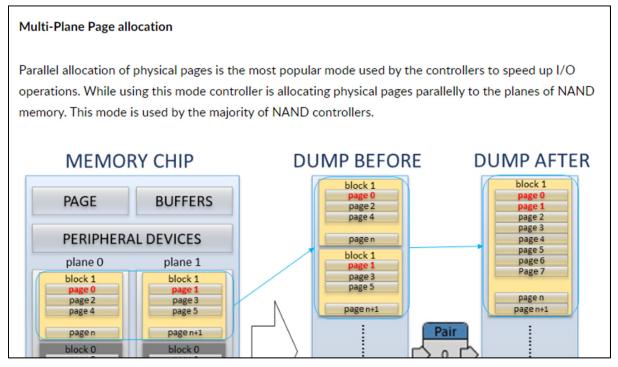

42. Dr. Rao received his first patent while working in a process and product engineering capacity to solve a production problem with Texas Instruments' 4-kilobit RAM product. From the late 1970s through the mid-1980s, he worked on and/or managed Texas Instruments': (1) 64Kb RAM, in a project management capacity as a Senior Member of Technical Staff; (2) 256Kb RAM, in a project management capacity as a Fellow; (3) 1Mb RAM, in a management capacity as a Senior Fellow, overseeing several projects; and (4) 4Mb RAM, in a management capacity as a Senior Fellow, overseeing several projects. At Texas Instruments, Dr. Rao also worked on projects involving EEPROM, SRAM, and microcontrollers. In total, Dr. Rao received approximately 35 U.S. patents during his time at Texas Instruments.

43. Some of Dr. Rao's work for Texas Instruments is featured in the Smithsonian Institution, in the Texas Instruments Collection.<sup>18</sup> For example, the Smithsonian Institution has a display of Texas Instruments' experimental 1-megabit CMOS DRAM with one-micron feature size, produced in April 1985 under Dr. Rao's leadership.

44. After his time at Texas Instruments, Dr. Rao joined Cirrus Logic in 1994. Although Cirrus Logic was a California company, Dr. Rao coordinated a team in the Dallas area. His work focused on a major project involving integration of a graphics controller and memory. During his time at Cirrus Logic, Dr. Rao received approximately 22 U.S. patents relating to his work on integrated graphics controllers and memory. Dr. Rao left Cirrus Logic in the summer of 1996.

<sup>&</sup>lt;sup>18</sup> <u>http://smithsonianchips.si.edu/texas/t\_360.htm;</u> <u>http://smithsonianchips.si.edu/texas/wafer.htm.</u>

### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 12 of 82

45. Later in 1996, Dr. Rao started a company called Silicon Aquarius. Through a relationship between Silicon Aquarius and Matsushita, Dr. Rao led a design team in working on a 256Mb DRAM chip.

46. After Silicon Aquarius ceased operations, Dr. Rao did consulting work for a number of different companies and devoted much of his free time to thinking about various challenges and problems with which the semiconductor industry had struggled for years. For example, Dr. Rao worked to improve non-volatile memories that are used for long term storage of data after the power is turned off, and how to reduce the power consumption of those devices.

47. In non-volatile memories, there are two types of storage cells: single-level cells (SLCs) that store one bit of information, and multi-level cells (MLCs) that store multiple bits of information. SLCs are faster, more reliable, and have a longer life. MLCs are less expensive and can store more data in less space with less power consumption. While working to improve these non-volatile memories, Dr. Rao developed inventions that combine the long life and high-performance of SLCs with the more cost-effective MLCs. The result is the best of both types of cells – longer life and better performance at less cost. By using the MLCs as the default storage, the cheaper, more reliable MLCs are used for the bulk of the data storage. Meanwhile, the SLCs are used for the data that needs it the most.

48. The claims of the Asserted Patents are directed to patent-eligible, non-abstract ideas. They address, among other things, specific improvements for controlling non-volatile memory modules. The claims are particularly useful for flash memory products or other memory devices that use a combination of SLCs and multi-level cells MLCs. If, for example, a range of addresses in a MLC memory module fails a data integrity test, the range of addresses may be mapped to a new range of addresses in a SLC memory module. Also, if a block in the

### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 13 of 82

MLC module is used frequently, the block may be transferred to the SLC module. By doing so, the reliability and life of the flash memory is increased.

49. Vervain's Asserted Patents claim, among other things, a specific implementation of a solution to a problem in the design and fabrication of flash memories. For example, the patents identify numerous specific advantages that Vervain's claimed techniques provide compared to traditional forms of flash memories. *See, e.g.*, Ex. A, '298 patent at 1:25-32; Ex. B, '385 patent at 1:28-35; Ex. C, '240 patent at 1:40-47; Ex. D, '300 patent at 1:44-51. Further, the claimed technologies cannot be performed as mental steps by a human, nor do they represent the application of a generic computer to any well-known method of organizing human behavior.

50. The Asserted Patents claim inventive concepts that are significantly more than any patent-ineligible, abstract idea. In particular, the claimed technologies, including individual limitations as well as ordered combinations of limitations, were not well-understood, routine, or conventional, and cover multiple advantages, and combinations of advantages, that were not well-understood, routine, or conventional. *See, e.g.*, Ex. A, '298 patent at 5:24-40, 6:24-35; Ex. B, '385 patent at 5:28-44, 6:28-39; Ex. C, '240 patent at 5:43-59, 6:46-58; Ex. D, '300 patent at 5:51-67, 6:53-65.

## KINGSTON'S INFRINGING PRODUCTS AND ACTIVITIES

51. Kingston is a global manufacturer and supplier of memory products, including non-volatile memory products. Kingston's flash memory products, such as solid state drives (SSDs),<sup>19</sup> USB flash drives,<sup>20</sup> memory cards such as SD and microSD,<sup>21</sup> and embedded flash products like eMMC and UFS,<sup>22</sup> are managed by a controller chip. Many of Kingston's

<sup>&</sup>lt;sup>19</sup> Ex. I, <u>https://www.kingston.com/en/ssd</u>

<sup>&</sup>lt;sup>20</sup> Ex. J, <u>https://www.kingston.com/en/usb-flash-drives</u>

<sup>&</sup>lt;sup>21</sup> Ex. K, <u>https://www.kingston.com/en/memory-cards</u>

<sup>&</sup>lt;sup>22</sup> Ex. L, <u>https://www.kingston.com/en/solutions/embedded-and-industrial</u>

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 14 of 82

controller chips are made by companies like Phison and Silicon Motion. For example, the exemplary products listed below have the controllers listed below:

| Drive                                   | Controller <sup>23</sup>            |

|-----------------------------------------|-------------------------------------|

| XS2000 External Solid State Drive (SSD) | Silicon Motion SM2320 <sup>24</sup> |

| DC1500M U.2 Enterprise SSD              | Silicon Motion SM2270 <sup>25</sup> |

| DC1000B M.2 NVMe SSD                    | Phison PS5012-E12 <sup>26</sup>     |

| NV2                                     | Phison E21T or Silicon              |

|                                         | Motion SM2267XT                     |

| NV1                                     | Phison 13T or Silicon               |

|                                         | Motion SM2263XT                     |

| HyperX Savage                           | Phison S10                          |

| A400                                    | Phison S11                          |

| A1000                                   | Phison E8                           |

| A2000                                   | Silicon Motion                      |

|                                         | SM2263EN                            |

| DC500M                                  | Phison E12                          |

| DC500R                                  | Phison S12                          |

| FURY Renegade                           | Phison E18                          |

<sup>&</sup>lt;sup>23</sup> Based on Ex. U, https://www.techpowerup.com/ssd-specs/#kingston, or Ex. V,

<sup>26</sup> Ex. Y, <u>https://www.kitguru.net/components/ssd-drives/simon-crisp/kingston-dc1000b-480gb-ssd-review/all/1/</u>

https://www.johnnylucky.org/data-storage/ssd-database.html, pages 10, 21, unless otherwise indicated.

<sup>&</sup>lt;sup>24</sup> Ex. W, <u>https://www.thessdreview.com/hardware/portable-ssds/kingston-xs2000-1tb-portable-ssd-review/</u>

<sup>&</sup>lt;sup>25</sup> Ex. X, <u>https://www.kitguru.net/components/ssd-drives/simon-crisp/kingston-dc1500m-3-84tb-ssd-review/all/1/</u>

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 15 of 82

| KC400  | Phison S10            |

|--------|-----------------------|

| KC600  | Silicon Motion        |

|        | SM2259H               |

| KC3000 | Phison E18            |

| KC2500 | Silicon Motion        |

|        | SM2262EN              |

| A2000  | Silicon Motion SM2263 |

| KC2000 | Silicon Motion        |

|        | SM2262EN              |

| KC1000 | Phison PS5007-E7      |

52. Kingston designs, makes, uses, offers to sell, sells, imports, supplies, or otherwise distributes, and provides support for, flash memory products, including the exemplary products listed above, as well as other SSDs, flash drives, memory cards, embedded flash products, or other flash products that have the same or similar structures, features, or functionalities as the aforementioned products ("Accused Products").

53. The Accused Products are integrated into devices made, used, offered for sale, sold, imported, supplied, or otherwise distributed in the United States by among others, Kingston, Kingston's customers, original equipment manufacturers ("OEMs"), original design manufacturers ("ODMs"), foundry suppliers, distributors, retailers, and other third parties. Kingston's Accused Products are essential, non-trivial components of the products into which they are integrated.

### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 16 of 82

54. Kingston also conducts research, development, and testing of Accused Products in the United States.

55. Kingston maintains a website that advertised and continues to advertise the Accused Products, including identifying the applications for which they can be used and specifications for the Accused Products.

56. Kingston's development, sales, marketing, and manufacturing activities in the United States, including within this District, directly contributed to Kingston's net revenue in the United States.

## COUNT I: INFRINGEMENT OF U.S. PATENT NO. 8,891,298

57. Vervain incorporates by reference and re-alleges all of the foregoing paragraphs of this Complaint as if fully set forth herein.

58. Kingston has directly infringed and continue to infringe, either literally or under the doctrine of equivalents, at least claim 1 of the '298 patent by making, using, offer for sale, selling, and importing, without authority or license, the Accused Products in violation of 35 U.S.C. § 271(a). The Accused Products are non-limiting examples that were identified based on currently available information, and Vervain reserves the right to identify additional infringing activities, products, and services, including, for example, on the basis of information obtained during discovery.

59. The Accused Products meet all the limitations of at least claim 1 of the '298 patent. Specifically, claim 1 of the '298 patent recites:

A system for storing data comprising:

at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks;

at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks; and

a controller coupled to the at least one MLC non-volatile memory module and the at least one SLC non-volatile memory module wherein the controller is adapted to:

- a) maintain an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC nonvolatile memory module;

- b) determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module;

- c) determine which of the blocks of the plurality of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed; and

- d) allocate those blocks that receive the most frequent writes by transferring the respective contents of those blocks to the at least one SLC non-volatile memory module.

- 60. To the extent the preamble is a limitation, the Accused Products include a system

for storing data. For example, Kingston's SSDs and other flash storage products are all systems

for storing data.

Ex. I, https://www.kingston.com/en/ssd

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 18 of 82

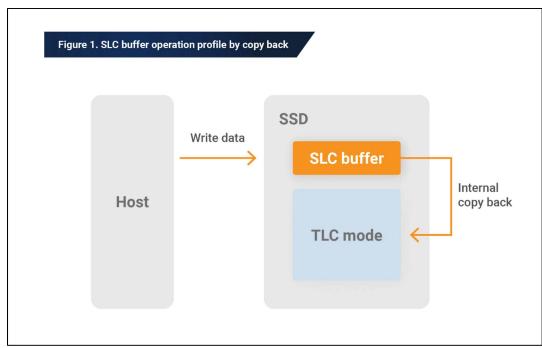

61. The Accused Products include at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks. For example, Kingston's Phison-based products use MLC (e.g. "TLC mode") memory as part of an SLC buffering system, and Kingston's Silicon Motion-based products use "Direct-to-TLC" and "SLC Caching" systems that include MLC memory.

Ex. Z, https://phisonblog.com/the-benefits-of-using-slc-buffers-with-ssds-2/

Leveraging Silicon Motion's proprietary NANDXtend<sup>™</sup> error-correcting code (ECC) technology, the SM2259 and SM2259XT enhance the endurance and retention of 3D NAND. Besides, SM2259 and SM2259XT include such enterprise features such as end-to-end data path protection and SRAM ECC capabilities to ensure the data integrity and reliability. SM2259 and SM2259XT also features advanced Direct-to-TLC and SLC Caching algorithms for optimal sustained performance with TLC and QLC NAND.

Ex. AA, https://www.siliconmotion.com/download/q/a/SM2259\_XT\_PB\_EN\_201910.pdf

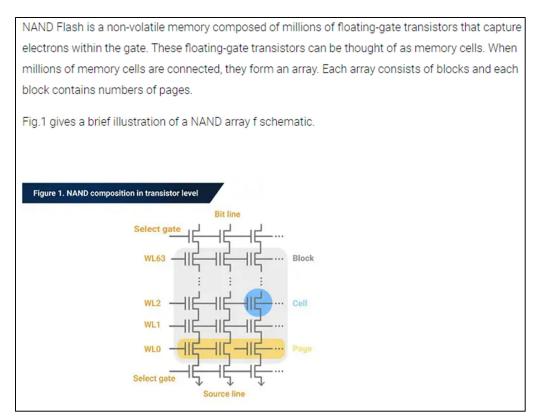

62. The flash memory uses individually erasable blocks. For example, Phison explains that individual blocks are erased, and that this is an "intrinsic characteristic of NAND device physics":

A flash memory cell is composed of pages, and pages form a block. Due to the intrinsic characteristic of NAND device physics, the flash cell allows data to be programmed on a page level but only erased on a block level. This inconsistency between program and erase tasks is the major impact on SSD endurance.

## Ex. BB, (https://phisonblog.com/ssd-garbage-collection/)

63. The Accused Products include at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks. The SLC caching systems, for example, used by the Accused Products use individually erasable SLC blocks.

|      | SSD        |  |            |   |                       |

|------|------------|--|------------|---|-----------------------|

|      | Write data |  | SLC buffer |   | 1                     |

| Host |            |  |            |   | Internal<br>copy back |

|      |            |  | TLC mode   | ← |                       |

|      |            |  |            |   |                       |

|      |            |  |            |   |                       |

Ex. Z, https://phisonblog.com/the-benefits-of-using-slc-buffers-with-ssds-2/

Leveraging Silicon Motion's proprietary NANDXtend<sup>™</sup> error-correcting code (ECC) technology, the SM2259 and SM2259XT enhance the endurance and retention of 3D NAND. Besides, SM2259 and SM2259XT include such enterprise features such as end-to-end data path protection and SRAM ECC capabilities to ensure the data integrity and reliability. SM2259 and SM2259XT also features advanced Direct-to-TLC and SLC Caching algorithms for optimal sustained performance with TLC and QLC NAND.

Ex. AA, https://www.siliconmotion.com/download/q/a/SM2259\_XT\_PB\_EN\_201910.pdf

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 20 of 82

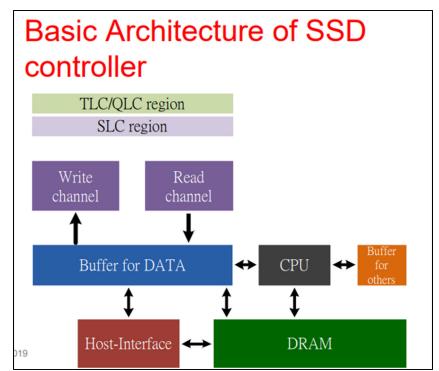

64. The Accused Products include a controller coupled to the at least one MLC nonvolatile memory module and the at least one SLC non-volatile memory module. For example, the exemplary products listed in the table in Paragraph 51 above include the listed controllers.

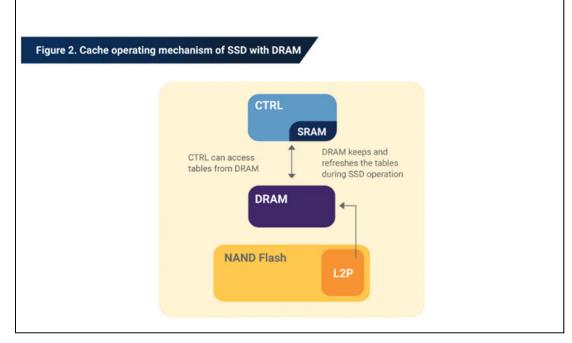

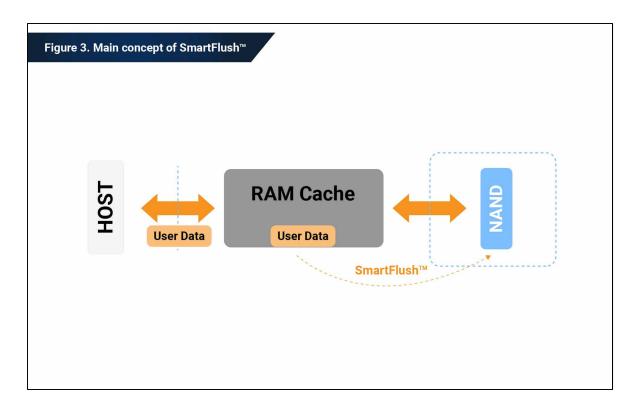

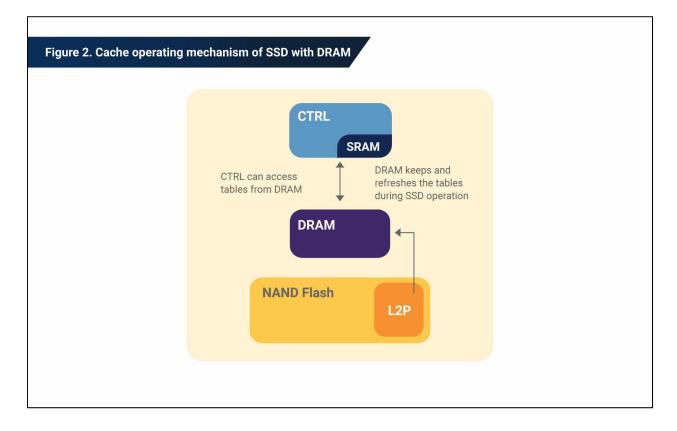

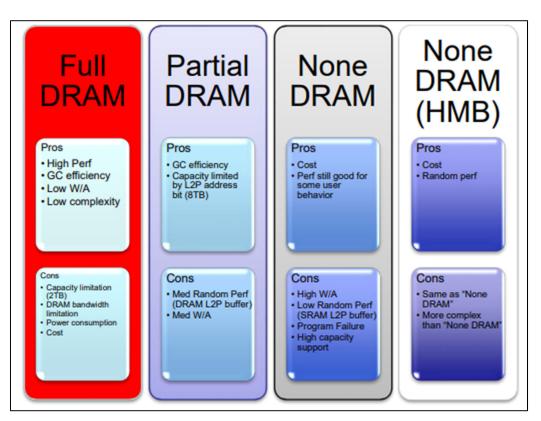

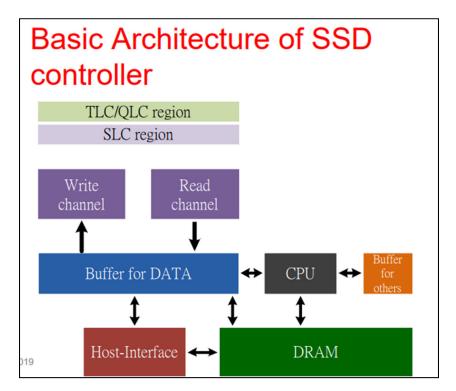

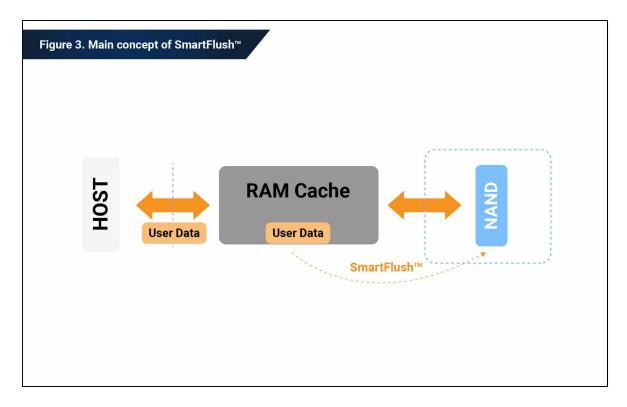

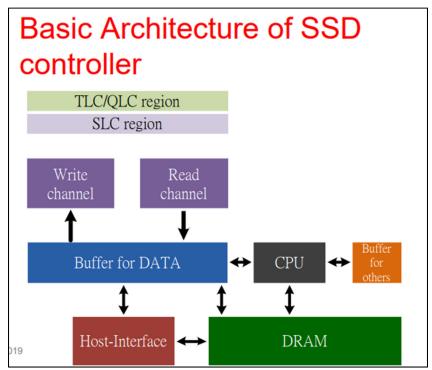

65. The Accused Products include a controller coupled to the at least one MLC nonvolatile memory module and the at least one SLC non-volatile memory module wherein the controller is adapted to maintain an address map of at least one of the MLC and SLC nonvolatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC non-volatile memory module. For example, Phison and Silicon Motion controllers in the Accused Products uses a mapping table such as an L2P (logical-to-physical) table to keep track of the relationship between the logical blocks and the physical addresses of the flash memory.

66. Phison controllers use an L2P table:

# Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 21 of 82

The most important information that gets cached to or retrieved from a DRAM is the mapping information that turns logical addresses into the physical locations of stored data within the NAND flash array. This information is stored in mapping tables called L2P (logical-to-physical) tables and is updated frequently as SSDs move data in and out of flash storage. During shutdowns, the L2P table is stored in flash memory, since DRAM quickly becomes inoperable without a continuous power supply.

Ex. CC, https://phisonblog.com/host-memory-buffer-2/

67. In Phison controllers, a minimum quanta of addresses—such as a page—is used:

# Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 22 of 82

Ex. DD, https://phisonblog.com/ensuring-data-correctness-with-phisons-guaranteedflush-2/

68. Silicon Motion controllers provide logical-to-physical translation:

DRAM cache with data redundancy: no data loss during data transfers Silicon Motion's new PCIe FerriSSD features an embedded DRAM which has a self-error detection and correction code (ECC) capability. This DRAM provides for secure, frequent read/write cache requests, and stores logical-to-physical address mapping information.

Ex. EE,

https://www.siliconmotion.com/download/3Ta/a/PCIe\_FerriSSD\_Industrial\_Embedded\_Applica\_tions\_WP\_EN.pdf

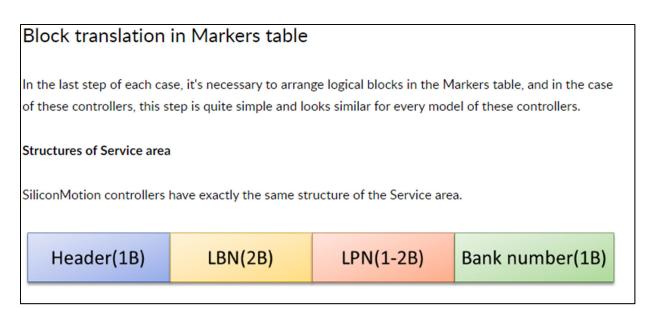

69. Silicon Motion's address map may take the form of a table:

Ex. FF, https://support.rusolut.com/portal/en/kb/articles/silicon-motion-data-recovery

70. In Silicon Motion's address map, a minimum quanta of addresses—such as a

page—is mapped to physical locations:

Ex. FF, https://support.rusolut.com/portal/en/kb/articles/silicon-motion-data-recovery

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 24 of 82

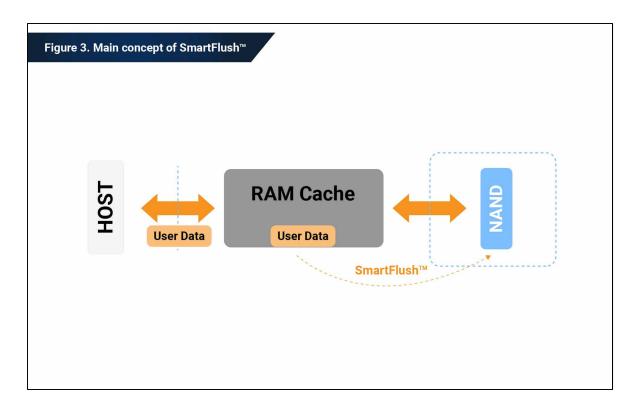

71. The Accused Products include a controller coupled to the at least one MLC nonvolatile memory module and the at least one SLC non-volatile memory module wherein the controller is adapted to determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module. For example, Kingston's products include Phison and Silicon Motion controllers that incorporate defect and error management technology, and use a variety of tests to determine that there is a data integrity problem.

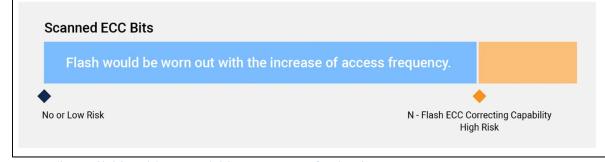

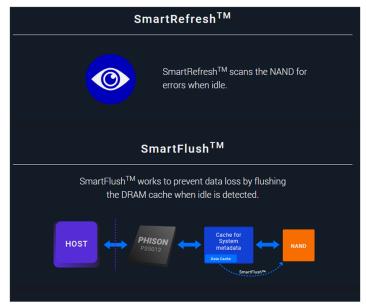

72. Phison controllers use a variety of data integrity tests to determine when there is a data integrity problem:

# Phison's SmartRefresh<sup>™</sup> technology

To protect the data stored in an SSD, Phison developed a proprietary technology called SmartRefresh<sup>™</sup> that uses two primary methodologies:

- 1. Dynamic Error Bit Monitoring (DEBM)

- 2. Read Retry

"Phison's embedded firmware runs in the background to check the error bit of each block. Once there is a block fail within the criteria set by our firmware (i.e., the number of error bits is over the threshold decided in advance), the firmware performs specific actions on this failed block to guarantee the integrity of user data."

Ex. GG, (https://phisonblog.com/phisons-smartrefresh-2/)

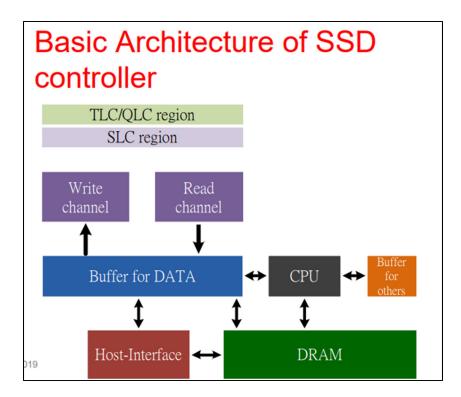

# Advanced Features:

- End-to-end data path protection

- SmartECC RAID data protection

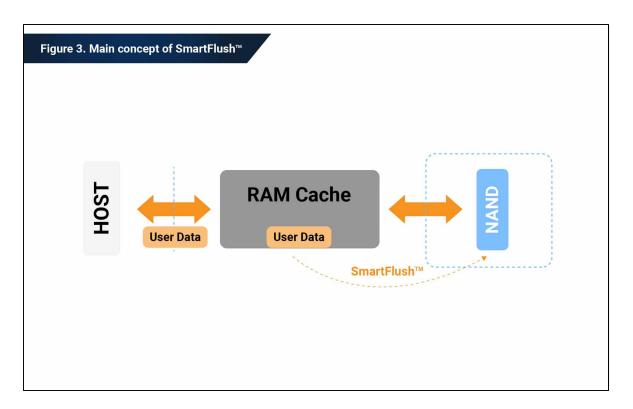

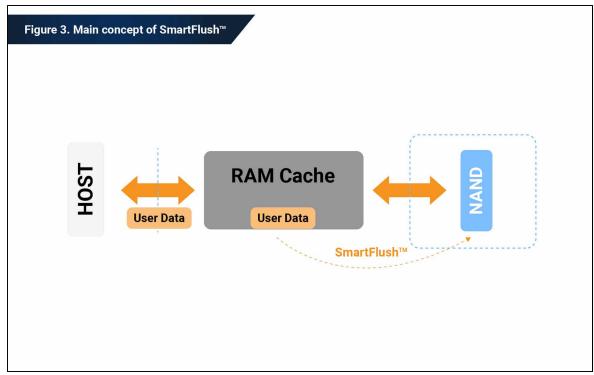

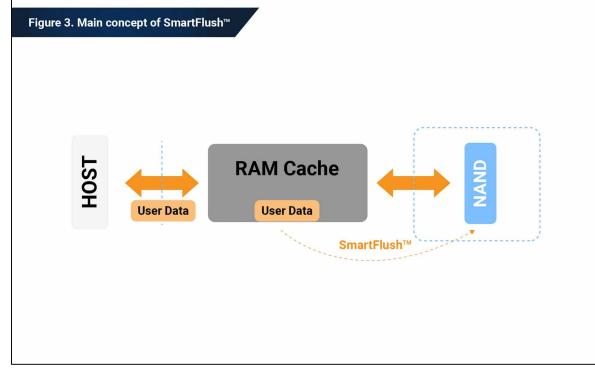

- P-fail protection with SmartFlush and GuaranteedFlush technology

- Advanced read disturb management with SmartRefresh technology

- Advanced global wear-leveling

Ex. HH, (<u>https://www.techpowerup.com/203889/phison-announces-quad-core-ps3110-sata-iii-ssd-controller</u>)

73. Upon a data integrity failure, Phison controllers remap degraded data to the next

available location:

"the firmware performs specific actions on this failed block to guarantee the integrity of user data."

Ex. GG, (https://phisonblog.com/phisons-smartrefresh-2/)

# Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 26 of 82

Ex. II, (https://www.phison.com/en/technologies/ftl)

74. In particular, Phison controllers move data from MLC to SLC as part of the relocation above as part of Phison's SLC caching technology, where writes are made to SLC before being moved to MLC:

Consumer workloads also write over a limited LBA range. W riting the data to SLC first ensures that only the final valid copy of the data is written to the QLC. This limits the writes to QLC, enabling QLC NAND to be used for consumer drive, despite its lower endurance.

SLC cache is used in the consumer TLC drive today. It takes advantage of customer workloads to address the similar limitation of lower speed and limited endurance on TLC NAND. QLC based drives provide 33% higher capacity as compared to TLC NAND. This lowers the cost of the drive.

Ex. O, (https://phisonblog.com/qlc-nand-for-consumer-ssds-2/)

75. For example, Phison's articles describing its storage devices discuss "replacing

## MLC to SLC":

With process advances, NAND Flash can support the development of more cost-competitive solutions but the reliability of NAND Flash is getting worse. In terms of market response, customers won't just accept inferior quality products because of the price drop. On the contrary, they demand products at the same level but with the same or better reliability and performance. Therefore, the focus of attention has turned to the Flash controller to address this problem.

Basically, significant problems of reliability are caused by things like replacing MLC to SLC, increasing 2 bits/cell to 3 bits/cell, reducing the Erase Cycle number from 100K down to 10K, and cutting Data Retention times through the advances of NAND Flash. These issues can be solved within a re-designed and robust controller.

For example the error rates of NAND Flash are increasing

Ex. JJ, (https://www2.advantech.com/embcore/promotions/whitepaper/PHISON%20Electronics-The\_Stability\_and\_Reliability\_of\_Storage\_Devices.pdf)

76. Silicon Motion controllers use a variety of data integrity tests to determine when

there is a data integrity problem:

# Full end-to-end data path protection: no bit errors sent to host

Conventional SSDs may employ error detection and correction circuitry at the far ends of the data path: at the front-end host interface and at the back-end NAND interface. This omits an important gap at the internal SRAM and/or DRAM transfer buffers, and other circuit paths. Data errors that occur between the NAND interface and the host, such as soft error bits, are often extremely difficult to identify and duplicate.

While conventional SSDs may have some internal error detection circuitry, the new PCIe FerriSSD storage solutions incorporate full data recovery engines to provide enhanced data integrity throughout the entire Host-to-NAND-to-Host data path.

The PCIe FerriSSD data recovery algorithm can effectively detect any error in the SSD data path, including hardware errors, firmware errors and memory errors arising in SRAM, DRAM or NAND. The PCIe FerriSSD implements an additional redundant back-up in NAND – the SMI Ferri Group Page Raid – which reinforces the protection against the risk of uncorrectable error in the NAND storage medium.

Ex. EE,

(https://www.siliconmotion.com/download/3Ta/a/PCIe\_FerriSSD\_Industrial\_Embedded\_Applic ations\_WP\_EN.pdf)

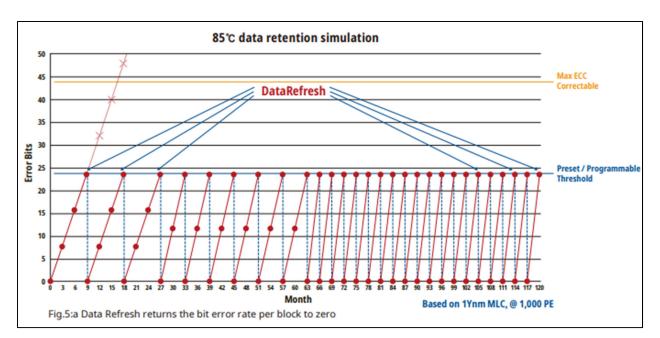

> IntelligentScan & DataRefresh: proactive data loss prevention measures

The features described above protect against the risk of data loss or error in data-transfer operations. The PCIe FerriSSD also incorporates sophisticated functions which ensure the integrity of data in storage. The IntelligentScan & DataRefresh function achieves this by identifying at-risk memory cells and refreshing the data stored in them. The risk of loss of stored data increases as:

- the aggregate number of Program / Erase (P/E) cycles increases

- the ambient temperature rises

In either condition, the operation of the IntelligentScan & DataRefresh function becomes increasingly important.

# Read disturbance

Performing an excessive number of read cycles from a cell, can cause unintended over-charging of adjacent cells, leading to unrecoverable bit errors, a phenomenon known as Read disturbance. FerriSSD products avoid potential Read disturbance errors by performing periodic IntelligentScan & DataRefresh operations on NAND blocks that undergo repetitive Read cycles. The PCIe FerriSSD firmware – an advanced 4th generation algorithm (IntelligentScan) – automatically manages DataRefresh cycles and processing time to minimize data loss due to the impact of intensive Read operations on the NAND Flash storage medium.

# Ex. EE,

(https://www.siliconmotion.com/download/3Ta/a/PCIe\_FerriSSD\_Industrial\_Embedded\_Applic ations\_WP\_EN.pdf)

The IntelligentScan function is responsible for checking whether the stored charge has declined below its threshold value. If it has, it reads out the data bit and rewrites it via the ECC engine, and DataRefresh recharges the cell to restore the NAND cell's voltage to the correct level.

Ex. KK, (https://www.siliconmotion.com/download/3g1/a/FerriSSD\_Gaming\_WP\_EN.pdf)

With Intelligent Scan, FerriSSD's firmware will respond to changing usage conditions to intelligently determine where, when and how frequently to scan the SSD. The scan will be triggered during idle time, based on preset thresholds and self-adopting algorithms, to determine which cells should be scanned according to severity priority (such as temperature readings, read counts, and other factors).

When IntelligentScan identifies overstressed cells, SMI's proprietary DataRefresh function will be activated automatically to recharge, repair or retire the cell block accordingly. As a result of the combination of Intelligent Scan and Data Refresh, FerriSSD can prolong its usage life much beyond typical NAND specifications.

## Ex. LL, (https://www.siliconmotion.com/download/3TY/a/FerriSSD\_BGASSD\_WP\_EN.pdf)

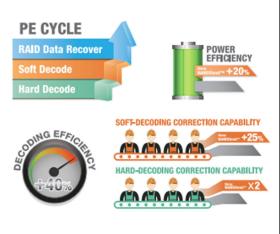

## NANDXtend<sup>™</sup> Technology

The SM2259 and SM2259XT employs the company's proprietary NANDXtend<sup>™</sup> ECC technology consisting of LDPC hard and soft decoding as well as RAID protection that together enhance the P/E cycles of 3D NAND -

extending the SSD lifespan and ensuring data integrity. The new generation NANDXtend<sup>™</sup> includes 2KB LDPC engine with advanced firmware algorithm delivers higher power efficiency, decoding efficiency and correction capability to maintain consistent data throughout and provide a better user experience, even as error bits increase throughout the product lifecycle of NAND Flash.

Ex. AA, (https://www.siliconmotion.com/download/q/a/SM2259 XT PB EN 201910.pdf)

Silicon Motion's SM689 and SM681 FerriSSDs supports enhanced reliability and data integrity features for use in demanding automotive, commercial, enterprise and industrial applications. Its set of features includes:

- End-to-end data path protection, which applies error correction code (ECC) to the SSD's SRAM and DRAM buffers as well as to the primary NAND Flash memory array

- DRAM data cache to ensure data programming and enable data redundancy, without delaying host processor operations

- Hybrid Zone which enables a single disk to be partitioned into single-level cell (SLC) and multi-level cell/three-level cell (MLC/TLC) zones, enabling faster access speeds and data retention

- Intelligent Scan/DataRefresh protects against the higher data loss from operating at high temperatures

- NANDXtend<sup>™</sup> technology incorporating Silicon Motion's proprietary 4<sup>th</sup> generation high-performance LDPC ECC engine with RAID, ensuring better data integrity even in extreme physical environments

Ex. MM, (https://www.prnewswire.com/news-releases/silicon-motion-announces-worlds-first-pcie-nvme-single-chip-ssds-with-enterprise-grade-data-protection-features-300604092.html)

# End to End Data Path Protection

Silicon Motion's SSD controller solutions incorporate full data error detection with recovery engines to provide enhanced data integrity throughout the entire Host-to-NAND-to-Host data path. The data recovery algorithm can effectively detect any error in the SSD data path, including hardware (i.e. ASIC) errors, firmware errors, and memory errors arising in SRAM, DRAM, or NAND.

Ex. NN, (https://www.siliconmotion.com/products/client/detail)

77. Upon a data integrity failure, Silicon Motion controllers remap (or "refresh") the

data to the next available location:

The IntelligentScan & DataRefresh function achieves this by identifying at-risk memory cells and refreshing the data stored in them. The risk of loss of stored data increases as:

Ex. EE,

(https://www.siliconmotion.com/download/3Ta/a/PCIe\_FerriSSD\_Industrial\_Embedded\_Applic ations\_WP\_EN.pdf).

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 32 of 82

## Ex. OO,

(https://www.siliconmotion.com/download/3TZ/a/Ferri Family\_Optimizes\_Embedded\_WP\_EN. pdf) (showing that when data integrity test shows error bits exceed a threshold, the data is rewritten to new blocks and that the error rate returns to zero).

78. In particular, Silicon Motion controllers may move data from MLC to SLC as part

of the relocation above as part of Silicon Motion's SLC caching technology. Further, Silicon

Motion's system also moves data to SLC for emergency shutdown operations, which may be

considered a response to a failure of a data integrity test (such as power loss that jeopardizes

data):

Without foregoing the density benefits of MLC/TLC, single NAND die SSDs can still maintain fast Write

SLC memory, which is ideal for emergency power shutdown operations. Without a portion of memory implemented as SLC, both the cost and the size of battery storage needed for MLC/TLC power shutdown would increase. The implementation of

Ex. EE,

https://www.siliconmotion.com/download/3Ta/a/PCIe\_FerriSSD\_Industrial\_Embedded\_Applica\_tions\_WP\_EN.pdf

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 33 of 82

79. The Accused Products include a controller coupled to the at least one MLC nonvolatile memory module and the at least one SLC non-volatile memory module wherein the controller is adapted to determine which of the blocks of the plurality of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed. For example, Kingston's products use controllers, such as Phison or Silicon Motion controllers, that employ various types of block counting.

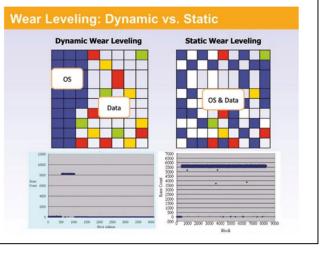

80. For example, Phison controllers use count data, such as program/erase counts and valid page counts, to maintain a count of the number of times each one of the blocks is accessed:

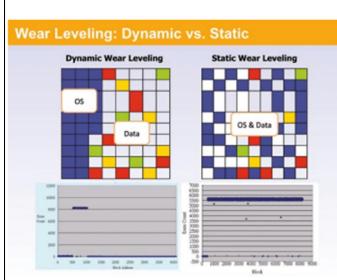

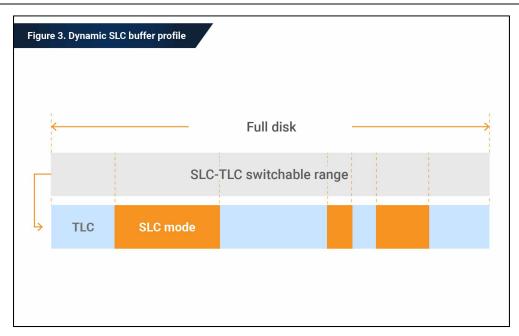

## Dynamic SLC buffer (D3)

A dynamic SLC buffer used with TLC flash, meaning that the SLC buffer in zone D3 zone can dynamically use the TLC flash by erasing the count balance scheme. The SSD firmware configures to select the block with the lowest erase count every time the dynamic SLC buffer is processed. The dynamic SLC buffer can be automatically disabled using FW calculations based on flash endurance for different flash types.

Ex. Z, https://phisonblog.com/the-benefits-of-using-slc-buffers-with-ssds-2/

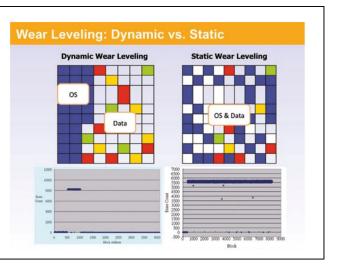

In addition, decreasing the Erase Count has brought about a shorter life expectancy of NAND Flash. The wear leveling mechanism of the controller can resolve this problem. NAND Flash consists of many blocks and each block has its certain life span. The number of erasable cycles represented the block life-expectancy and was called the Erase Count. In order to extend the lifetime of NAND Flash, we have to balance the Erase Count of all blocks. With a wear leveling mechanism implemented, the controller can achieve this goal to average the Erase Count of each block.

"A memory management method, and a memory control circuit unit and a memory storage apparatus using the same are provided. The method includes associating physical erasing units with a data area or a spare area, configuring a plurality of logical addresses for mapping to the physical erasing units, and obtaining a garbage collection threshold based on a plurality of valid logical addresses among the logical addresses, and the physical erasing units mapping to the valid logical addresses are associated with the data area. The method further includes performing a garbage collection operation on the data area if the number of the physical erasing units associated with the data area is no less than the garbage collection threshold."

Ex. PP, U.S. Pat. App. Pub. No. 2019/0073298, Abstract.

81. For example, Silicon Motion controllers use count data, such as program/erase

(P/E) counts and valid page counts, to maintain a count of the number of times each one of the

blocks is accessed:

Effect of temperature on data retention One of the most significant inhibitors to data retention is elevated NAND temperature – the higher the ambient working temperature, the shorter the retention capability of the NAND itself. The PCIe FerriSSD incorporates a Silicon Motion patent-pending monitoring algorithm which logs cumulative junction temperature readings, the number of P/E cycles, SSD power on-time, and other essential reference points to dynamically select and prioritize which NAND cells to DataRefresh, and when.

# Ex. EE,

https://www.siliconmotion.com/download/3Ta/a/PCIe\_FerriSSD\_Industrial\_Embedded\_Applica\_tions\_WP\_EN.pdf

Armed with Silicon Motion's proprietary IntelligentScan & DataRefresh, FerriSSD will intelligently activate a self-scanning feature to prevent potential data lost before it occurs; the self-scan frequency will be intelligently adjusted by ambient temperature, erase count, read count, and associated factors. FerriSSD's

Ex. LL, https://www.siliconmotion.com/download/3TY/a/FerriSSD\_BGASSD\_WP\_EN.pdf

"In the control method, by establishing a valid page count table, a detailed valid page count table and/or a zone valid page count table according to deallocate command from the host device, the flash memory controller can efficiently and quickly determine if any one of the zones does not have any valid data, so that the flash memory controller can recommend the host device to send a reset command to reset the zone. In addition, after receiving the reset command from the host device, the flash memory controller can use a garbage collection operation or directly put the blocks corresponding to the erased zone into a spare block pool, for the further use."

Ex. QQ, U.S. Patent 11,809,328, Abstract; see also Ex. RR, U.S. Patent App. Pub. No. 2023/0350799, Abstract (describing valid page count table).

82. The Accused Products include a controller coupled to the at least one MLC non-

volatile memory module and the at least one SLC non-volatile memory module wherein the

controller is adapted to allocate those blocks that receive the most frequent writes by transferring

the respective contents of those blocks to the at least one SLC non-volatile memory module. For

example, the controller (for example, a Phison or Silicon Motion controller) transfers the

contents of those blocks that receive the most frequent writes to SLC memory.

83. Phison controllers move frequently accessed data to SLC NAND. A "count

balance scheme" is used to transfer frequently written blocks to SLC, and blocks are switchable

between SLC and TLC:

# Dynamic SLC buffer (D3)

A dynamic SLC buffer used with TLC flash, meaning that the SLC buffer in zone D3 zone can dynamically use the TLC flash by erasing the count balance scheme. The SSD firmware configures to select the block with the lowest erase count every time the dynamic SLC buffer is processed. The dynamic SLC buffer can be automatically disabled using FW calculations based on flash endurance for different flash types.

Ex. Z, https://phisonblog.com/the-benefits-of-using-slc-buffers-with-ssds-2/

# 84. In addition, garbage collection can relocate frequently accessed data based on a

## page count:

For random writes, the main issue is invalid pages. Whenever garbage collection engages, the controller needs to write valid pages to other unused blocks. With the background read/write and Host read/write requests, the overall drive performance degrades.

Ex. SS, https://phisonblog.com/using-overprovisioning-with-ssds-2/

85. Phison also uses a "double rotation" scheme to move data to SLC blocks:

Therefore, controllers are using many sophisticated functions to protect stored data. We can observe these results during our daily work, many steps have to be applied before data will be recovered and almost every operation, we reverse, is applied to protect user data as well as possible.

In this article, we would like to bring closer SLC blocks topic and present to you the solution for Phison controllers which are using double rotation mode.

How to recognize that controller uses double rotation?

How to reverse this type of rotation?

How to pull out data from the SLC block?

All this information you will find in this article.

In the example below we have a dump from a micro SD card equipped with a Phison controller. We've used static rotation, but despite, that the rotation element is attached, we could not access the file system.

🚜 || ∓

Visual Nand Reconstructor - phison double rotation

D X

## Ex. TT, https://support.rusolut.com/portal/en/kb/articles/no-pic-no

86. Phison's articles discuss "replacing MLC to SLC":

With process advances, NAND Flash can support the development of more cost-competitive solutions but the reliability of NAND Flash is getting worse. In terms of market response, customers won't just accept inferior quality products because of the price drop. On the contrary, they demand products at the same level but with the same or better reliability and performance. Therefore, the focus of attention has turned to the Flash controller to address this problem.

Basically, significant problems of reliability are caused by things like replacing MLC to SLC, increasing 2 bits/cell to 3 bits/cell, reducing the Erase Cycle number from 100K down to 10K, and cutting Data Retention times through the advances of NAND Flash. These issues can be solved within a re-designed and robust controller.

For example, the error rates of NAND Flash are increasing

Ex. JJ, (https://www2.advantech.com/embcore/promotions/whitepaper/PHISON%20Electronics-The Stability and Reliability of Storage Devices.pdf)

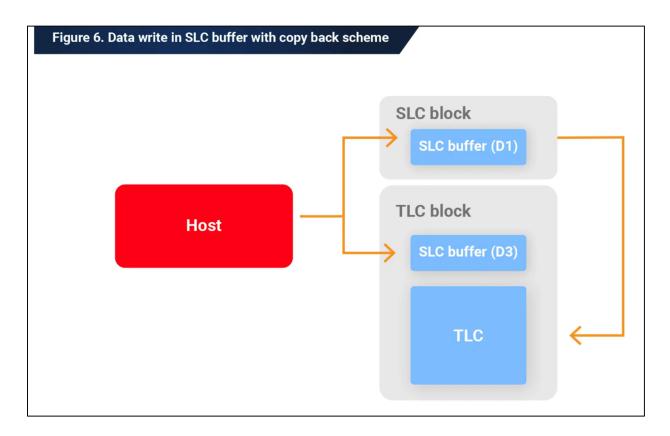

87. Phison's controllers have a copyback scheme where data is moved between SLC

and TLC blocks; with this scheme, data being rewritten as part of garbage collection may be

## Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 38 of 82

moved from TLC to SLC. For example, Phison's blog explains that "When an SSD uses copy back, host data moves into zone D1," where D1 represents SLC.

Ex. Z, https://phisonblog.com/the-benefits-of-using-slc-buffers-with-ssds-2/

88. Silicon Motion controllers move frequently accessed data to SLC NAND.

Hybrid Zone, a unique feature of the PCIe FerriSSD, offers a way to take advantage both of the low latency of SLC cells and the high memory density of TLC cells.

The Hybrid Zone feature partitions a single NAND die into separate SLC and MLC/TLC zones. Partitioning a single drive is particularly useful in low- to medium- density SSDs.

Without foregoing the density benefits of MLC/TLC, single NAND die SSDs can still maintain fast Write

SLC memory, which is ideal for emergency power shutdown operations. Without a portion of memory implemented as SLC, both the cost and the size of battery storage needed for MLC/TLC power shutdown would increase. The implementation of SLC memory is also ideal for high reliability and fast access— assigning SLC to boot code for instance – while also preserving a portion of the NAND medium for higher density MLC/TLC uses.

Ex. EE,

(https://www.siliconmotion.com/download/3Ta/a/PCIe\_FerriSSD\_Industrial\_Embedded\_Applic ations\_WP\_EN.pdf

89. The foregoing allegations are based on publicly available information and a reasonable investigation of the structure and operation of the Accused Products. Vervain reserves the right to modify this description, including, for example, on the basis of information about the Accused Products that it obtains during discovery.

90. Defendants' infringement has damaged and continues to damage Vervain in an amount yet to be determined, of at least a reasonable royalty.

91. This is an exceptional case. Vervain is entitled to attorneys' fees and costs under

35 U.S.C. § 285 as a result of the infringement of the '298 patent by Defendants.

## COUNT II: INFRINGEMENT OF U.S. PATENT NO. 9,196,385

92. Vervain incorporates by reference and re-alleges all of the foregoing paragraphs of this Complaint as if fully set forth herein.

93. Kingston has directly infringed and continue to infringe, either literally or under the doctrine of equivalents, at least claim 1 of the '385 patent by making, using, offer for sale,

### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 41 of 82

selling, and importing, without authority or license, the Accused Products in violation of 35

U.S.C. § 271(a). The Accused Products are non-limiting examples that were identified based on

currently available information, and Vervain reserves the right to identify additional infringing

activities, products, and services, including, for example, on the basis of information obtained

during discovery.

94. The Accused Products meet all the limitations of at least claim 1 of the '385

patent. Specifically, claim 1 of the '385 patent recites:

A system for storing data comprising:

at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks;

at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks; and

a flash translation layer (FTL); wherein the FTL is adapted to:

- a) maintain an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC nonvolatile memory module;

- b) determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module;

- c) determine which of the blocks of the plurality of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed; and

- d) allocate those blocks that receive the most frequent writes by transferring the respective contents of those blocks to the at least one SLC non-volatile memory module.

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 42 of 82

95. To the extent the preamble is a limitation, the Accused Products include a system for storing data. For example, as explained in Count I above, the Accused Products are flash memory products for storing data.

96. The Accused Products include at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks. As explained in Count I above, the Accused Products store certain data in MLC memory with individually erasable blocks, for example as part of an SLC caching or direct-to-TLC system.

97. The Accused Products include at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks. As explained in Count I above, the Accused Products store certain data in SLC memory with individually erasable blocks, for example as part of an SLC caching system.

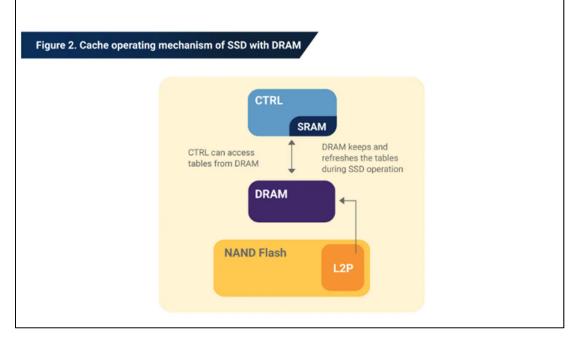

98. The Accused Products include a flash translation layer (FTL). For example, as explained in Count I above, the Accused Products provide mapping between logical and physical addresses using a data structure such as a L2P table. This is known as a flash translation layer:

# FLASH TRANSLATION LAYER

Phison develops its own FTL with proprietary improvements from generation to generation. Proprietary technologies include:

Ex. II, (https://www.phison.com/en/technologies/ftl)

99. The Accused Products include a flash translation layer (FTL), wherein the FTL is adapted to maintain an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 43 of 82

system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC nonvolatile memory module. For example, as explained in Count I above, the Accused Products provide mapping between logical and physical addresses using a data structure such as a L2P table, and these mappings have a minimum quanta such as a page.

100. The Accused Products include a flash translation layer (FTL), wherein the FTL is adapted to determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module. For example, as explained in Count I above, the controllers in the Accused Products perform a variety of data integrity functions, and remap data to SLC memory upon the failure of a data integrity test.

101. The Accused Products include a flash translation layer (FTL), wherein the FTL is adapted to determine which of the blocks of the plurality of the blocks in the MLC and SLC nonvolatile memory modules are accessed most frequently by maintaining a count of the number of times each one of the blocks is accessed. For example, as explained in Count I above, a variety of block counting mechanisms are present in the Accused Products.

102. The Accused Products include a flash translation layer (FTL), wherein the FTL is adapted to allocate those blocks that receive the most frequent writes by transferring the respective contents of those blocks to the at least one SLC non-volatile memory module. For

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 44 of 82

example, as explained in Count I above, frequently written blocks are allocated and their contents transferred to SLC.

103. The foregoing allegations are based on publicly available information and a reasonable investigation of the structure and operation of the Accused Products. Vervain reserves the right to modify this description, including, for example, on the basis of information about the Accused Products that it obtains during discovery.

104. Defendants' infringement has damaged and continues to damage Vervain in an amount yet to be determined, of at least a reasonable royalty.

105. This is an exceptional case. Vervain is entitled to attorneys' fees and costs under35 U.S.C. § 285 as a result of the infringement of the '385 patent by Defendants.

## COUNT III: INFRINGEMENT OF U.S. PATENT NO. 9,997,240

106. Vervain incorporates by reference and re-alleges all of the foregoing paragraphs of this Complaint as if fully set forth herein.

107. Kingston has directly infringed and continue to infringe, either literally or under the doctrine of equivalents, at least claim 1 of the '240 patent by making, using, offer for sale, selling, and importing, without authority or license, the Accused Products in violation of 35 U.S.C. § 271(a). The Accused Products are non-limiting examples that were identified based on currently available information, and Vervain reserves the right to identify additional infringing activities, products, and services, including, for example, on the basis of information obtained during discovery.

108. The Accused Products meet all the limitations of at least claim 6 of the '240 patent. Specifically, claim 6 of the '240 patent recites:

6. A system for storing data comprising:

at least one MLC non-volatile memory module comprising a plurality of individually erasable blocks;

at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks; and

a controller coupled to the at least one MLC non-volatile memory module and the at least one SLC non-volatile memory module, the controller maintaining an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module;

wherein the controller allocates those blocks that receive frequent writes into the SLC non-volatile memory module as hot blocks and those blocks that only receive infrequent writes into the MLC non-volatile memory module as cold blocks; and

wherein the controller is adapted to determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module;

wherein the controller is further adapted to maintain a count value of those blocks that are accessed most frequently and, on a periodic basis when the count value is a predetermined count value, transfer the contents of those counted blocks into the SLC non-volatile memory module, wherein the counted blocks transferred to after reaching the predetermined count value are determined in accordance with the next equivalent range of physical addresses determined by the controller.

109. To the extent the preamble is a limitation, the Accused Products include a system

for storing data. For example, as explained in Count I above, the Accused Products are flash

memory products for storing data.

110. The Accused Products include at least one MLC non-volatile memory module

comprising a plurality of individually erasable blocks. As explained in Count I above, the

Accused Products store certain data in MLC memory with individually erasable blocks, for

example as part of an SLC caching or direct-to-TLC system.

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 46 of 82

111. The Accused Products include at least one SLC non-volatile memory module comprising a plurality of individually erasable blocks. As explained in Count I above, the Accused Products store certain data in SLC memory with individually erasable blocks, for example as part of an SLC caching system.

112. The Accused Products include a controller coupled to the at least one MLC nonvolatile memory module and the at least one SLC non-volatile memory module, the controller maintaining an address map of at least one of the MLC and SLC non-volatile memory modules, the address map comprising a list of logical address ranges accessible by a computer system, the list of logical address ranges having a minimum quanta of addresses, wherein each entry in the list of logical address ranges maps to a similar range of physical addresses within either the at least one SLC non-volatile memory module or within the at least one MLC non-volatile memory module. For example, as explained in Count I above, the Accused Products provide mapping between logical and physical addresses using a data structure such as a L2P table, and these mappings have a minimum quanta such as a page.

113. In the Accused Products, the controller allocates those blocks that receive frequent writes into the SLC non-volatile memory module as hot blocks and those blocks that only receive infrequent writes into the MLC non-volatile memory module as cold blocks. For example, as explained in Count I above, frequently written blocks are allocated and their contents transferred to SLC, and infrequently written data is moved to MLC through copyback/garbage collection and other procedures.

114. In the Accused Products, the controller is adapted to determine if a range of addresses listed by an entry and mapped to a similar range of physical addresses within the at least one MLC non-volatile memory module, fails a data integrity test, and, in the event of such a

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 47 of 82

failure, the controller remaps the entry to the next available equivalent range of physical addresses within the at least one SLC non-volatile memory module. For example, as explained in Count I above, the controllers in the Accused Products perform a variety of data integrity functions, and remap data to SLC memory upon the failure of a data integrity test.

115. In the Accused Products, the controller is adapted to maintain a count value of those blocks that are accessed most frequently and, on a periodic basis when the count value is a predetermined count value, transfer the contents of those counted blocks into the SLC nonvolatile memory module, wherein the counted blocks transferred to after reaching the predetermined count value are determined in accordance with the next equivalent range of physical addresses determined by the controller. For example, as explained in Count I above, the Accused Products employ various types of block counting, and transfer the contents of frequently written blocks to the next available locations in SLC based on the count value.

116. The foregoing allegations are based on publicly available information and a reasonable investigation of the structure and operation of the Accused Products. Vervain reserves the right to modify this description, including, for example, on the basis of information about the Accused Products that it obtains during discovery.

117. Defendants' infringement has damaged and continues to damage Vervain in an amount yet to be determined, of at least a reasonable royalty.

118. This is an exceptional case. Vervain is entitled to attorneys' fees and costs under35 U.S.C. § 285 as a result of the infringement of the '240 patent by Defendants.

#### COUNT IV: INFRINGEMENT OF U.S. PATENT NO. 10,950,300

119. Vervain incorporates by reference and re-alleges all of the foregoing paragraphs of this Complaint as if fully set forth herein.

#### Case 1:24-cv-00254 Document 1 Filed 03/07/24 Page 48 of 82

120. Kingston has directly infringed and continue to infringe, either literally or under the doctrine of equivalents, at least claim 1 of the '300 patent by making, using, offer for sale, selling, and importing, without authority or license, the Accused Products in violation of 35 U.S.C. § 271(a). The Accused Products are non-limiting examples that were identified based on currently available information, and Vervain reserves the right to identify additional infringing activities, products, and services, including, for example, on the basis of information obtained during discovery.

121. The Accused Products meet all the limitations of at least claim 1 of the '300 patent. Specifically, claim 1 of the '300 patent recites:

A system for storing data comprising:

memory space containing volatile memory space and nonvolatile memory space, wherein the nonvolatile memory space includes both multilevel cell (MLC) memory space and single level cell (SLC) memory space;

at least one controller to operate memory elements and associated memory space;

at least one MLC nonvolatile memory element that can be mapped into the MLC memory space;

at least one SLC nonvolatile memory element that can be mapped into the SLC memory space;

at least one random access volatile memory;

an FTL flash translation layer, wherein the at least one controller, or FTL, or a combination of both maintain an address table in one or more of the memory elements and random access volatile memory;