### UNITED STATES DISTRICT COURT FOR THE EASTERN DISTRICT OF TEXAS MARSHALL DIVISION

| DAEDALUS PRIME LLC, | Civil Action No. <u>2:24ev235</u> |

|---------------------|-----------------------------------|

| Plaintiff,          | JURY TRIAL DEMANDED               |

| v.                  |                                   |

| MEDIATEK INC.       |                                   |

| Defendant.          |                                   |

# COMPLAINT FOR PATENT INFRINGEMENT AND DAMAGES <u>AND DEMAND FOR JURY TRIAL</u>

Plaintiff Daedalus Prime LLC ("Daedalus" or "Plaintiff") files this Complaint for Patent Infringement and Damages against MediaTek Inc. ("MediaTek" or "Defendant") and alleges as follows:

#### **INTRODUCTION**

1. The novel inventions disclosed in U.S. Patent Nos. 8,769,316 (the "'316 Patent"); 10,372,197 (the "'197 Patent"); 10,740,281 (the "'281 Patent"); 8,984,228 (the "'228 Patent"); 11,507,167 (the "'167 Patent"); 9,887,838 (the "'838 Patent"); 10,705,960 (the "'960 Patent") and 10,725,919 (the "'919 Patent") (collectively, the "Asserted Patents") in this matter were invented by Intel Corporation ("Intel"). Intel pioneered the field of microprocessor and semiconductor chip technology. This technology provides capabilities that are crucial to electronic devices such as personal computers and smartphones. Every year, Intel spends billions of dollars on research and development to invent, market, and sell new technology, and Intel obtains patents on many of the novel inventions that come out of that work, including the Asserted Patents.

#### THE PARTIES

- 2. Plaintiff is the current owner and assignee of the Asserted Patents.

- 3. Plaintiff is a Delaware limited liability company with its principal place of business located at 51 Pondfield Road, Suite 3, Bronxville, New York 10708.

- 4. On information and belief, Defendant MediaTek Inc. is a corporation organized and existing under the laws of Taiwan, and located at No. 1, Dusing Road 1, Hsinchu Science Park, Hsinchu City 30078, Taiwan.

- 5. On information and belief, Defendant directly and/or indirectly develops, designs, manufactures, distributes, markets, offers to sell and/or sells infringing products and services in the United States, including in the Eastern District of Texas, and otherwise direct infringing activities to this District in connection with their products and services as set forth in this Complaint.

#### **JURISDICTION**

- 6. This civil action arises under the Patent Laws of the United States, 35 U.S.C. § 1 *et seq.*, including without limitation 35 U.S.C. §§ 271, 281, 283, 284, and 285. Accordingly, this Court has subject matter jurisdiction under, *inter alia*, 28 U.S.C. §§ 1331 and 1338(a).

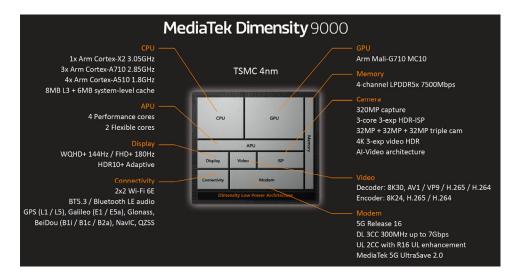

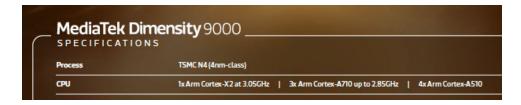

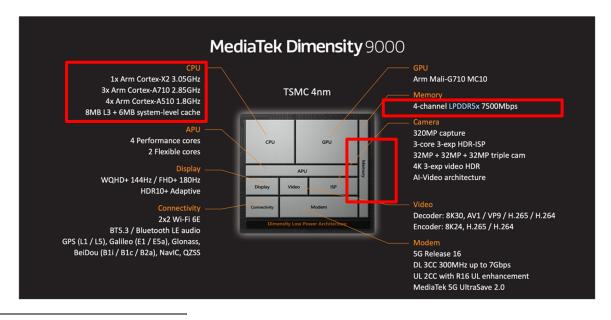

- 7. MediaTek sells semiconductors and/or processors that are used in mobile phones and other consumer products in the United States. For example, upon information and belief, MediaTek sells Dimensity 9300, Dimensity 9200 and Dimensity 9000 smartphone chips, as well as the MediaTek Kompanio 1380 Chromebook chips and the Dimensity Auto Cockpit CX-1 automotive chips in the U.S.¹:

<sup>&</sup>lt;sup>1</sup> https://www.mediatek.com/products/smartphones-2/mediatek-dimensity-9300; https://www.mediatek.com/products/smartphones-2/mediatek-dimensity-9200; https://www.mediatek.com/products/smartphones-2/mediatek-dimensity-9000;

# Powering 2 Billion+ Devices a year

# MediaTek Makes Great Technology Available To Everyone

Chances are you already have a MediaTek powered device in your life. MediaTek chips power more than **2 billion devices** every year.

# New MediaTek Powered Devices Each Year

2,013,258,324+

https://www.poweredbymediatek.com; https://i.mediatek.com/kompanio;

https://www.mediatek.com/products/automotive

- 8. This Court has personal jurisdiction over MediaTek Inc. at least because MediaTek Inc. sells, offers for sale, uses, makes and/or imports products that are and have been used, offered for sale, sold, and purchased in the Eastern District of Texas, and MediaTek Inc. has committed, and continues to commit, acts of infringement in the Eastern District of Texas, has conducted business in the Eastern District of Texas, and/or has engaged in continuous and systematic activities in the Eastern District of Texas.

- 9. Under 28 U.S.C. §§ 1391(b)-(d) and 1400(b), venue is proper in this judicial district as to MediaTek Inc. at least because MediaTek Inc. is a foreign corporation subject to personal jurisdiction in this judicial district and has committed acts of infringement within this judicial district giving rise to this action.

- 10. On information and belief, Defendant or Defendant's subsidiaries have physical facilities and employees in Texas, including an office at 2435 North Central Expressway, Suite

750, Richardson, Texas 75080. On information and belief, Defendant or Defendant's subsidiaries maintain multiple offices in Texas and have numerous employees in Texas<sup>2</sup>:

#### ISSCC 2022 / SESSION 2 / PROCESSORS / 2.5

# 2.5 A 5nm 3.4GHz Tri-Gear ARMv9 CPU Subsystem in a Fully Integrated 5G Flagship Mobile SoC

Ashish Nayak¹, HsinChen Chen¹, Hugh Mair¹, Rolf Lagerquist¹, Tao Chen¹, Anand Rajagopalan¹, Gordon Gammie¹, Ramu Madhavaram¹, Madhur Jagota¹, CJ Chung¹, Jenny Wiedemeier¹, Bala Meera¹, Chao-Yang Yeh², Maverick Lin², Curtis Lin², Vincent Lin², Jiun Lin², YS Chen², Barry Chen², Cheng-Yuh Wu², Ryan ChangChien², Ray Tzeng², Kelvin Yang², Achuta Thippana¹, Ericbill Wang², SA Hwang²

'MediaTek, Austin, TX; 2MediaTek, Hsinchu, Taiwan

11. Defendant has not contested proper venue and exercise of personal jurisdiction in this District for patent infringement actions. *See, e.g.*, Answer, ¶¶ 12-20, *Mosaid Techs. Inc. v. Mediatek Inc. et al.*, No. 2:23-cv-00129, ECF 24 (E.D. Tex. July 18, 2023); Answer, ¶¶ 11-13, *Am. Patents, LLC v. Mediatek Inc., et al.*, No. 4:22-cv-487, ECF 18 (E.D. Tex. Sept. 6, 2022).

#### THE ASSERTED PATENTS

12. The Intel inventions contained in the Asserted Patents in this case relate to groundbreaking improvements to microprocessor circuitry and mobile wireless, and have particular application in consumer electronics such as smartphones, tablets, and personal computers.

#### <u>U.S PATENT NO. 8,769,316</u>

13. On July 1, 2014, the United States Patent Office duly and legally issued the '316 Patent, entitled "Dynamically Allocating a Power Budget Over Multiple Domains of a Processor."<sup>3</sup>

<sup>&</sup>lt;sup>2</sup> Ashish Nayak et al., A 5nm 3.4GHz Tri-Gear ARMv9 CPU Subsystem in a Fully Integrated 5G Flagship Mobile SoC, ISSCC, 2022.

<sup>&</sup>lt;sup>3</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/8769316.

- 14. Daedalus is the owner and assignee of all right, title, and interest in and to the '316 Patent, including the right to assert all causes of action arising under the '316 Patent and the right to sue and obtain any remedies for past, present, or future infringement.

- 15. The '316 Patent describes, among other things, a method for determining a power budget for a multi-domain processor for a current time interval, determining a portion of the power budget to be allocated to first and second domains of the processor, and controlling a frequency of the domains based on the allocated portions. '316 Patent, Abstract. As the '316 Patent explains, one issue with multicore processors was that "the different circuitry can consume differing amounts of power based on their workloads" but "suitable mechanisms to ensure that these different units have sufficient power do not presently exist." *Id.* at 1:18-22.

- 16. The '316 Patent seeks to solve the problem with multicore processors. The novel inventions of the '316 Patent are recited in the claims. For example, claim 8 of the '316 Patent recites:

#### 8. A method comprising:

determining, in a power controller of a multi-domain processor, a power budget for the multi-domain processor for a current time interval, the multi-domain processor including at least a first domain and a second domain;

determining, in the power controller, a portion of the power budget to be allocated to the first and second domains, including allocating a minimum reservation value to the first domain and a minimum reservation value to the second domain, and sharing a remaining portion of the power budget according to a first sharing policy value for the first domain and a second sharing policy value for the second domain; and

controlling a frequency of the first domain and a frequency of the second domain based on the allocated portions.

#### '316 Patent, Cl. 8.

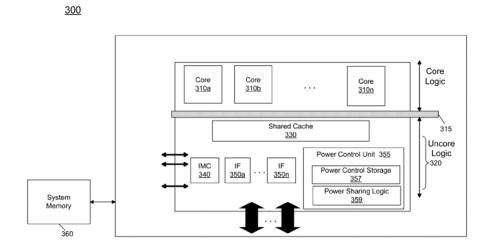

17. Figure 6 of the '316 Patent, reproduced below, shows a block diagram of a portion of a system of one embodiment of the claimed invention. "As shown in FIG. 6, processor 300 may

be a multicore processor including a plurality of cores [310-310,] ... [where] each [] core may be of an independent power domain ... configured to operate at an independent voltage and/or frequency". '316 Patent, 8:21-25. The cores may be "coupled via an interconnect 315" with a shared cache 330. *Id.* at 8:26-27. "[P]ower control unit 355 may include a power sharing logic 359 ... [that] perform[s] dynamic control and re-allocation of an available power budget between multiple independent domains of the processor." *Id.* at 8:33-36.

FIG. 6

'316 Patent, Fig. 6.

#### <u>U.S PATENT NO. 10,372,197</u>

- 18. On August 6, 2019, the United States Patent Office duly and legally issued the '197 Patent, entitled "User Level Control of Power Management Policies."

- 19. Daedalus is the owner and assignee of all right, title, and interest in and to the '197 Patent, including the right to assert all causes of action arising under the '197 Patent and the right to sue and obtain any remedies for past, present, or future infringement.

<sup>&</sup>lt;sup>4</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/10372197.

- 20. The '197 Patent describes, among other things, a multicore processor comprising a power controller that receives a workload configuration input and a plurality of energy performance bias values, determines a global energy performance bias value to update one or more power settings of one or more management features. '197 Patent, Fig. 4, 6:61-7:14; 7:55-8:4.

- 21. The novel features of the invention are recited in the claims. For example, claim 1 of the '197 Patent recites:

- 1. A processor comprising:

- a plurality of cores;

- a cache memory;

- an interconnect to couple the plurality of cores and the cache memory; and

- a power controller to control a plurality of power management features of the processor, wherein the power controller includes a tuning circuit to receive a workload configuration input regarding a workload, receive a plurality of energy performance bias (EPB) values and determine a global EPB value based thereon, and update at least one setting of at least one of the plurality of power management features based on the workload configuration input and the global EPB value.

*Id.* at Cl. 1.

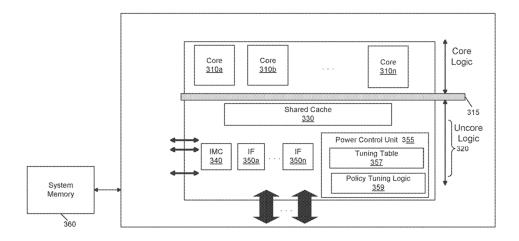

22. Figure 4 of the '197 Patent, reproduced below, is a block diagram of a processor in accordance with an embodiment of the inventions disclosed in the '197 Patent. As shown in Figure 4, processor 300 may be a multicore processor including a plurality of cores 310a-31. The various cores may be coupled via an interconnect 315 to a system agent or uncore 320 that includes various components. The uncore 320 may include a shared cache 330 which may be a last level cache. In addition, the uncore may include a power control unit 355.

FIG. 4

'197 Patent, Fig. 4.

#### **U.S PATENT NO. 10,740,281**

- 23. On August. 11, 2020, the United States Patent Office duly and legally issued the '281 Patent, entitled "Asymmetric Performance Multicore Architecture with Same Instruction Set Architecture."

- 24. Daedalus is the owner and assignee of all right, title, and interest in and to the '281 Patent, including the right to assert all causes of action arising under the '281 Patent and the right to sue and obtain any remedies for past, present, or future infringement.

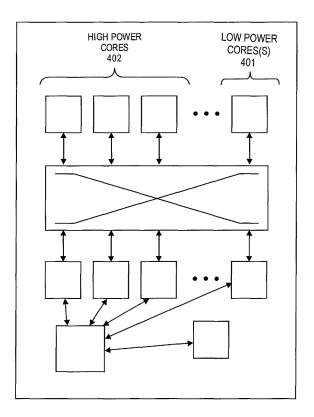

- 25. The '281 Patent describes, among other things, a method of operating enabled cores of a multi-core processor such that both cores support respective software routines with a same instruction set, with a first core being higher performance and consuming more power than a second core under a same set of applied supply voltage and operating frequency. '281 Patent, Abstract. The '281 Patent describes "a new approach in which at least one of the cores **401** is designed to be lower performance and therefore consume less power than other cores **402** in the

<sup>&</sup>lt;sup>5</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/10740281.

processor. However, the lower power core(s) **401** has a same logic design as the higher power core(s) **402** and therefore supports the same instruction set **403** as the high power core(s) **402**. The low power core(s) **401** achieve a lower power design point by having narrower drive transistor widths than the higher power core(s) and/or having other power consumption related design features". '281 Patent, 3:58-67.

26. The novel features of the invention are recited in the claims. For example, claim 8 of the '281 Patent recites:

#### 8. A method comprising:

monitoring a demand for a multi-core processor by an operating system executing on the multi-core processor, wherein the multi-core processor comprises a first plurality of cores and a second plurality of cores that support a same instruction set, the first plurality of cores are higher performance and consume more power than the second plurality of cores, each of the second plurality of cores have a maximum operating frequency that is less than a maximum operating frequency of each of the first plurality of cores, and a caching layer shared by the first plurality of cores and the second plurality of cores; and

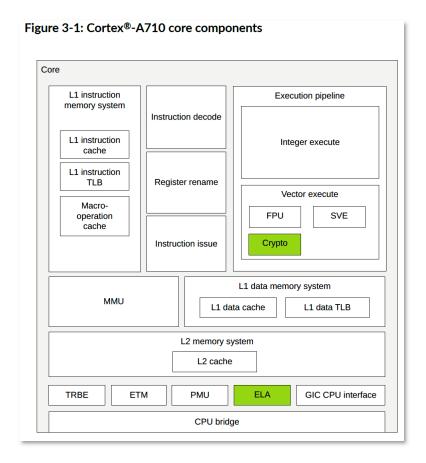

controlling a core mix of the first plurality of cores and the second plurality of cores based on the demand with power management hardware of the multi-core processor.

'281 Patent, Cl. 8.

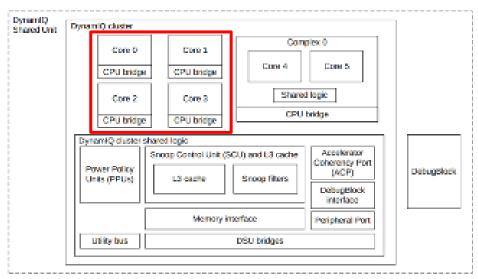

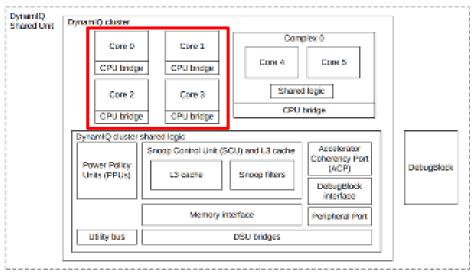

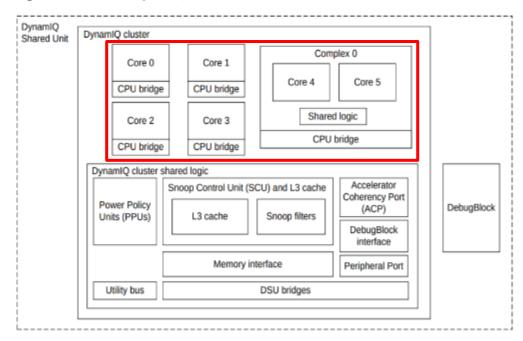

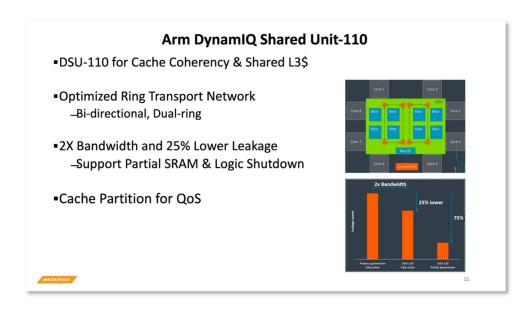

27. Figure 4 of the '281 Patent, reproduced below, shows a block diagram of a portion of a system of one embodiment of the claimed invention. As shown in Figure 4, cores 401 are "lower performance and therefore consume less power than [the higher power] cores **402** in the processor." The "lower power core[s] **401** has a same logic design as the higher power core[s] **402** and therefore support[] the same instruction set **403** as the high power core[s] **402**. *Id.* at 3:58-65.

FIG. 4

'281 Patent, Fig. 4.

#### **U.S PATENT NO. 8,984,228**

- 28. On March 17, 2015, the United States Patent Office duly and legally issued the '282 Patent, entitled "Providing Common Caching Agent for Core and Integrated Input/Output (IO) Module."

- 29. Daedalus is the owner and assignee of all right, title, and interest in and to the '228 Patent, including the right to assert all causes of action arising under the '228 Patent and the right to sue and obtain any remedies for past, present, or future infringement.

- 30. The '228 Patent describes, among other things, a multicore processor having a plurality of cores, a shared cache memory, an integrated input/output module to interface between

<sup>&</sup>lt;sup>6</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/8984228.

the multicore processor and at least one IO device coupled to the multicore processor, and a caching agent to perform cache coherency operations for the plurality of cores and the integrated input/output module. '228 Patent, Abstract. As the '228 Patent explains, "problems arise once an IO component is integrated on the same chip with a multiprocessor. Traditional IO integration treats the IO component as a separate caching agent, meaning that dedicated logic is associated with the IO component to handle cache coherency operations. When an IO agent is performing read/write operations to main memory, it has to snoop the CPU side cache to maintain cache coherency." *Id.* at 1:19-25. The integrated input/output module, however, "reduces the amount of snoop traffic needed since a reduced number of caching agents per system can be realized." *Id.* at 3:8-9.

31. The novel features of the invention are recited in the claims. For example, claim 1 of the '228 Patent recites:

#### 1. An apparatus comprising:

a multicore processor including a plurality of cores, a shared cache memory, an integrated input/output (IIO) module to interface between the multicore processor and at least one IO device coupled to the multicore processor, and a caching agent to perform cache coherency operations for the plurality of cores and the IIO module, the caching agent a single caching agent for the multicore processor and including a plurality of distributed portions each associated with a corresponding one of the plurality of cores.

#### '228 Patent, Cl. 1.

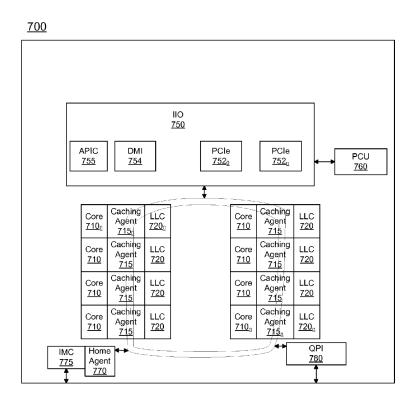

32. Figure 6 of the '228 Patent, reproduced below, shows a block diagram of a portion of a system of one embodiment of the claimed invention. As shown in Figure 6, "processor 700 includes a distributed configuration having partitions or slices each including a core 710 and a partition of a caching agent 715 and a LLC 720. Note that while distributed caching agents are shown, understand that these distributed portions form a single caching agent, and which is

configured to handle cache coherency operations both for the cores as well as an IIO module **750**." *Id.* at 6:23-29.

FIG. 6

'228 Patent, Fig. 6.

#### U.S PATENT NO. 11,507,167

- 33. On November 22, 2022, the United States Patent Office duly and legally issued the '167 Patent, entitled "Controlling Operating Voltage of a Processor."<sup>7</sup>

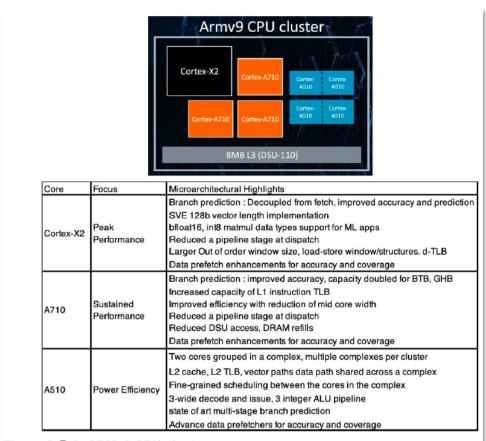

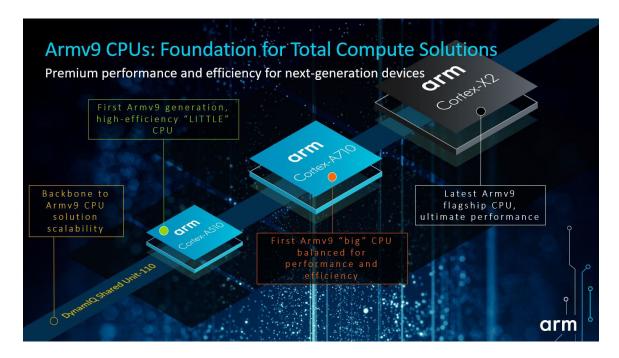

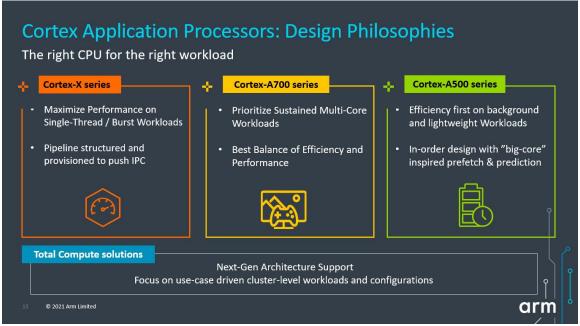

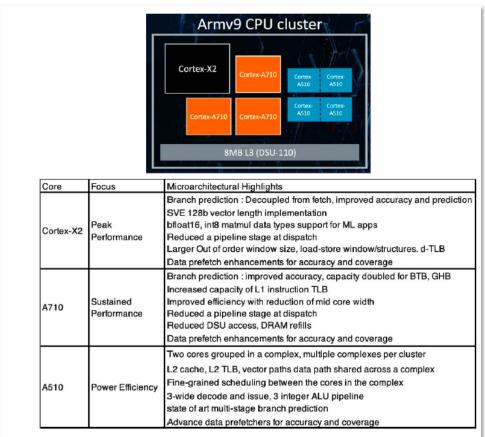

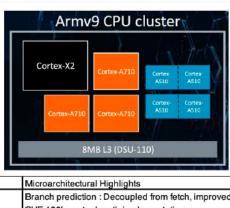

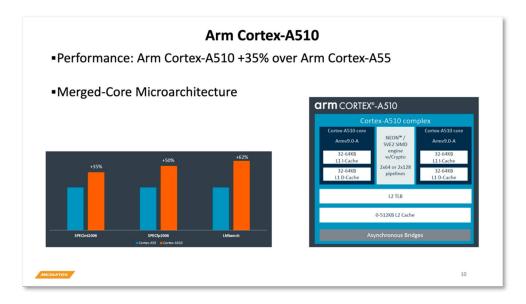

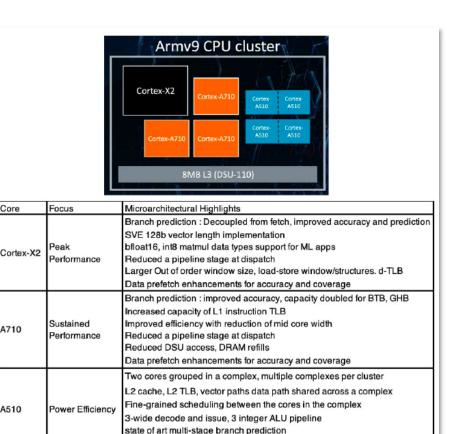

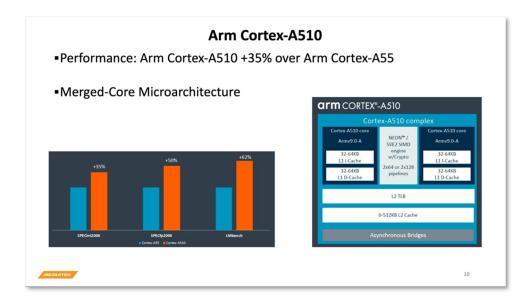

- 34. Daedalus is the owner and assignee of all right, title, and interest in and to the '167 Patent, including the right to assert all causes of action arising under the '167 Patent and the right to sue and obtain any remedies for past, present, or future infringement.

- 35. The '167 Patent describes, among other things, a processor that includes a core domain with a plurality of cores, and a power controller capable of instructing a voltage regulator

<sup>&</sup>lt;sup>7</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/11507167.

to increase the operating voltage. '167 Patent, Abstract. As the '167 Patent explains, "there is a vital need for energy efficiency and conservation associated with integrated circuits." *Id.* at 1:44-45. The '167 Patent explains that "voltage transitions within a processor may be segmented into two or more segments. In an embodiment, a dispatcher or other control logic of the processor may controllably cause such multi-phase voltage ramps. In operation, a first segment is a transition to an interim or safe voltage level, which is at a sufficient voltage level to cover all active agents (and at least one additional agent) running at a lower frequency in a particular transition. Any additional voltage increase to enable a pending frequency increase requested for one or more of the agents is handled in a second segment of the transition, which can occur after a low power state exit of the additional agent. [...] In this way, a reduced latency for allowing an agent to exit a low power state may be realized." *Id.* at 2:28-46.

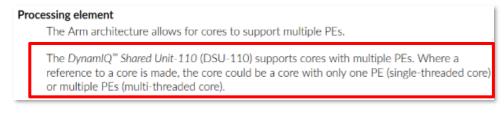

36. The novel features of the invention are recited in the claims. For example, claim 1 of the '167 Patent recites:

#### 1. A multicore processor comprising:

a plurality of cores, wherein each core comprises a processor configured to operate at an independent voltage and frequency level;

wherein at least one core is coupled to a plurality of levels of cache memory;

a power control unit configured to cause an operating voltage to be updated for one or more of the cores in response to receiving a request to alter an operating state of the one or more of the cores;

wherein the power control unit is further configured to:

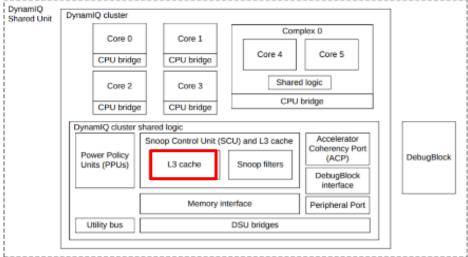

receive a first request to alter an operating state of a first core to a modified operating state, the modified operating state operating at a third voltage level;

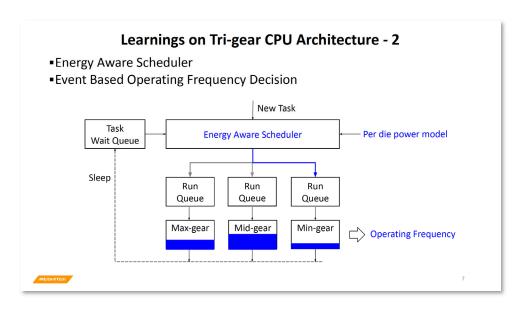

responsive to the first request, cause a voltage regulator to increase an operating voltage of the first core from a first voltage level to a second voltage level lower than the third voltage level;

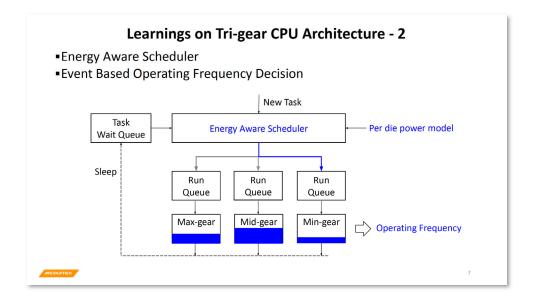

enable a second core to exit an inactive state and enter an active state while the operating voltage of the first core is at the second voltage level; increase the operating voltage of the first core from the second voltage level to the third voltage level after the second core enters the active state.

'167 Patent, Cl. 1.

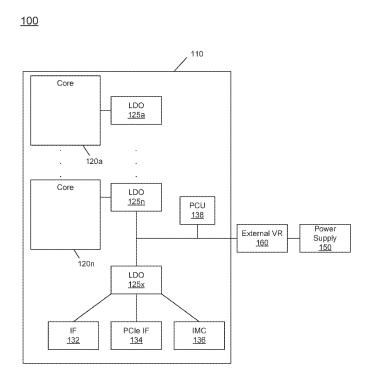

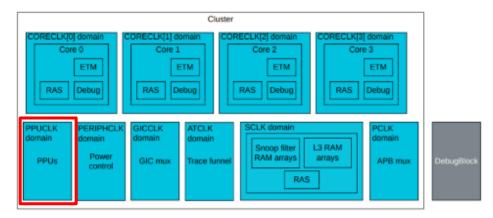

37. Figure 1 of the '167 Patent, reproduced below, shows a block diagram of a portion of a system of one embodiment of the claimed invention. "As shown in FIG. 1, system 100 may include various components, including a processor 110 which as shown is a multicore processor. Processor 110 may be coupled to a power supply 150 via an external voltage regulator 160, which may perform a first voltage conversion to provide a primary regulated voltage to processor 110." *Id.* at 2:49-54.

FIG. 1

#### U.S PATENT NO. 9,887,838

- 38. On February 6, 2018, the United States Patent Office duly and legally issued the '838 Patent, entitled "Method and Device for Secure Communications Over a Network Using a Hardware Security Engine."

- 39. Daedalus is the owner and assignee of all right, title, and interest in and to the '838 Patent, including the right to assert all causes of action arising under the '838 Patent and the right to sue and obtain any remedies for past, present, or future infringement.

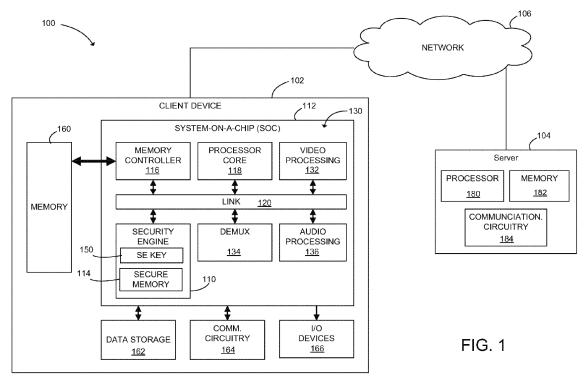

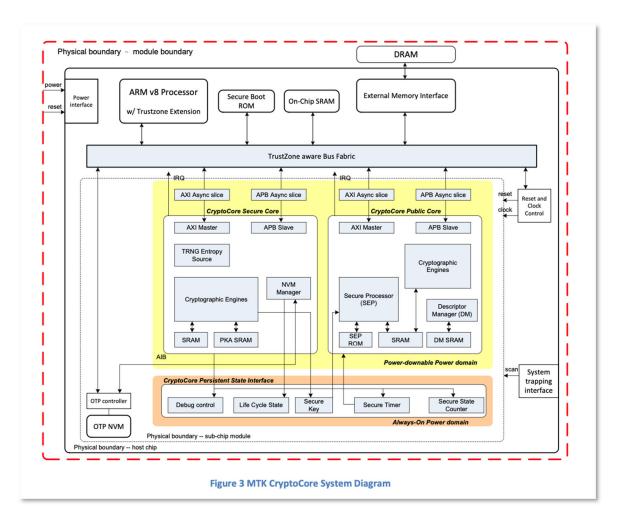

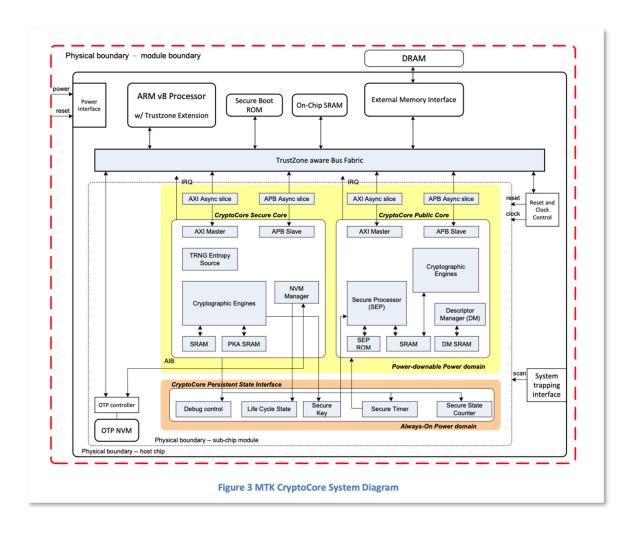

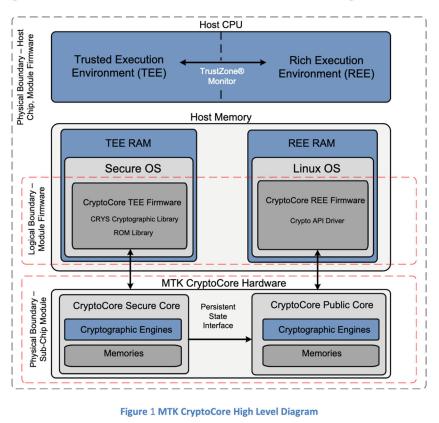

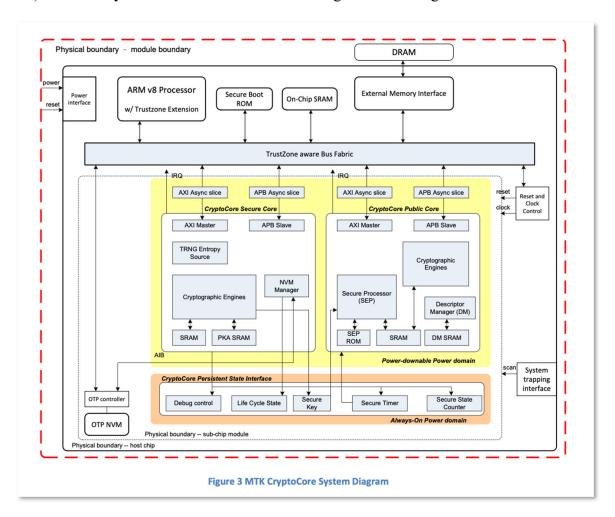

- 40. The '838 Patent describes, among other things, establishing a secure communication session with a server including initiating a request for a secure communication session with a server using a nonce value generated in a security engine of a system-on-a-chip (SOC) of a client device. '838 Patent, Abstract. As the '838 Patent explains, "there is a vital need for energy efficiency and conservation associated with integrated circuits." *Id.* at 1:44-45. The '838 Patent explains that a "security engine 110 may be embodied as a security co-processor or processing circuitry separate from the processor core 118. The security engine 110 includes the security key 150 and the secure memory 114, which is accessible only by the security engine 110. The security engine 110 stores the security key 150, and other cryptographic keys as discussed below, in the secure memory 114." *Id.* at 4:17-23.

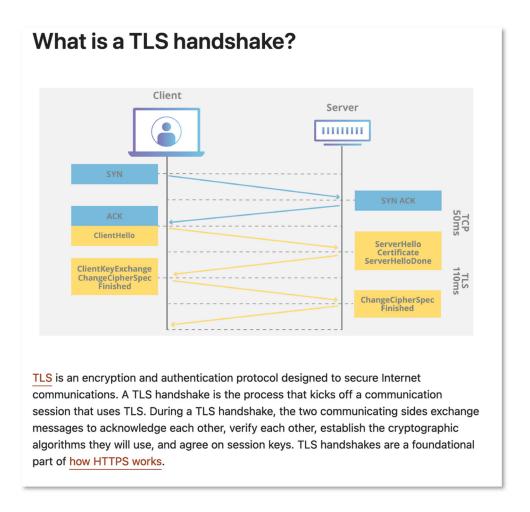

- 41. The novel features of the invention are recited in the claims. For example, claim 9 of the '838 Patent recites:

### 9. A method comprising:

generating a random nonce in a security engine that is separate from a processor core of a system-on-a-chip of a client device;

initiating, using the client device, a request for a secure communication session with a remote server over a network, the request including the random nonce;

$<sup>^{8}\</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/9887838.$

performing a cryptographic key exchange, using the security engine of the system-on-a-chip, with the remote server;

generate a symmetric session key to encrypt messages sent to the remote server and decrypt messages received from the remote server during the secure communication session;

encrypting the session key based on a security key that was encoded in a secure memory of the security engine during a manufacturing process of the system-on-a-chip;

storing the encrypted session key in the secure memory of the security engine of the system-on-a-chip; and

establishing, using the client device, the secure communication session with the remote server using the session key.

'838 Patent, Cl. 9.

42. Figure 1 of the '838 Patent, reproduced below, shows a block diagram of a portion of a system of one embodiment of the claimed invention. "In the illustrative embodiment of FIG. 1, the SOC 112 includes the security engine 110, a memory controller 116, a processor core 118, and a plurality of hardware peripherals 130, which are communicatively coupled to each other via a link 120." *Id.* at 1:63-67. As shown in Figure 1, "a system 100 [establishes] a secure communication session include[ing] a client device 102, a server 104, and a network 106. In operation, the client device 102 initiates a request for a secure communication session with the server 104 over the network 106. *Id.* at 3:24-28.

'838 Patent, Fig. 1.

## **U.S PATENT NOS. 10,705,960 and 10,725,919**

- 43. On July 7, 2020, the United States Patent Office duly and legally issued the '960 Patent, entitled "Processors Having Virtually Clustered Cores and Cache Slices." 9

- 44. On July 28, 2020, the United States Patent Office duly and legally issued the '919 Patent, entitled "Processors Having Virtually Clustered Cores and Cache Slices." <sup>10</sup>

- 45. Daedalus is the owner and assignee of all right, title, and interest in and to the '960 Patent and the '919 Patent, including the right to assert all causes of action arising under the '960 Patent and '919 Patent, and the right to sue and obtain any remedies for past, present, or future infringement.

- 46. The '960 Patent and the '919 Patent describe, among other things, a system comprising a plurality of processors each having one or more corresponding lower-level caches,

<sup>&</sup>lt;sup>9</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/10705960.

<sup>&</sup>lt;sup>10</sup> https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/10725919.

and a shared higher-level cache, which includes a plurality of distributed cache slices. '960 Patent, Abstract. The claimed processors include logic to direct an access that misses in one or more lower-level caches of a corresponding logical processor to a subset of the distributed cache slides in a virtual cluster that corresponds to the logical processor. *Id.* As the '960 Patent explains, "many processors now have multiple to many cores that are monolithically integrated on a single integrated circuit or die[,]" which "generally help to allow multiple threads or other workloads to be performed concurrently, which generally helps to increase execution throughput." *Id.* at 1:26-31. "However, the multiple cores may have a downside in terms of longer hit and/or miss latencies to a shared cache. [...] In addition, the multiple or many cores also tend to increase the memory address entropy at memory controllers, which may tend to result in lower effective memory bandwidth." *Id.* at 1:32-47. The inventions described and claimed in the '960 Patent overcome these challenges by providing novel processors with virtually clustered cores and cache slices, which has the effect of resulting in higher effective memory bandwidth.

47. The novel features of the invention are recited in the claims. For example, claim 15 of the '960 Patent recites:

#### 15. A method comprising:

executing instructions and processing data with a plurality of cores, the plurality of cores comprising symmetric multi-threaded cores;

storing the instructions and the data in a cache subsystem, the cache subsystem comprising a plurality of first level caches and at least one higher level distributed cache comprising a plurality of distributed cache portions that are physically distributed across a die, each first level cache integral to one of the plurality of cores and each distributed cache portion accessible to each of the plurality of cores;

sharing the plurality of distributed cache portions among the plurality of cores;

providing coherent, non-uniform access to the plurality of distributed cache portions by the plurality of cores;

enabling a first frequency to be set for a first cluster of the plurality of cores which are physically proximate to one another and a second frequency to be set for a second cluster of the plurality of cores which are physically proximate to one another, wherein an average distance between cores in the first cluster is less than an average distance between the plurality of cores;

selectively gating power to the first cluster of the plurality of cores and distributed cache portions that correspond to the first cluster and/or the second cluster of the plurality of cores and distributed cache portions that correspond to the second cluster;

controlling access by the symmetric multi-threaded cores to a first system memory with a first integrated memory controller; and

controlling access by the symmetric multi-threaded cores to a second system memory with a second integrated memory controller.

'960 Patent, Cl. 15.

48. Further, claim 16 of the '919 Patent recites:

#### 16. A method comprising:

executing instructions and processing data with a plurality of cores, the plurality of cores comprising symmetric multi-threaded cores;

storing the instructions and the data in a cache subsystem, the cache subsystem comprising a plurality of first-level caches and at least one higher-level distributed cache comprising a plurality of distributed cache portions that are physically distributed across a die, each first-level cache integral to one of the plurality of cores and each distributed cache portion accessible to each of the plurality of cores;

sharing the plurality of distributed cache portions among the plurality of cores;

providing coherent, non-uniform access to the plurality of distributed cache portions by the plurality of cores;

enabling a first frequency to be set for a first cluster of the plurality of cores which are physically proximate to one another and a second frequency to be set for a second cluster of the plurality of cores which are physically proximate to one another, wherein an average distance between cores in the first cluster is less than an average distance between all of the cores; and

selectively gating power to the first cluster of the plurality of cores and distributed cache portions of the at least one higher-level distributed cache that correspond to the first cluster and/or the second cluster of the plurality of cores and distributed cache portions of the at least one higher-level distributed cache that correspond to the second cluster.

'919 Patent, Cl. 16.

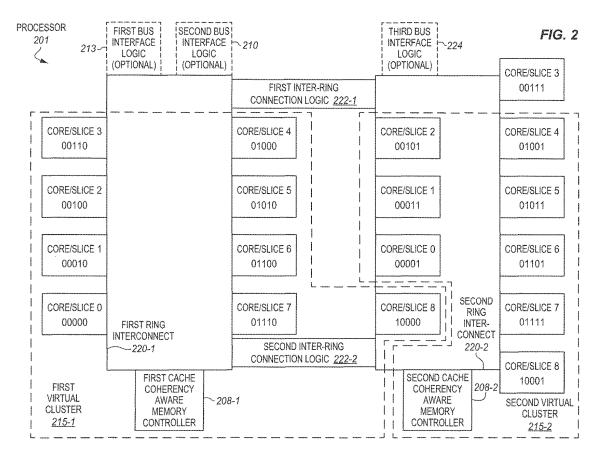

49. Figure 2 of the '960 Patent, reproduced below, shows a block diagram of an embodiment of a processor 201 having a first virtual cluster 215-1 and a second virtual cluster 215-2. The processor includes eighteen cores and eighteen corresponding cache slices. The cores/slices are coupled with first and second ring interconnects, which are coupled by a first interring connection logic and a second inter-ring connection logic.

'960 Patent, Fig. 2.

#### MEDIATEK'S USE OF THE PATENTED TECHNOLOGY

50. According to its website, MediaTek is the world's 5th largest global fabless semiconductor company.<sup>11</sup> MediaTek powers more than 2 billion devices a year, which are in 20

<sup>11</sup> https://www.mediatek.com/who-we-are.

percent of homes and nearly 1 of every 3 mobile phones globally.<sup>12</sup> Upon information and belief, MediaTek's revenue in 2023 is approximately \$13 billion USD<sup>13</sup>.

On information and belief, MediaTek makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States various semiconductor chips which infringe the Asserted Patents. For example, MediaTek makes, uses, sells, and/or offers to sell in the United States, and/or imports into the United States the MediaTek Dimensity SoCs. As described in the counts below, these and other MediaTek products that include processors based on the ARMv8.2 architecture, as well as subsequent revisions to the ARM architecture such as the ARMv9 architecture, include power management, multiprocessor, cache and security technology that infringe the Asserted Patents.

#### FIRST COUNT

## (Infringement of U.S Patent No. 8,769,316)

- 52. Daedalus incorporates by reference the allegations set forth in Paragraphs 1-51 of the Complaint as though fully set forth herein.

- 53. The claims of the '316 Patent are valid and enforceable.

- 54. On information and belief, in violation of 35 U.S.C. § 271(a), MediaTek has directly infringed and continues to directly infringe one or more claims of the '316 Patent, including at least Claim 8 of the '316 Patent, in the state of Texas, in this judicial district, and elsewhere in the United States by, among other things, making, using, selling, offering for sale, and/or importing into the United States products that embody one or more of the inventions claimed in the '316 Patent, including but not limited to its electronic devices containing SoCs or microprocessors based on or derived from ARMv8.2 architecture, as well as subsequent revisions

<sup>&</sup>lt;sup>12</sup> *Id.*; https://www.poweredbymediatek.com/.

<sup>&</sup>lt;sup>13</sup> https://corp.mediatek.com/investor-relations/investor-relation-news/2023-q4-financial-results.

to the ARM architecture such as the ARMv9 architecture, such as the Dimensity 9300 SoCs, and all reasonably similar products (the "'316 Patent Accused Products").

- 55. Each of the '316 Patent Accused Products implements a method comprising determining, in a power controller of a multi-domain processor, a power budget for the multi-domain processor for a current time interval, the multi-domain processor including at least a first domain and a second domain.

- 56. For example, SoCs or microprocessors derived from the ARMv8.2 architecture, as well as subsequent revisions to the ARM architecture such as the ARMv9 architecture, such as the Dimensity 9300, include logic such as ARM Power Policy Units that are configured by systems such as an ARM System Control Processor.<sup>14</sup>

- 57. Upon information and belief, Dimensity 9300 includes a Power Controller that determines a power budget for the multi-domain processor for a current time interval. The multi-domain processor includes a first domain comprising of the CPU and a second domain comprising of the GPU. The GPU.

- 58. Each of the '316 Patent Accused Products implements a method comprising determining, in the power controller, a portion of the power budget to be allocated to the first and second domains, including allocating a minimum reservation value to the first domain and a minimum reservation value to the second domain, and sharing a remaining portion of the power budget according to a first sharing policy value for the first domain and a second sharing policy value for the second domain.

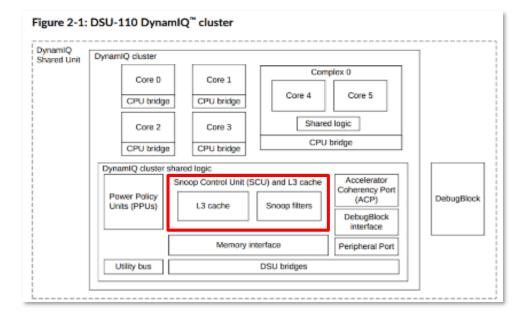

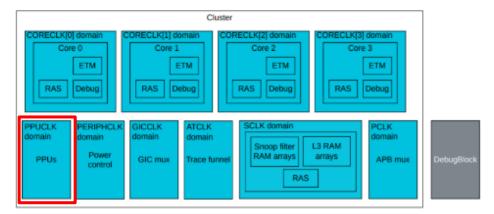

<sup>&</sup>lt;sup>14</sup> "Arm DynamIQ Shared Unit-110", page 78, *available at* https://documentationservice.arm.com/static/62bb28beb334256d9ea8cc32; *id.*, page 51; *id.*, page 80; *id.*, page 77.

<sup>&</sup>lt;sup>15</sup> ARM, *High-level Considerations for Power Management of a big.LITTLE™ System*, Application Note 424 (2016), p. 15, https://developer.arm.com/documentation/dai0424/a/I1007542.

<sup>&</sup>lt;sup>16</sup> Xin Wang, *Intelligent Power Allocation, Maximize Performance in the Thermal Envelope*, ARM White Paper (March 2017), at pp. 11-14,

https://developer.arm.com/Tools%20 and%20 Software/Intelligent%20 Power%20 Allocation.

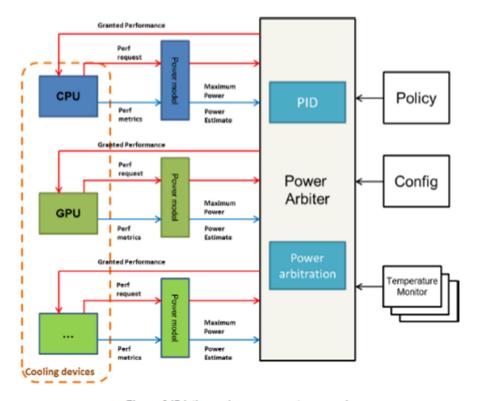

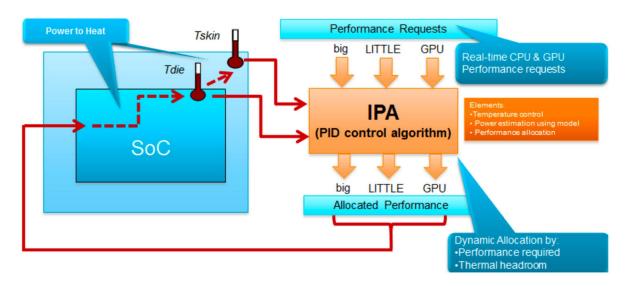

59. For example, the Dimensity 9300 uses intellectual power allocation (IPA) to dynamically allocate power budget between two domains pursuant to a power allocation policy.<sup>17</sup> Under the policy, "[e]ach cooling device is allocated with a share of the power budget, depending on the proportion of the device's requested power in the total requested power;" and the extra power is allocated between the devices based on the weight for each device.<sup>18</sup>

Figure 8 IPA thermal management approach

To keep the system within the thermal envelope, IPA uses the PID controller to dynamically allocate power budget, and allows a short term boosting by exploiting thermal headroom.

IPA manages performance requests from different cooling devices. Each cooling device can request different performance levels, and has a power model to estimate its power consumption and the impact of the performance request for the cooling device.

The Power Arbiter provides guaranteed minimum performance. You can configure the Power Arbiter with policies to allocate power among different cooling devices.

<sup>&</sup>lt;sup>17</sup> *Id., supra* note 8, pp. 12, 14-15.

<sup>&</sup>lt;sup>18</sup> *Id.* at pp. 14-15.

- 60. Further, on information and belief, MediaTek has actively induced and/or contributed to infringement of at least Claim 8 of the '316 Patent in violation of at least 35 U.S.C. § 271(b), (c), and (f).

- 61. Users of the '316 Patent Accused Products directly infringe at least Claim 8 of the '316 Patent when they use the '316 Patent Accused Products in the ordinary, customary, and intended way. On information and belief, MediaTek's inducements in violation of 35 U.S.C. § 271(b) include, without limitation and with specific intent to encourage infringement, knowingly inducing consumers to use the '316 Patent Accused Products within the United States in the ordinary, customary, and intended way by, directly or through intermediaries, supplying the '316 Patent Accused Products to consumers within the United States and instructing and encouraging such customers to use the '316 Patent Accused Products in the ordinary, customary, and intended way, which MediaTek knew infringes at least Claim 8 of the '316 Patent, or, alternatively, was willfully blind to the infringement.

- 62. On information and belief, MediaTek's inducements in violation of 35 U.S.C. § 271(b) further include, without limitation and with specific intent to encourage the infringement, knowingly inducing customers to commit acts of infringement with respect to the '316 Patent Accused Products within the United States, by, directly or through intermediaries, instructing and encouraging such customers to import, make, use, sell, offer to sell, or otherwise commit acts of infringement with respect to the '316 Patent Accused Products in the United States, which MediaTek knew infringes at least Claim 8 of the '316 Patent, or, alternatively, was willfully blind to the infringement.

- 63. On information and belief, in violation of 35 U.S.C. § 271(c), MediaTek's contributory infringement further includes offering to sell or selling within the United States, or

importing into the United States, components of the patented invention of at least Claim 8 of the '316 Patent, constituting a material part of the invention. On information and belief, MediaTek knows and has known the same to be especially made or especially adapted for use in an infringement of the '316 Patent, and such components are not a staple article or commodity of commerce suitable for substantial noninfringing use.

- 64. On information and belief, in violation of 35 U.S.C. § 271(f)(1), MediaTek's infringement further includes without authority supplying or causing to be supplied in or from the United States all or a substantial portion of the components of the patented invention of at least Claim 8 of the '316 Patent, where such components are uncombined in whole or in part, in such manner as to actively induce the combination of such components outside of the United States in a manner that would infringe the patent if such combination occurred within the United States.

- 65. On information and belief, in violation of 35 U.S.C. § 271(f)(2), MediaTek's infringement further includes without authority supplying or causing to be supplied in or from the United States components of the patented invention of at least Claim 8 of the '316 Patent that are especially made or especially adapted for use in the invention and not staple articles or commodities of commerce suitable for substantial noninfringing use, where such components are uncombined in whole or in part, knowing that such components are so made or adapted and intending that such components will be combined outside of the United States in a manner that would infringe the patent if such combination occurred within the United States.

- 66. MediaTek is not licensed or otherwise authorized to practice the claims of the '316 Patent.

- 67. Thus, by its acts, MediaTek has injured Daedalus and is liable to Daedalus for directly and/or indirectly infringing one or more claims of the '316 Patent, whether literally or under the doctrine of equivalents, including without limitation Claim 8.

- 68. On information and belief, MediaTek has known about the '316 Patent at least since August 23, 2022.<sup>19</sup> At a minimum, MediaTek has knowledge of the '316 Patent at least as of the filing of this Complaint. Accordingly, MediaTek's infringement of the '316 Patent has been and continues to be deliberate, intentional, and willful, and this is therefore an exceptional case warranting an award of enhanced damages and attorneys' fees and costs pursuant to 35 U.S.C. §§ 284 and 285.

- 69. As a result of MediaTek's infringement of the '316 Patent, Daedalus has suffered monetary damages, and seeks recovery, in an amount to be proven at trial, adequate to compensate for MediaTek's infringement, but in no event less than a reasonable royalty with interest and costs.

- 70. On information and belief, MediaTek will continue to infringe the '316 Patent unless enjoined by this Court. MediaTek's infringement of Daedalus' rights under the '316 Patent will continue to damage Daedalus, causing irreparable harm for which there is no adequate remedy at law, unless enjoined by this Court.

#### **SECOND COUNT**

#### (Infringement of U.S Patent No. 10,372,197)

- 71. Daedalus incorporates by reference the allegations set forth in Paragraphs 1-70 of the Complaint as though fully set forth herein.

- 72. The claims of the '197 Patent are valid and enforceable.

<sup>&</sup>lt;sup>19</sup> Daedalus Prime LLC v. Mazda Motor Corp., et al., No. 22-cv-01108 (D. Del. Aug. 23, 2022).

- 73. On information and belief, in violation of 35 U.S.C. § 271(a), MediaTek has directly infringed and continues to directly infringe one or more claims of the '197 Patent, including at least Claim 1 of the '197 Patent, in the state of Texas, in this judicial district, and elsewhere in the United States by, among other things, making, using, selling, offering for sale, and/or importing into the United States products that embody one or more of the inventions claimed in the '197 Patent, including but not limited to its electronic devices containing SoCs or microprocessors based on or derived from ARMv8.2 architecture, as well as subsequent revisions to the ARM architecture such as the ARMv9 architecture, such as the Dimensity 9300 SoCs, and all reasonably similar products (the "'197 Patent Accused Products").

- 74. Each of the '197 Patent Accused Products comprises a processor. For example, the Dimensity 9300 contains one or more microprocessors based on or derived from the ARM Cortex-X4 architecture and the ARM Cortex-A720 architecture.

- 75. Each of the '197 Patent Accused Products comprises a plurality of cores.

- 76. Specifically, the '197 Patent Accused Products include one or more clusters comprising a plurality of cores. For example, Dimensity 9300 SoCs comprise four Cortex-X4 and 4 Cortex A720 cores<sup>20</sup>:

<sup>&</sup>lt;sup>20</sup> https://mediatek-marketing.files.svdcdn.com/production/documents/Infographics/MediaTek-Dimensity-9300-Infographic.pdf?dm=1698856450.

- 77. Each of the '197 Patent Accused Products comprises a cache memory.

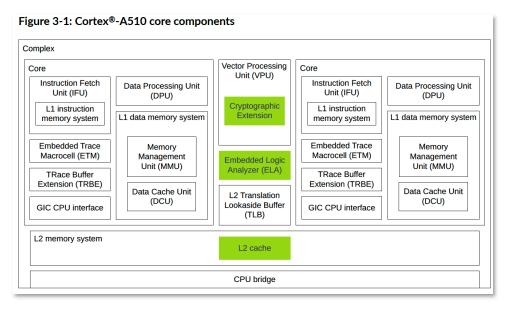

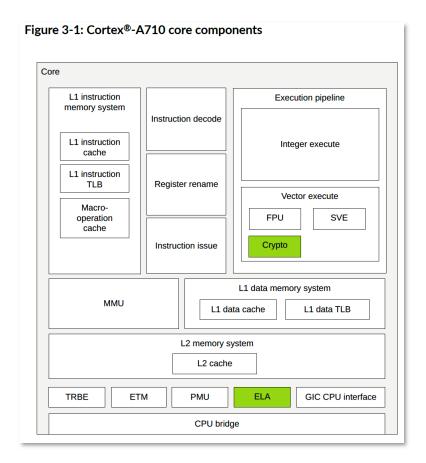

- 78. For example, Dimensity 9300 SoCs comprise L1 and L2 cache memories<sup>21</sup>.

<sup>&</sup>lt;sup>21</sup> Arm® Cortex-X4 Core Technical Reference Manual, p. 41; Arm® Cortex-A720 Core Technical Reference Manual, p. 37.

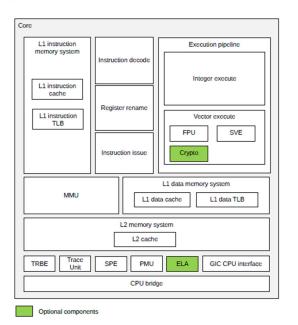

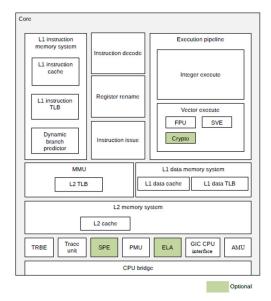

Figure 3-1: Cortex-X4 core components

Figure 3-1: Cortex-A720 core components

- 79. Each of the '197 Patent Accused Products comprises an interconnect to couple the plurality of cores and the cache memory.

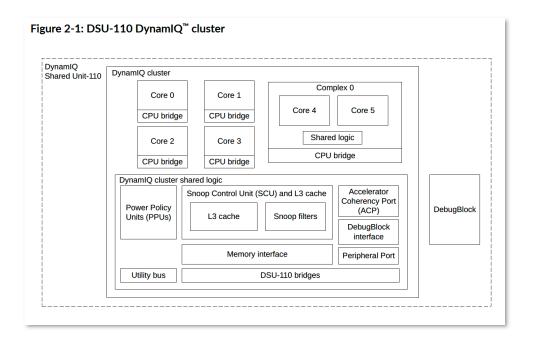

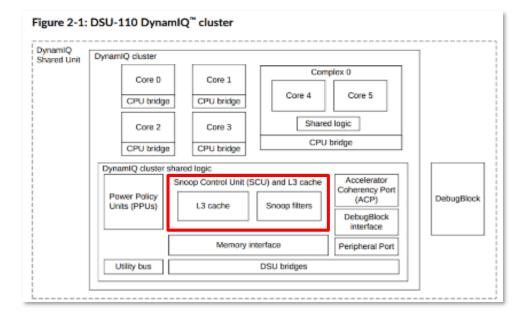

- 80. For example, the Dimensity 9300 SoCs include a DynamIQ Shared Unit (DSU). The DSU couples the plurality of cores to the L3 cache memory<sup>22</sup>.

<sup>&</sup>lt;sup>22</sup> Stefan Rosinger & Saurabh Pradhan, *Dimensity 9000 – A Flagship Smartphone SoC*, at p. 8, https://hc34.hotchips.org/assets/program/conference/day2/Mobile%20and%20Edge/HC2022.Mediatek.EricbillWang .v08.pptx.pdf.

- 81. Each of the '197 Patent Accused Products comprises a power controller to control a plurality of power management features of the processor, wherein the power controller includes a tuning circuit to receive a workload configuration input regarding a workload, receive a plurality of energy performance bias (EPB) values and determine a global EPB value based thereon, and update at least one setting of at least one of the plurality of power management features based on the workload configuration input and the global EPB value.

- 82. For example, SoCs or microprocessors derived from the ARMv8.2 architecture, as well as subsequent revisions to the ARM architecture such as the ARMv9 architecture, such as the Dimensity 9300, include logic such as ARM Power Policy Units that are configured by systems such as an ARM System Control Processor.<sup>23</sup>

- 83. On information and belief, the '197 Patent Accused Products use ARM's Intelligent Power Allocation technology in conjunction with the Power Policy units and a System Control Processor or Resource and Power Manger to receive a workload configuration input regarding a

<sup>&</sup>lt;sup>23</sup> "Arm DynamIQ Shared Unit-110", page 78, *available at* https://documentationservice.arm.com/static/62bb28beb334256d9ea8cc32; *id.*, page 51; *id.*, page 80; *id.*, page 77.

workload, receive a plurality of energy performance bias (EPB) values and determine a global EPB value based thereon, and update at least one setting of at least one of the plurality of power management features based on the workload configuration input and the global EPB value.

84. For example, on information and belief, in the Dimensity 9300 SoCs, the Intelligent Power Allocation logic receives real-time CPU and GPU performance requests and based on the requested workload configuration and power models to cause settings of Power Policy Units to be updated to maximize requested performance without exceeding the Thermal Design Power for the SoC<sup>24</sup>:

Figure 7 ARM Intelligent Power Allocation

- 85. Further, on information and belief, MediaTek has actively induced and/or contributed to infringement of at least Claim 1 of the '197 Patent in violation of at least 35 U.S.C. § 271(b), (c), and (f).

- 86. Users of the '197 Patent Accused Products directly infringe at least Claim 1 of the '197 Patent when they use the '197 Patent Accused Products in the ordinary, customary, and

<sup>&</sup>lt;sup>24</sup> Wang, *supra* note 8, pp. 11-14.

intended way. On information and belief, MediaTek's inducements in violation of 35 U.S.C. § 271(b) include, without limitation and with specific intent to encourage infringement, knowingly inducing consumers to use the '197 Patent Accused Products within the United States in the ordinary, customary, and intended way by, directly or through intermediaries, supplying the '197 Patent Accused Products to consumers within the United States and instructing and encouraging such customers to use the '197 Patent Accused Products in the ordinary, customary, and intended way, which MediaTek knew infringes at least Claim 1 of the '197 Patent, or, alternatively, was willfully blind to the infringement.

- 87. On information and belief, MediaTek's inducements in violation of 35 U.S.C. § 271(b) further include, without limitation and with specific intent to encourage the infringement, knowingly inducing customers to commit acts of infringement with respect to the '197 Patent Accused Products within the United States, by, directly or through intermediaries, instructing and encouraging such customers to import, make, use, sell, offer to sell, or otherwise commit acts of infringement with respect to the '197 Patent Accused Products in the United States, which MediaTek knew infringes at least Claim 1 of the '197 Patent, or, alternatively, was willfully blind to the infringement.

- 88. On information and belief, in violation of 35 U.S.C. § 271(c), MediaTek's contributory infringement further includes offering to sell or selling within the United States, or importing into the United States, components of the patented invention of at least Claim 1 of the '197 Patent, constituting a material part of the invention. On information and belief, MediaTek knows and has known the same to be especially made or especially adapted for use in an infringement of the '197 Patent, and such components are not a staple article or commodity of commerce suitable for substantial noninfringing use.

- 89. On information and belief, in violation of 35 U.S.C. § 271(f)(1), MediaTek's infringement further includes without authority supplying or causing to be supplied in or from the United States all or a substantial portion of the components of the patented invention of at least Claim 1 of the '197 Patent, where such components are uncombined in whole or in part, in such manner as to actively induce the combination of such components outside of the United States in a manner that would infringe the patent if such combination occurred within the United States.

- 90. On information and belief, in violation of 35 U.S.C. § 271(f)(2), MediaTek's infringement further includes without authority supplying or causing to be supplied in or from the United States components of the patented invention of at least Claim 1 of the '197 Patent that are especially made or especially adapted for use in the invention and not staple articles or commodities of commerce suitable for substantial noninfringing use, where such components are uncombined in whole or in part, knowing that such components are so made or adapted and intending that such components will be combined outside of the United States in a manner that would infringe the patent if such combination occurred within the United States.

- 91. MediaTek is not licensed or otherwise authorized to practice the claims of the '197 Patent.

- 92. Thus, by its acts, MediaTek has injured Daedalus and is liable to Daedalus for directly and/or indirectly infringing one or more claims of the '197 Patent, whether literally or under the doctrine of equivalents, including without limitation Claim 1.

- 93. On information and belief, MediaTek has known about the '197 Patent at least since August 23, 2022.<sup>25</sup> At a minimum, MediaTek has knowledge of the '197 Patent at least as of the filing of this Complaint. Accordingly, MediaTek's infringement of the '197 Patent has been and

<sup>&</sup>lt;sup>25</sup> Daedalus Prime LLC v. Mazda Motor Corp., et al., No. 22-cv-01108 (D. Del. Aug. 23, 2022).

continues to be deliberate, intentional, and willful, and this is therefore an exceptional case warranting an award of enhanced damages and attorneys' fees and costs pursuant to 35 U.S.C. §§ 284 and 285.

- 94. As a result of MediaTek's infringement of the '197 Patent, Daedalus has suffered monetary damages, and seeks recovery, in an amount to be proven at trial, adequate to compensate for MediaTek's infringement, but in no event less than a reasonable royalty with interest and costs.

- 95. On information and belief, MediaTek will continue to infringe the '197 Patent unless enjoined by this Court. MediaTek's infringement of Daedalus' rights under the '197 Patent will continue to damage Daedalus, causing irreparable harm for which there is no adequate remedy at law, unless enjoined by this Court.

#### THIRD COUNT

## (Infringement of U.S Patent No. 10,740,281)

- 96. Daedalus incorporates by reference the allegations set forth in Paragraphs 1-95 of the Complaint as though fully set forth herein.

- 97. The claims of the '281 Patent are valid and enforceable.

- 98. On information and belief, in violation of 35 U.S.C. § 271(a), MediaTek has directly infringed and continues to directly infringe one or more claims of the '281 Patent, including at least Claim 8 of the '281 Patent, in the state of Texas, in this judicial district, and elsewhere in the United States by, among other things, making, using, selling, offering for sale, and/or importing into the United States products that embody one or more of the inventions claimed in the '281 Patent, including but not limited to its electronic devices containing SoCs or microprocessors based on or derived from ARMv8.2 architecture, as well as subsequent revisions

to the ARM architecture such as the ARMv9 architecture, such as the Dimensity 9000 SoCs, and all reasonably similar products (the "'281 Patent Accused Products").

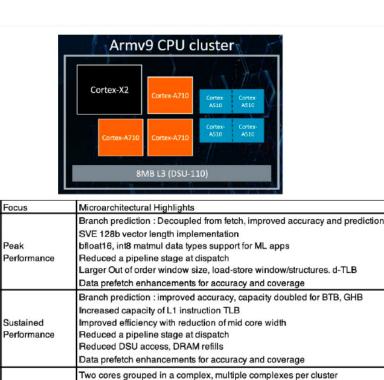

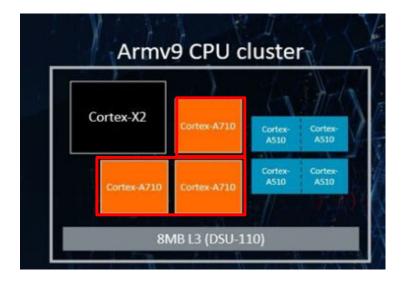

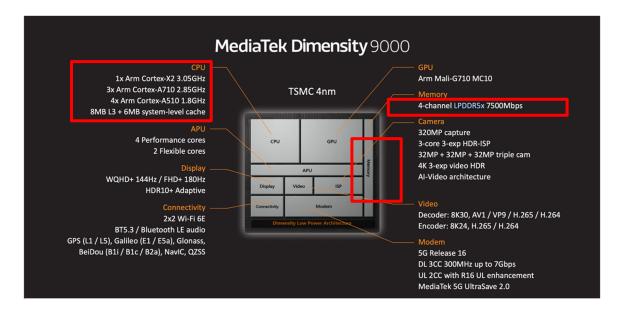

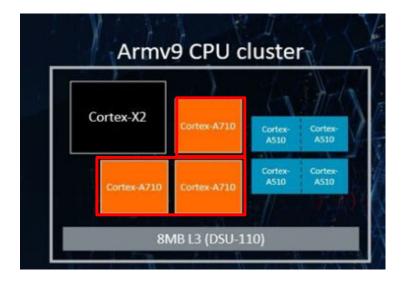

- 99. Each of the '281 Patent Accused Products comprises a multi-core processor. For example, the Dimensity 9000 contains one or more microprocessors based on or derived from the ARM Cortex-X2 architecture, the ARM Cortex-A710 architecture and the ARM Cortex-A510 architecture.

- 100. Each of the '281 Patent Accused Products comprises a first plurality of cores and a second plurality of cores.

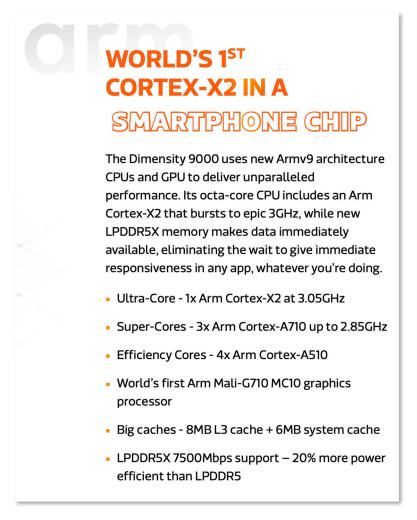

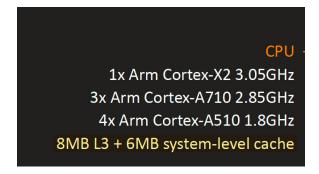

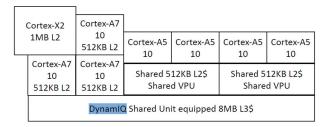

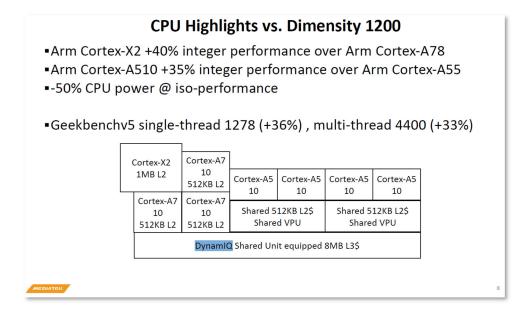

- 101. Specifically, the '281 Patent Accused Products include one or more clusters comprising a plurality of cores. For example, Dimensity 9000 SoCs comprise three Cortex-A710 cores and four Cortex-A510 cores<sup>26</sup>:

<sup>&</sup>lt;sup>26</sup> https://mediatek-marketing.files.svdcdn.com/production/documents/Dimensity-9000-Infographic.pdf; https://i.mediatek.com/dimensity-9000; Nayak, et al., *supra* note 2.

# WORLD'S 1<sup>ST</sup> CORTEX-X2 IN A

# SMARTPHONE CHIP

The Dimensity 9000 uses new Armv9 architecture CPUs and GPU to deliver unparalleled performance. Its octa-core CPU includes an Arm Cortex-X2 that bursts to epic 3GHz, while new LPDDR5X memory makes data immediately available, eliminating the wait to give immediate responsiveness in any app, whatever you're doing.

- Ultra-Core 1x Arm Cortex-X2 at 3.05GHz

- Super-Cores 3x Arm Cortex-A710 up to 2.85GHz

- Efficiency Cores 4x Arm Cortex-A510

- World's first Arm Mali-G710 MC10 graphics processor

- Big caches 8MB L3 cache + 6MB system cache

- LPDDR5X 7500Mbps support 20% more power efficient than LPDDR5

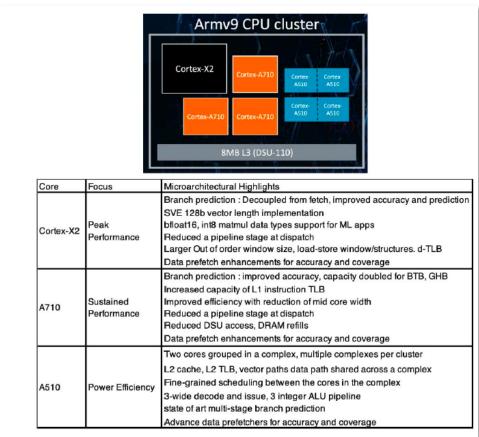

Figure 2.5.2: ARMv9 CPU cluster.

- 102. Each of the '281 Patent Accused Products comprises a first plurality of cores and a second plurality of cores that support a same instruction set.

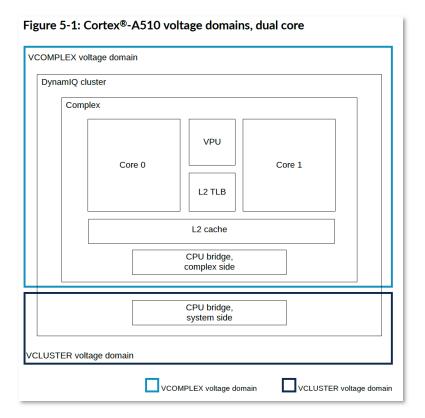

- 103. For example, Dimensity 9000 SoCs comprise clusters of Cortex-A710 cores and Cortex-A510 cores, all supporting the ARMv9 instruction set<sup>27</sup>:

# 2 The Cortex®-A510 core

The Cortex®-A510 core is a high-efficiency, low-power product that implements the Arm®v9.0-A architecture. The Arm®v9.0-A architecture extends the architecture defined in the Arm®v8-A architectures up to Arm®v8.5-A.

<sup>&</sup>lt;sup>27</sup> Arm® Cortex®-A510 Core Technical Reference Manual, p. 22-23; Arm® Cortex®-A710 Core Technical Reference Manual, p. 22-23; Nayak, et al., *supra* note 2.

# 2.1 Cortex®-A510 core features

The Cortex®-A510 core might be used in standalone DynamlQ $^{\text{M}}$  configurations where a homogenous DSU-110 DynamlQ $^{\text{M}}$  cluster includes one to eight Cortex $^{\text{R}}$ -A510 cores. The Cortex $^{\text{R}}$ -A510 core might also be used as a high efficiency core or a high-performance core in a heterogenous DSU-110 DynamlQ $^{\text{M}}$  cluster.

However, regardless of the cluster configuration, the Cortex®-A510 core always has the same features.

#### Core features

• Implementation of the Arm®v9.0-A A64 instruction set

# 2 The Cortex®-A710 core

The Cortex®-A710 core is a high-performance, low-power, and constrained area product that implements the Arm®v9.0-A architecture. The Arm®v9.0-A architecture extends the architecture defined in the Armv8-A architectures up to Arm®v8.5-A. The Cortex®-A710 core targets clamshell and premium high-end smartphone applications.

# 2.1 Cortex®-A710 core features

The Cortex®-A710 core might be used in standalone DynamlQ™ configurations, that is in a homogenous cluster of one to four Cortex®-A710 cores. It might also be used either as the high-performance or balanced-performance core in a heterogenous cluster.

However, regardless of the cluster configuration, the Cortex®-A710 core always has the same features.

#### Core features

• Implementation of the Armv9-A A32, T32, and A64 instruction sets

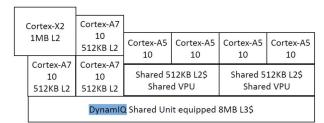

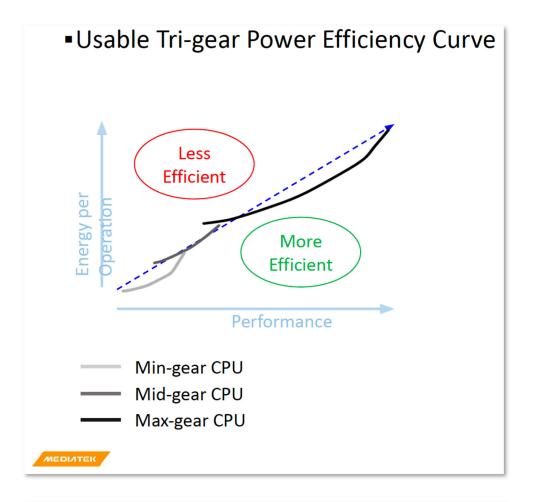

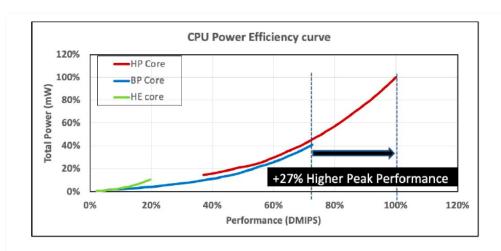

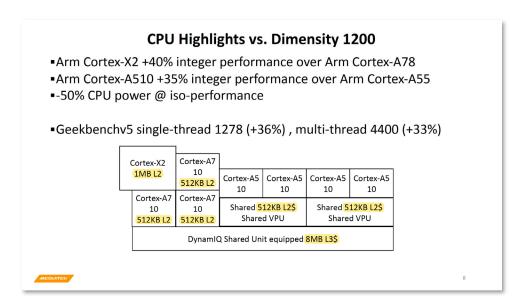

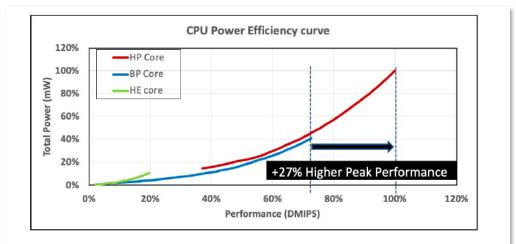

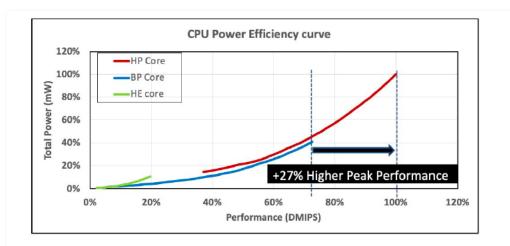

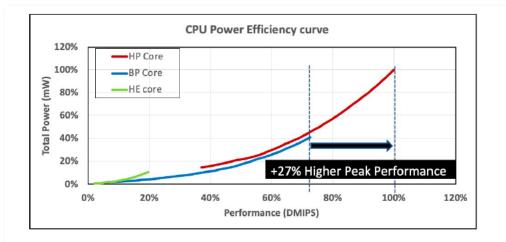

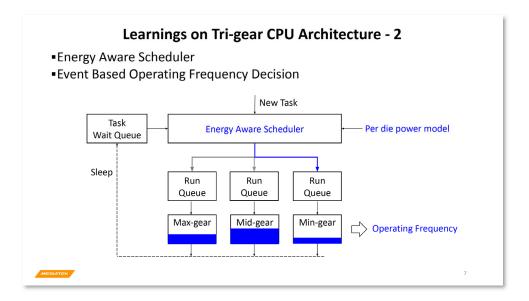

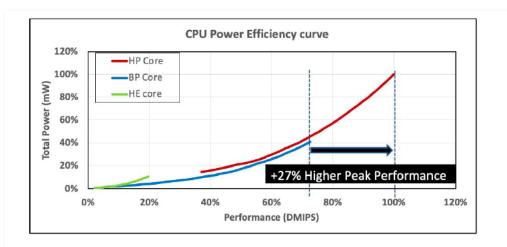

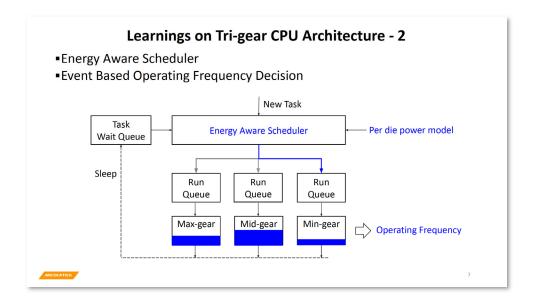

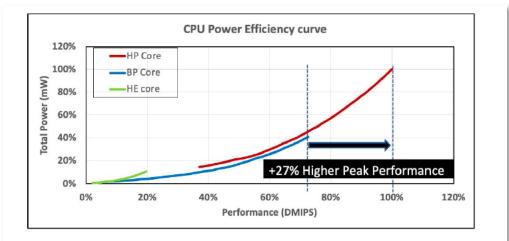

The heterogeneous CPU complex, shown in Fig. 2.5.2, is organized into 3 gears. The 1st gear is a single HP core which utilizes the ARMv9 Cortex-X2 microarchitecture with 64KB L1 instruction cache, 64KB L1 data cache, and a 1MB private L2 cache. The 2st gear consists of three Balanced Performance (BP) cores utilizing the ARMv9 Cortex-A710 architecture, each with a 64KB L1 instruction cache, a 64KB L1 data cache, and a 512KB private L2 cache. The 3st gear features four High Efficiency (HE) ARMv9 Cortex-A510 cores [1], with each core using a 64KB L1 instruction cache, 64KB L1 data cache. Further, the HE CPU cores are implemented in pairs to facilitate the sharing of a 512KB L2 cache, floating-point and vector hardware between two CPUs cores, improving area and power efficiency, maintaining full v9 compatibility, without sacrificing performance of key workloads. Finally, an 8MB L3 cache is shared across all the cores of the CPU complex.

All processor cores in the CPU subsystem incorporate the ARMv9 instruction set with key architectural advances. Memory Tagging Extension (MTE) enables greater security by locking data in the memory using a tag which can only be accessed by the correct key held by the pointer accessing the memory location, as shown in Fig. 2.5.1. Further, a Scalable Vector Extension 2 (SVE2) allows a scalable vector length in multiples of 128b, up to 2048b, enabling increased DSP and ML vector-processing capabilities, as shown in Fig. 2.5.1.

- 104. Each of the '281 Patent Accused Products comprises a first plurality of cores that are higher performance and consume more power than a second plurality of cores.

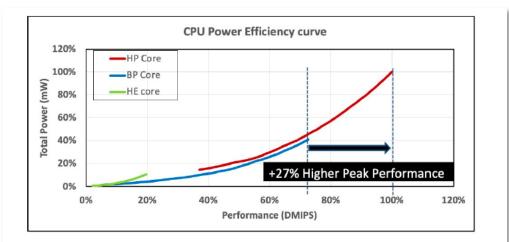

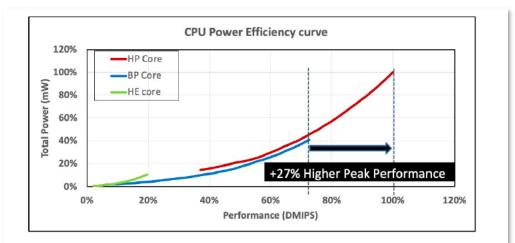

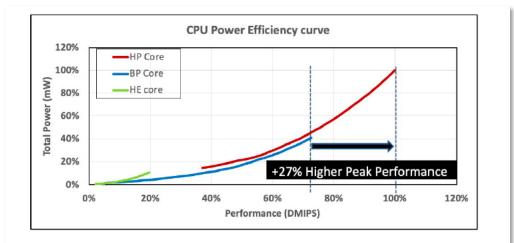

- 105. For example, the Dimensity 9000 SoCs include a plurality of "Balanced Performance (BP)" Cortex-A710 cores and a plurality of "High Efficiency (HE)" Cortex-A510 cores., wherein the Cortex-A710 cores are higher performance and consume more power than the Cortex-A510 cores<sup>28</sup>:

The heterogeneous CPU complex, shown in Fig. 2.5.2, is organized into 3 gears. The 1<sup>st</sup> gear is a single HP core which utilizes the ARMv9 Cortex-X2 microarchitecture with 64KB L1 instruction cache, 64KB L1 data cache, and a 1MB private L2 cache. The 2<sup>nd</sup> gear consists of three Balanced Performance (BP) cores utilizing the ARMv9 Cortex-A710 architecture, each with a 64KB L1 instruction cache, a 64KB L1 data cache, and a 512KB private L2 cache. The 3<sup>rd</sup> gear features four High Efficiency (HE) ARMv9 Cortex-A510 cores [1], with each core using a 64KB L1 instruction cache, 64KB L1 data cache. Further, the HE CPU cores are implemented in pairs to facilitate the sharing of a 512KB L2 cache, floating-point and vector hardware between two CPUs cores, improving area and power efficiency, maintaining full v9 compatibility, without sacrificing performance of key workloads. Finally, an 8MB L3 cache is shared across all the cores of the CPU complex.

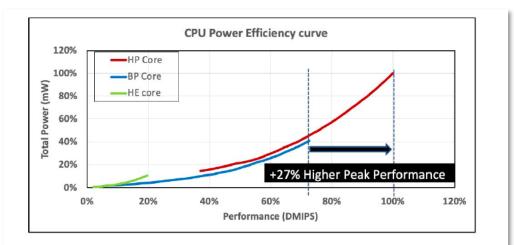

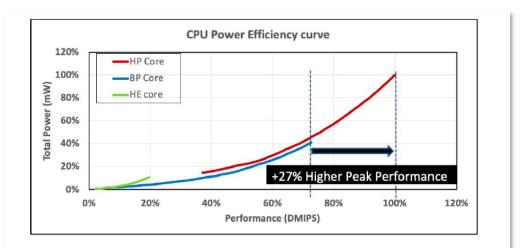

The HP core runs up to 3.4GHz clock speed to meet high-speed compute demands, while the HE cores are optimized to operate efficiently at ultra-low voltage. The BP cores provide a balance of power and performance for average workloads. Depending on the dynamic computing needs, workloads can be seamlessly switched and assigned across different gears of the CPU subsystem enabling maximum power efficiency. Dynamic voltage and frequency scaling (DVFS) is employed along with adaptive voltage scaling to adjust operating voltage and frequency. Figure 2.5.1 demonstrates the power efficiency of the CPU subsystem achieving 27% improvement in single thread performance of the HP core over the BP core.

<sup>&</sup>lt;sup>28</sup> Nayak, et al., *supra* note 2; Aditya Bedi, *The Foundation of Total Compute: First Armv9 Cortex* CPUs (May 25, 2021), https://community.arm.com/arm-community-blogs/b/architectures-and-processors-blog/posts/first-armv9-cpu-cores.

Figure 2.5.1: ARMv9 memory tagging, SVE2 performance chart, CPU power efficiency.

Figure 2.5.2: ARMv9 CPU cluster.

We are also announcing the <u>Arm Cortex-A710</u>. This is our first Armv9 generation "big" CPU, with it providing the best balance of performance and efficiency. Accompanying the "big" Cortex-A710 is the first Armv9 high efficiency "LITTLE" CPU, the <u>Arm Cortex-A510</u>, which is the successor to the highly popular Arm Cortex-A55 CPU.

- 106. Each of the '281 Patent Accused Products comprises a second plurality of cores that have a maximum operating frequency that is less than the maximum operating frequency of each of the first plurality of cores.

- 107. For example, the Dimensity 9000 SoCs include a plurality of Cortex-A510 cores, which have a maximum operating frequency that is less than the maximum operating frequency of the plurality of Cortex-A710 cores.<sup>29</sup>.

Figure 2.5.1: ARMv9 memory tagging, SVE2 performance chart, CPU power efficiency.

<sup>&</sup>lt;sup>29</sup> Rosinger & Pradhan, *supra* note 14, p 3; Nayak, et al., *supra* note 2; https://i.mediatek.com/dimensity-9000; https://mediatek-marketing.files.svdcdn.com/production/documents/Dimensity-9000-Infographic.pdf.

- 108. Each of the '281 Patent Accused Products comprises a caching layer shared by the first plurality of cores and the second plurality of cores.

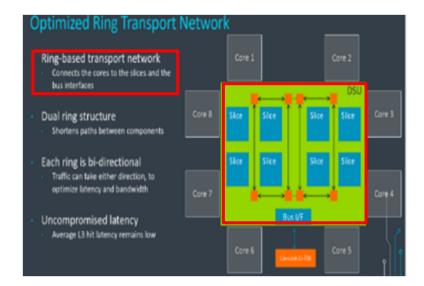

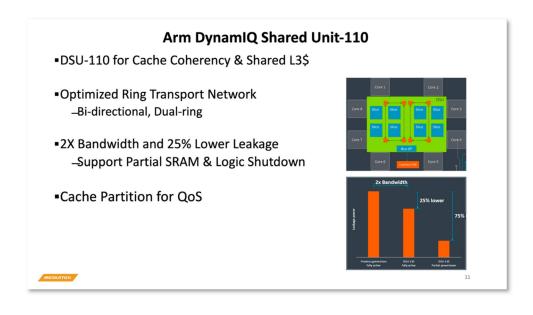

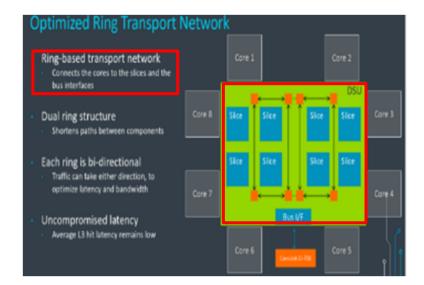

- 109. For example, the Dimensity 9000 SoCs include a DynamIQ Shared Unit (DSU). The DSU couples the plurality of cores to the shared L3 cache memory<sup>30</sup>.

<sup>&</sup>lt;sup>30</sup> Rosinger & Pradhan, *supra* note 14, pp. 3, 8, 11; Nayak, et al., *supra* note 2.

1x Arm Cortex-X2 3.05GHz 3x Arm Cortex-A710 2.85GHz 4x Arm Cortex-A510 1.8GHz 8MB L3 + 6MB system-level cache

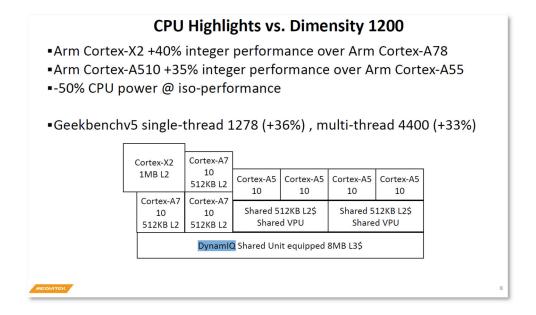

# CPU Highlights vs. Dimensity 1200

- Arm Cortex-X2 +40% integer performance over Arm Cortex-A78

- Arm Cortex-A510 +35% integer performance over Arm Cortex-A55

- ■-50% CPU power @ iso-performance

- ■Geekbenchv5 single-thread 1278 (+36%), multi-thread 4400 (+33%)

MEDIATEK

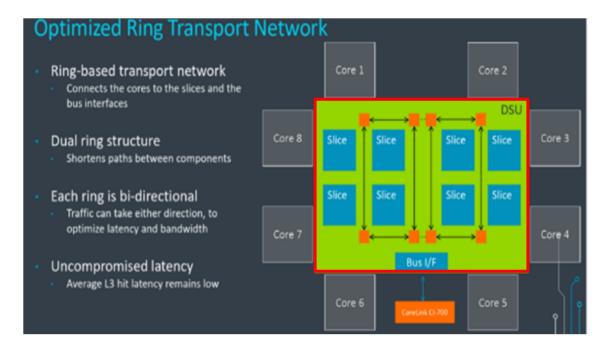

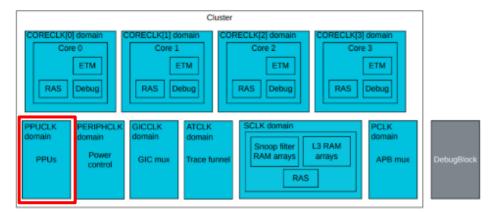

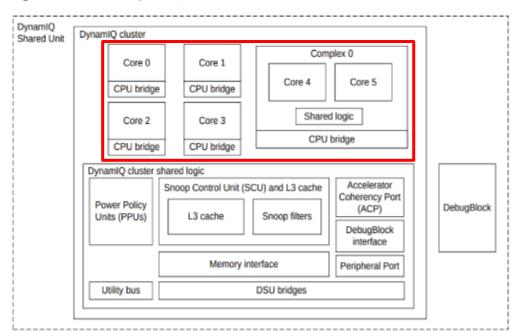

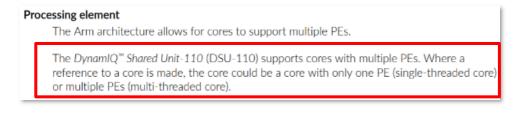

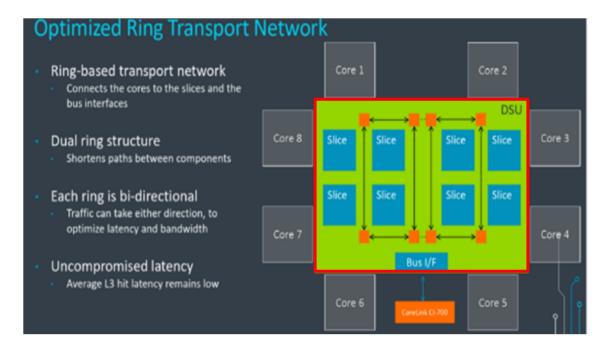

# **Arm DynamIQ Shared Unit-110**

- ■DSU-110 for Cache Coherency & Shared L3\$

- Optimized Ring Transport NetworkBi-directional, Dual-ring

- 2X Bandwidth and 25% Lower LeakageSupport Partial SRAM & Logic Shutdown

- Cache Partition for QoS

MEDIATEK

The heterogeneous CPU complex, shown in Fig. 2.5.2, is organized into 3 gears. The 1st gear is a single HP core which utilizes the ARMv9 Cortex-X2 microarchitecture with 64KB L1 instruction cache, 64KB L1 data cache, and a 1MB private L2 cache. The 2nd gear consists of three Balanced Performance (BP) cores utilizing the ARMv9 Cortex-A710 architecture, each with a 64KB L1 instruction cache, a 64KB L1 data cache, and a 512KB private L2 cache. The 3nd gear features four High Efficiency (HE) ARMv9 Cortex-A510 cores [1], with each core using a 64KB L1 instruction cache, 64KB L1 data cache. Further, the HE CPU cores are implemented in pairs to facilitate the sharing of a 512KB L2 cache, floating-point and vector hardware between two CPUs cores, improving area and power efficiency, maintaining full v9 compatibility, without sacrificing performance of key workloads. Finally, an 8MB L3 cache is shared across all the cores of the CPU complex.

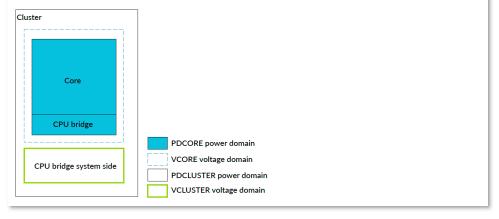

- 110. Each of the '281 Patent Accused Products comprises power management hardware to enable and disable the first plurality of cores and the second plurality of cores, wherein an operating system that executes on the multi-core processor is to monitor a demand for the multi-core processor and control a core mix of the first plurality of cores and the second plurality of cores based on the demand with the power management hardware.

- 111. For example, the Dimensity 9000 SoCs include an Energy Aware Scheduler and other logic such as ARM Power Policy Units that are configured by systems such as an ARM System Control Processor.<sup>31</sup>

<sup>&</sup>lt;sup>31</sup> Rosinger & Pradhan, *supra* note 14, p. 7; Nayak, et al., *supra* note 2.

The HP core runs up to 3.4GHz clock speed to meet high-speed compute demands, while the HE cores are optimized to operate efficiently at ultra-low voltage. The BP cores provide a balance of power and performance for average workloads. Depending on the dynamic computing needs, workloads can be seamlessly switched and assigned across different gears of the CPU subsystem enabling maximum power efficiency. Dynamic voltage and frequency scaling (DVFS) is employed along with adaptive voltage scaling to adjust operating voltage and frequency. Figure 2.5.1 demonstrates the power efficiency of the CPU subsystem achieving 27% improvement in single thread performance of the HP core over the BP core.

Figure 2.5.1: ARMv9 memory tagging, SVE2 performance chart, CPU power efficiency.

In summary, a tri-gear ARMv9 CPU subsystem for a flagship 5G smartphone SoC is introduced with a high-performance core achieving 3.4GHz at robust yield and delivering up to 27% higher peak performance through microarchitectural and implementation advancements. Further, circuit innovation to enable continuous monitoring of on-die power supply is shown. Finally, a new variation aware AVS technology is introduced to further improve CPU power efficiency.

112. On information and belief, the '281 Patent Accused Products use ARM's Intelligent Power Allocation technology in conjunction with the Power Policy Units and a System Control Processor or Resource and Power Manger to monitor demand and enable and disable the first plurality of cores and the second plurality of cores.<sup>32</sup>

<sup>&</sup>lt;sup>32</sup> "Arm DynamIQ Shared Unit-110" at 36-37.

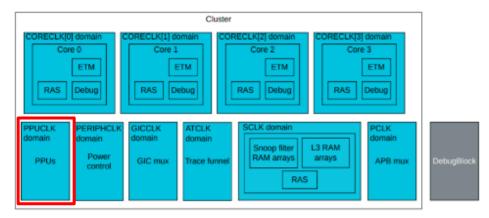

# Power management and Power Policy Units The DynamIQ™ cluster shared logic integrates several Power management and Power Policy Units (PPUs) to control power modes and resets. The PPUs can be programmed to directly select a Copyright © 2019-2022 Arm Limited (or its affiliates). All rights reserved. Non-Confidential Page 36 of 862 Arm® DynamIQ™ Shared Unit-110 Technical Reference Manual Document ID: 101381\_0400\_11\_en Issue: 11 Technical overview specific power mode or can be programmed to autonomously switch between power modes within a specified range, based on the requirements of the cluster. The PPUs can be programmed from your System Control Processor (SCP) using the utility bus to access them.

113. For example, on information and belief, in the Dimensity 9000 SoCs, the Power Policy Units are utilized to enable and disable the first plurality of cores and the second plurality of cores <sup>33</sup>:

# 5.1 Power management in the DSU-110

The *DynamIQ™ Shared Unit-110* (DSU-110) provides various mechanisms to control both dynamic and static power dissipation. These mechanisms are associated with a set of power domains, power modes, and operational modes. Some of these mechanisms are brought under software control using *Power Policy Units* (PPUs).

The power management techniques employed by the DSU-110 and cores in the cluster include:

- · Internal core clock gating where different internal parts of the core are clock idle

- Per-core Dynamic Voltage and Frequency Scaling (DVFS)

- Powerdown of components of the cluster which can include:

- Cores

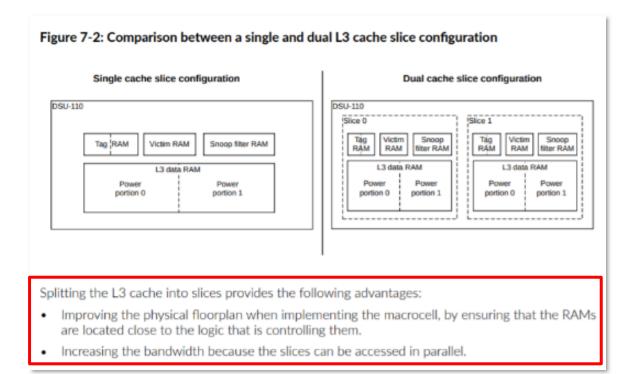

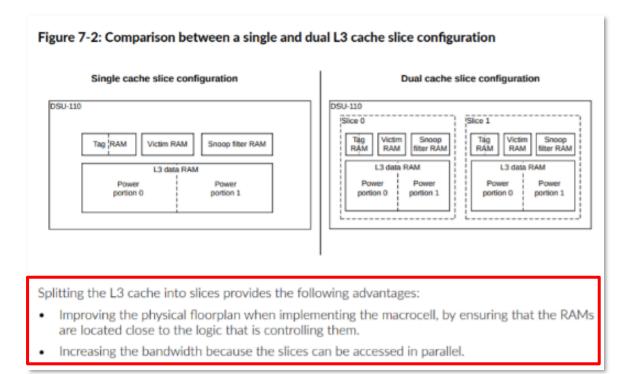

- All the L3 cache or parts of the L3 cache. See 5.4.1 L3 cache RAM powerdown on page 57 and 5.4.2 L3 cache slice powerdown on page 61.

- Retention which is a low-power mode that retains the register and RAM state. Retention can be applied to the following components of the cluster:

- Cache RAMs in the cores

- · All of the L3 cache or parts of the L3 cache

<sup>&</sup>lt;sup>33</sup> *Id*. at 50.

- 114. Further, on information and belief, MediaTek has actively induced and/or contributed to infringement of at least Claim 8 of the '281 Patent in violation of at least 35 U.S.C. § 271(b), (c), and (f).

- 115. Users of the '281 Patent Accused Products directly infringe at least Claim 8 of the '281 Patent when they use the '281 Patent Accused Products in the ordinary, customary, and intended way. On information and belief, MediaTek's inducements in violation of 35 U.S.C. § 271(b) include, without limitation and with specific intent to encourage infringement, knowingly inducing consumers to use the '281 Patent Accused Products within the United States in the ordinary, customary, and intended way by, directly or through intermediaries, supplying the '281 Patent Accused Products to consumers within the United States and instructing and encouraging such customers to use the '281 Patent Accused Products in the ordinary, customary, and intended way, which MediaTek knew infringes at least Claim 8 of the '281 Patent, or, alternatively, was willfully blind to the infringement.

- 116. On information and belief, MediaTek's inducements in violation of 35 U.S.C. § 271(b) further include, without limitation and with specific intent to encourage the infringement, knowingly inducing customers to commit acts of infringement with respect to the '281 Patent Accused Products within the United States, by, directly or through intermediaries, instructing and encouraging such customers to import, make, use, sell, offer to sell, or otherwise commit acts of infringement with respect to the '281 Patent Accused Products in the United States, which MediaTek knew infringes at least Claim 8 of the '281 Patent, or, alternatively, was willfully blind to the infringement.

- 117. On information and belief, in violation of 35 U.S.C. § 271(c), MediaTek's contributory infringement further includes offering to sell or selling within the United States, or

importing into the United States, components of the patented invention of at least Claim 8 of the '281 Patent, constituting a material part of the invention. On information and belief, MediaTek knows and has known the same to be especially made or especially adapted for use in an infringement of the '281 Patent, and such components are not a staple article or commodity of commerce suitable for substantial noninfringing use.

- 118. On information and belief, in violation of 35 U.S.C. § 271(f)(1), MediaTek's infringement further includes without authority supplying or causing to be supplied in or from the United States all or a substantial portion of the components of the patented invention of at least Claim 8 of the '281 Patent, where such components are uncombined in whole or in part, in such manner as to actively induce the combination of such components outside of the United States in a manner that would infringe the patent if such combination occurred within the United States.

- 119. On information and belief, in violation of 35 U.S.C. § 271(f)(2), MediaTek's infringement further includes without authority supplying or causing to be supplied in or from the United States components of the patented invention of at least Claim 8 of the '281 Patent that are especially made or especially adapted for use in the invention and not staple articles or commodities of commerce suitable for substantial noninfringing use, where such components are uncombined in whole or in part, knowing that such components are so made or adapted and intending that such components will be combined outside of the United States in a manner that would infringe the patent if such combination occurred within the United States.

- 120. MediaTek is not licensed or otherwise authorized to practice the claims of the '281 Patent.

- 121. Thus, by its acts, MediaTek has injured Daedalus and is liable to Daedalus for directly and/or indirectly infringing one or more claims of the '281 Patent, whether literally or under the doctrine of equivalents, including without limitation Claim 8.

- 122. On information and belief, MediaTek has known about the '281 Patent at least since August 23, 2022.<sup>34</sup> At a minimum, MediaTek has knowledge of the '281 Patent at least as of the filing of this Complaint. Accordingly, MediaTek's infringement of the '281 Patent has been and continues to be deliberate, intentional, and willful, and this is therefore an exceptional case warranting an award of enhanced damages and attorneys' fees and costs pursuant to 35 U.S.C. §§ 284 and 285.

- 123. As a result of MediaTek's infringement of the '281 Patent, Daedalus has suffered monetary damages, and seeks recovery, in an amount to be proven at trial, adequate to compensate for MediaTek's infringement, but in no event less than a reasonable royalty with interest and costs.

- 124. On information and belief, MediaTek will continue to infringe the '281 Patent unless enjoined by this Court. MediaTek's infringement of Daedalus' rights under the '281 Patent will continue to damage Daedalus, causing irreparable harm for which there is no adequate remedy at law, unless enjoined by this Court.

## **FOURTH COUNT**

# (Infringement of U.S Patent No. 8,984,228)

- 125. Daedalus incorporates by reference the allegations set forth in Paragraphs 1-124 of the Complaint as though fully set forth herein.

- 126. The claims of the '228 Patent are valid and enforceable.

<sup>&</sup>lt;sup>34</sup> Daedalus Prime LLC v. Mazda Motor Corp., et al., No. 22-cv-01108 (D. Del. Aug. 23, 2022).

- 127. On information and belief, in violation of 35 U.S.C. § 271(a), MediaTek has directly infringed and continues to directly infringe one or more claims of the '228 Patent, including at least Claims 1 and 11 of the '228 Patent, in the state of Texas, in this judicial district, and elsewhere in the United States by, among other things, making, using, selling, offering for sale, and/or importing into the United States products that embody one or more of the inventions claimed in the '228 Patent, including but not limited to its electronic devices containing SoCs or microprocessors based on or derived from ARMv8.2 architecture, as well as subsequent revisions to the ARM architecture such as the ARMv9 architecture, such as the Dimensity 9000 SoCs, and all reasonably similar products (the "'228 Patent Accused Products').

- 128. Each of the '228 Patent Accused Products comprises a multi-core processor including a plurality of cores. For example, the Dimensity 9000 contains one or more microprocessors based on or derived from the ARM Cortex-X2 architecture, the ARM Cortex-A710 architecture and the ARM Cortex-A510 architecture.

- 129. Specifically, the '228 Patent Accused Products include one or more clusters comprising a plurality of cores. For example, Dimensity 9000 SoCs comprise a Cortex-X2 core, three Cortex-A710 cores and four Cortex-A510 cores<sup>35</sup>:

<sup>&</sup>lt;sup>35</sup> https://mediatek-marketing.files.svdcdn.com/production/documents/Dimensity-9000-Infographic.pdf; https://i.mediatek.com/dimensity-9000; Nayak, et al., *supra* note 2.

# WORLD'S 1<sup>ST</sup> CORTEX-X2 IN A

# SMARTPHONE CHIP

The Dimensity 9000 uses new Armv9 architecture CPUs and GPU to deliver unparalleled performance. Its octa-core CPU includes an Arm Cortex-X2 that bursts to epic 3GHz, while new LPDDR5X memory makes data immediately available, eliminating the wait to give immediate responsiveness in any app, whatever you're doing.

- Ultra-Core 1x Arm Cortex-X2 at 3.05GHz

- Super-Cores 3x Arm Cortex-A710 up to 2.85GHz

- Efficiency Cores 4x Arm Cortex-A510

- World's first Arm Mali-G710 MC10 graphics processor

- Big caches 8MB L3 cache + 6MB system cache

- LPDDR5X 7500Mbps support 20% more power efficient than LPDDR5

Figure 2.5.2: ARMv9 CPU cluster.

- 130. Each of the '228 Patent Accused Products comprises a shared cache memory.

- 131. For example, the Dimensity 9000 SoCs include a DynamIQ Shared Unit (DSU). The DSU couples the plurality of cores to the shared cache memory<sup>36</sup>.

<sup>&</sup>lt;sup>36</sup> Rosinger & Pradhan, *supra* note 14, pp. 3, 8, 11; Nayak, et al., *supra* note 2.

# CPU Highlights vs. Dimensity 1200

- Arm Cortex-X2 +40% integer performance over Arm Cortex-A78

- Arm Cortex-A510 +35% integer performance over Arm Cortex-A55

- ■-50% CPU power @ iso-performance

- Geekbenchv5 single-thread 1278 (+36%), multi-thread 4400 (+33%)

MEDIATEK

# **Arm DynamIQ Shared Unit-110**

- ■DSU-110 for Cache Coherency & Shared L3\$

- Optimized Ring Transport NetworkBi-directional, Dual-ring

- 2X Bandwidth and 25% Lower LeakageSupport Partial SRAM & Logic Shutdown

- Cache Partition for QoS

MEDIATEK

The heterogeneous CPU complex, shown in Fig. 2.5.2, is organized into 3 gears. The 1st gear is a single HP core which utilizes the ARMv9 Cortex-X2 microarchitecture with 64KB L1 instruction cache, 64KB L1 data cache, and a 1MB private L2 cache. The 2nd gear consists of three Balanced Performance (BP) cores utilizing the ARMv9 Cortex-A710 architecture, each with a 64KB L1 instruction cache, a 64KB L1 data cache, and a 512KB private L2 cache. The 3nd gear features four High Efficiency (HE) ARMv9 Cortex-A510 cores [1], with each core using a 64KB L1 instruction cache, 64KB L1 data cache. Further, the HE CPU cores are implemented in pairs to facilitate the sharing of a 512KB L2 cache, floating-point and vector hardware between two CPUs cores, improving area and power efficiency, maintaining full v9 compatibility, without sacrificing performance of key workloads. Finally, an 8MB L3 cache is shared across all the cores of the CPU complex.

- 132. Each of the '228 Patent Accused Products comprises an integrated input/output (IIO) module to interface between the multicore processor and at least one IO device coupled to the multicore processor.