### IN THE UNITED STATES DISTRICT COURT FOR THE EASTERN DISTRICT OF TEXAS SHERMAN DIVISION

TURBOCODE LLC,

Plaintiff,

v.

**BEC TECHNOLOGIES INC.,**

Defendant.

C.A. No. 4:24-cv-357

JURY TRIAL DEMANDED

PATENT CASE

## **ORIGINAL COMPLAINT FOR PATENT INFRINGEMENT**

Plaintiff TurboCode LLC files this Original Complaint for Patent Infringement against BEC Technologies Inc., and would respectfully show the Court as follows:

## I. <u>THE PARTIES</u>

1. Plaintiff TurboCode LLC ("TurboCode" or "Plaintiff") is a Texas limited liability company with its address at 6000 Shepherd Mountain Cove, Suite #1604, Austin Texas 78730.

2. On information and belief, Defendant BEC Technolgoies Inc. ("Defendant") is a corporation organized and existing under the laws of California with a place of business at 3301 Matrix Dr., STE 200, Richardson, TX 75082. Defendant has a registered agent Chia Hsing Lin at 14524 Blakehill Dr., Frisco, TX 75035.

## II. JURISDICTION AND VENUE

3. This action arises under the patent laws of the United States, Title 35 of the United States Code. This Court has subject matter jurisdiction of such action under 28 U.S.C. §§ 1331 and 1338(a).

4. On information and belief, Defendant is subject to this Court's specific and general personal jurisdiction, pursuant to due process and the Texas Long-Arm Statute, due at least to its

1

#### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 2 of 54 PageID #: 2

business in this forum, including at least a portion of the infringements alleged herein at 3301 Matrix Dr., STE 200, Richardson, TX 75082.

5. Without limitation, on information and belief, within this state, Defendant used the patented invention thereby committing, and continuing to commit, acts of patent infringement alleged herein. In addition, on information and belief, Defendant derived revenues from its infringing acts occurring within Texas. Further, on information and belief, Defendant is subject to the Court's general jurisdiction, including from regularly doing or soliciting business, engaging in other persistent courses of conduct, and deriving substantial revenue from goods and services provided to persons or entities in Texas. Further, on information and belief, Defendant is subject to the Court's personal jurisdiction at least due to its sale of products and/or services within Texas. Defendant committed such purposeful acts and/or transactions in Texas such that it reasonably should know and expect that it could be haled into this Court as a consequence of such activity.

6. Venue is proper in this district under 28 U.S.C. § 1400(b). On information and belief, Defendant maintains a places of business in Texas at 3301 Matrix Dr., STE 200, Richardson, TX 75082. On information and belief, from and within this District Defendant committed at least a portion of the infringements at issue in this case.

7. For these reasons, personal jurisdiction exists and venue is proper in this Court under 28 U.S.C. § 1400(b).

### III. <u>COUNT I</u> (PATENT INFRINGEMENT OF UNITED STATES PATENT NO. 6,813,742)

8. Plaintiff incorporates the above paragraphs herein by reference.

9. On November 2, 2004, the USPTO duly and legally issued U.S. Patent No. 6,813,742 ("the '742 Patent" or "Patent-in-Suit"), entitled "High Speed Turbo Codes Decoder for 3G Using Pipelined SISO Log-Map Decoders Architecture." The '742 patent was the subject of a

2

#### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 3 of 54 PageID #: 3

reexamination request filed on July 13, 2006. An *Ex Parte* Reexamination Certificate was issued for the '742 patent on February 10, 2009. A true and correct copy of the '742 Patent with its *Ex Parte* Reexamination Certificate is attached hereto as Exhibit 1.

10. TurboCode is the assignee of all right, title, and interest in the '742 patent, including all rights to enforce and prosecute actions for infringement and to collect damages for all relevant times against infringers of the '742 Patent. Accordingly, TurboCode possesses the exclusive right and standing to prosecute the present action for infringement of the '742 Patent by Defendant.

11. This case generally relates to decoder architectures and processes for receiving and decoding data in communications devices.

12. **Direct Infringement.** Upon information and belief, Defendant directly infringed claim 6 of the '742 Patent in Texas, and elsewhere in the United States, by performing actions comprising using or performing the claimed method of iteratively decoding a plurality of sequences of received baseband signals by using and/or testing the products, devices, systems, and components of systems that comply with the 3G and/or 4G/LTE standards as disclosed in the 3<sup>rd</sup> Generation Partnership Project ("3GPP") Standard Specifications (releases 8-11) governing cellular wireless communications including, but not limited to, RidgeWave 6900 Series, RidgeWave 4900 Series, RidgeWave 4700AZ, MX-210NP Series, MX-200 Series, MX-200 PL9, GigaConnect 6500 Series, 430M, and MX-100U ("Accused Instrumentalities").

13. Claim 6 of the '742 Patent *Ex Parte* Reexamination Certificate states:

A method of iteratively decoding a plurality of sequences of received baseband signals, the method comprising:

- providing an input buffer comprising at least three shift registers, for receiving an input signal and generating first, second, and third shifted input signals;

- providing first and second soft decision decoders serially coupled in a circular circuit, wherein each decoder processes soft decision from the preceding decoder output data, and wherein the first decoder further

receives the first and second shifted input signals from the input buffer and the second decoder further receives the third shifted input signal from the input buffer;

- providing at least one memory module coupled to an output of each of the first and second soft decision decoders, wherein the output of the memory module associated with the second soft decision decoder is fed back as an input of the first soft decision decoder;

- processing systematic information data and extrinsic information data using the maximum a posteriori (AP) probability algorithm, and/or logarithm approximation algorithm;

- generating soft decision based on the maximum a posteriori (MAP) probability algorithm, and/or logarithm approximation algorithm;

- weighing and storing soft decision information into the corresponding memory module;

- performing, for a predetermined number of times, iterative decoding from the first to the last of multiple decoders, wherein an output from the last soft decision decoder is fed back as an input to the first soft decision decoder, then from the first to the second decoders, and propagate to the last decoder in a circular circuit.

- 14. The Accused Instrumentalities provided or performed a method of iteratively

decoding a plurality of sequences of received baseband signals, as shown below by their

compliance with the 3G and/or 4G/LTE standards disclosed in the 3GPP Standard Specifications:

## **Physical Interface**

- Gigabit LAN Interface with IEEE 802.3at compliant with PoE P.D

- WAN: 3G/4G LTE

(E.g., https://bectechnologies.net/devices/6900/).

# RidgeWave® 6900 Series

Outdoor LTE Wideband Router

#### (E.g., https://bectechnologies.net/devices/6900/).

# RidgeWave® 4900 Series

LTE Advanced Outdoor Router

## (E.g., https://bectechnologies.net/devices/4900/).

#### **Features & Specifications**

#### **Supported Frequency Band**

#### • Model: 4900 R18-25

- CAT 6 with 2CA DL

- LTE Bands: B41 (2496 2690MHz)

- Speeds: Up to 220Mbps DL / 10Mbps UL

Modulation: 64QAM DL / 16QAM UL

- Model: 4900 R21 (Part 96 Authorized FUD)

- Model: 4900 R21 (Part 96 Authorized EUD

- CAT 12 with 3CA DL / 2CA UL

- LTE Bands: B48 (3550 3700MHz) - Speeds: Up to 430Mbps DL / 20Mbps UL

- Modulation: 256QAM DL / 64QAM UL

- Channel Bandwidth

- 1.4MHz / 3MHz / 5MHz/ 10MHz/ 15MHz/ 20MHz

- LTE Antenna

- 4x4 Dual Polarity MIMO

- Antenna Gain

- 12dBi ± 1dBi

## (*E.g.*, <u>https://p0d.b92.myftpupload.com/wp-content/uploads/2021/03/BEC\_RidgeWave\_4900\_</u>

# RidgeWave® 4700AZ

Outdoor LTE Router with Carrier-Grade Wi-Fi Hotspot

| Overview                                                         | Key Features                                                            | Specifications                                                                                     | Documents                                          |

|------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------|

| areas without<br>4700AZ, the i<br>Hotspot. The<br>Wi-Fi technolo | any viable wireline co<br>ndustry's first 4G/LTE<br>BEC 4700AZ integrat | nnectivity? You select<br>Outdoor Router with<br>es the latest generation<br>vith 2 CA Carrier Agg | on of Mobile Wireless and<br>regation and 802.11ac |

| environments.                                                    | ngress of water, humid                                                  | JL-50E rated enclosur                                                                              | e enables it to stand up to                        |

Network operators can support new business models, build differentiated services, and explore new revenue-generating opportunities.

Ideal Applications:

- Outdoor Living Spaces

- Public Venues / Parks

- Campground / RV Park / Marina

- Construction / Industrial Sites

- · Smart Cities and much more

- · Locations without any wireline options

(E.g., https://bectechnologies.net/devices/4700az/).

| Overview                                                                           | Key Features                                                                                                         | Specifications  | Documents |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-----------|

| Carrier Netwo                                                                      | ork Certification: Spri                                                                                              | nt              |           |

| Supported Fre                                                                      | equency Bands                                                                                                        |                 |           |

| <ul> <li>WCDMA</li> <li>Cat. 6 Data</li> <li>LTE Band</li> <li>Max. Out</li> </ul> | A: B1, B2, B3, B4, B5, E<br>ata Rate: 300Mbps(DI<br>dwidth: 5, 10, 15, 20 N<br>itput Power: 23dBm<br>t Power: +23dBm | L) & 50Mbps(UL) | .41       |

|                                                                                    | gation Combinations                                                                                                  |                 |           |

| LTE Band                                                                           | d 1: 1 + 8<br>d 2 : 2 + 2/5/12/13/29                                                                                 |                 |           |

|                                                                                    | d 2 : 2 + 2/5/12/13/29<br>d 3: 3 + 7/20                                                                              | ,<br>,          |           |

|                                                                                    | d 4: 4 + 4/5/12/13/19                                                                                                |                 |           |

|                                                                                    | d 5 : 5 + 2/4/30                                                                                                     |                 |           |

| LTE Band                                                                           | d 7 : 7 + 3/7/20                                                                                                     |                 |           |

| LTE Band                                                                           | d 8: 8 + 1                                                                                                           |                 |           |

| LTE Band                                                                           | d 12:12+2/4/30                                                                                                       |                 |           |

| LTE Band                                                                           | d 13: 13 + 2/4                                                                                                       |                 |           |

| LTE Band                                                                           | d 20:20+3/7                                                                                                          |                 |           |

| LTE Band                                                                           | d 30:30+5/12                                                                                                         |                 |           |

|                                                                                    |                                                                                                                      |                 |           |

LTE Band 41: 41 + 41

#### LTE Antenna

- Embedded MIMO Directional

- Gain: Wideband (6~8dBi)

(E.g., https://bectechnologies.net/devices/4700az/).

Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 9 of 54 PageID #: 9

# **MX-210NP Series**

Mini 4G/LTE X-Range Wi-Fi Router

| Overview                        | Key<br>Features                                              | Models            | Specifications                                                                                     | Documents                      |

|---------------------------------|--------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------|--------------------------------|

| affordable soli<br>210NP Series | utions for busine<br>is the clear choic<br>ons that can sear | ess continuity an | onnectivity need cost<br>d managed failover. Th<br>ons seeking rapidly de<br>o any network deployr | ne BEC MX-<br>ployable, highly |

| fully-featured,                 | integrating mult                                             | tiple Gigabit Eth | nge Wi-Fi Router is ult<br>ernet interfaces, high-<br>re GPS, and Power ove                        | powered Wi-Fi                  |

| A versatile and                 | d feature-rich pla                                           | tform the PEC     | MX-210NP Sories is a                                                                               |                                |

| solution comb<br>competitive pr | •                                                            |                   | nctionality with LTE co                                                                            |                                |

- Primary Connectivity

- Business Continuity/WWAN Failover

- Retail/Pop-up Store Networks

- SD-WAN Deployments

- ATMs/Kiosks/Digital Signage

- M2M/IoT

- Healthcare

- Distance and Remote Learning

(*E.g.*, <u>https://bectechnologies.net/devices/mx210/</u>).

| Overview                                                                                                                                                                                                                              | Key<br>Features             | Models                                                             | Specifications          | Documents |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------|-------------------------|-----------|--|

| <ul> <li>Availability and Resilience</li> <li>Dual-WAN ports (4G &amp; Ethernet WAN)</li> <li>Load balancing - Maximizing bandwidth of outbound traffic</li> <li>Automatic failover and fallback</li> </ul> Supported Frequency Bands |                             |                                                                    |                         |           |  |

| LTE Band<br>(LTE Ban<br>Channel<br>1.4MHz,<br>RF Chara<br>Maximur                                                                                                                                                                     | Bandwidth<br>3MHz, 5MHz, 10 | G/2G fallback o<br>the model varia<br>MHz, 15MHz &<br>:: 23 ± 2dBm | ant, see models section | n)        |  |

# (*E.g.*, <u>https://bectechnologies.net/devices/mx210/</u>).

## Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 11 of 54 PageID #: 11

# MX-200 Series

LTE-Advanced Industrial Router

Overview Models Key Features

Specifications

Documents

The BEC MX-200 Series of 4G LTE-Advanced Industrial Routers are high performance, ultra-compact industrial-grade routers, designed to deliver reliable and secure connectivity between devices across a broad range of M2M/IoT Applications.

The MX-200 features two Gigabit Ethernet interfaces with configurable LAN/WAN options, an RS-232 serial interface enabling serial device connectivity over IP, Active GPS, and enterprise-level functionality such as advanced security mechanisms, Quality of Service (QoS), SPI firewall, integrated VPN, auto-failover for unparalleled uptime and network redundancy. It's managed by BECentral®, BEC's cloud-based device management platform, to extend visibility and maximize deployment efficiency.

Ideal applications:

- Primary Connectivity

- Business Continuity/WWAN Failover

- Retail/Pop-up Store Networks

- SD-WAN Deployments

- ATMs/Kiosks/Digital Signage

- M2M/IoT

- Healthcare

(E.g., https://bectechnologies.net/devices/mx-200/).

| Overview | Key<br>Features | Models |

|----------|-----------------|--------|

|----------|-----------------|--------|

Specifications

Documents

#### MX-200Ae - LTE-Advanced Industrial Router

(Includes: RS-232 Interface and Active GPS feature; But doesn't include: Secured VPN Termination and Dynamic Routing)

#### Network Certification: AT&T, T-mobile (PTCRB), Verizon, and US Cellular

#### Supported Frequency Bands

- LTE Band 1, 2, 3, 4, 5, 7, 8, 12, 13, 20, 25, 26, 29, 30, 41

- LTE FDD (Cat. 6) Data Rate: DL up to 300Mbps & UL up to 50 Mbps

- Channel Bandwidth: 1.4, 3, 5, 10, 15, 20 MHz

- Max. Output Power: 23dBm

- Carrier Aggregation (2CA DL) FDD & TDD

- LTE Antenna: 2×2 DL MIMO

#### MX-200A - LTE-Advanced Industrial Router

(Includes: RS-232 Interface, Active GPS, Secured VPN Termination, and Dynamic Routing)

#### Network Certification: AT&T, T-mobile (PTCRB), Verizon, and US Cellular

#### Supported Frequency Bands

- LTE Band 1, 2, 3, 4, 5, 7, 8, 12, 13, 20, 25, 26, 29, 30, 41

- LTE FDD (Cat. 6) Data Rate: DL up to 300Mbps & UL up to 50 Mbps

- Channel Bandwidth: 1.4, 3, 5, 10, 15, 20 MHz

- Max. Output Power: 23dBm

- Carrier Aggregation (2CA DL) FDD & TDD

- LTE Antenna: 2×2 DL MIMO

(E.g., https://bectechnologies.net/devices/mx-200/).

Advanced Industrial 4G LTE Router

Overview Key Features

Specifications Documents

The BEC MX-200 PL9 Advanced Industrial Router is a high-performance, ultracompact industrial-grade router, designed to deliver reliable and secure connectivity between devices across a broad range of M2M/IoT and industrial communication applications. The ultra-compact platform is specifically designed for limited space installations.

The MX-200 PL9 features two Gigabit Ethernet interfaces with configurable LAN/WAN options, an RS-232 serial interface enabling serial device connectivity over IP, Active GPS, and enterprise-level functionality such as advanced security mechanisms, Quality of Service (QoS), SPI firewall, integrated VPN, auto-failover for unparalleled uptime and network redundancy. It's managed by BECentral®, BEC's cloud-based device management platform, to extend visibility and maximize deployment efficiency.

#### Key Applications:

Private LTE, Utility Broadband, Primary Connectivity, Industrial Communications, M2M/IoT, SCADA, Remote Monitoring/Control

(E.g., https://bectechnologies.net/devices/mx-200pl9/).

## (E.g., https://bectechnologies.net/devices/mx-200pl9/).

# GigaConnect® 6500 Series

Enterprise Multi-Service LTE Router

#### Overview

Key Features

Models

Specifications

Documents

The BEC 6500 series Enterprise Multi-Service LTE Router is a high-performance platform, featuring Dual-WAN interfaces (4G/LTE and GigaConnect® Ethernet WAN), 4-port Gigabit Ethernet Switch, USB 2.0, high-power 802.11ac dual-band Wi-Fi access point, hotspot/captive portal, dynamic routing, and robust Firewall security.

The 6500AEL Series modes range from LTE CAT 4 up to LTE CAT 12 providing unprecedented LTE speeds, bandwidth, and network performance across licensed LTE bands and CBRS shared spectrum commercial deployments.. Dual WAN connectivity allows the 6500AEL Series to support a variety of wired broadband connections types, FTTH, Cable modems, with data rates reaching up to 1Gbps.

(E.g., https://bectechnologies.net/devices/6500/).

| Overview                                                   | Key<br>Features  | Models          | Specifications      | Documents |  |

|------------------------------------------------------------|------------------|-----------------|---------------------|-----------|--|

| Availability an                                            |                  |                 |                     |           |  |

| <ul> <li>Dual-WAN ports (4G &amp; Ethernet WAN)</li> </ul> |                  |                 |                     |           |  |

| <ul> <li>Load bala</li> </ul>                              | ancing – Maximiz | ing bandwidth ( | of outbound traffic |           |  |

| <ul> <li>Auto fail-</li> </ul>                             | over between 40  | G and EWAN      |                     |           |  |

(E.g., https://bectechnologies.net/devices/6500/).

430M

Portable 4G LTE Mobile Hotspot

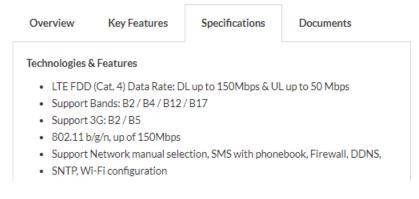

## (E.g., https://bectechnologies.net/devices/430m/).

# Industrial 4G/LTE USB Modem

The BEC MX-100U 4G/LTE Industrial Modem is a rugged, ultra-compact 4G/LTE Modem for Enterprise and IoT/M2M Applications that require secure, always-on LTE connectivity. Designed to accelerate application development and service deployments, lower total cost of ownership (TCO) providing faster ROI, the BEC MX-100U is the perfect balance of performance, ruggedness, reliability, price and secure wireless connectivity for business-critical operations.

#### **KEY FEATURES**

- + Offers 4G/LTE Cellular Connectivity with Single Radio / Dual SIMs

- + Cellular WAN for BEC Multi-WAN Routers (MX-600 & MX-1200)

- + Offer GPS option for 24/7 real-time tracking and location updating

- + Small form factor M2M with affordable price

- + Simplify deployment and easy installation by a single person

- + IP50 Hardened enclosure with Industrial-graded Components

- + BECentral\* (BEC's Cloud Based Remote Management)

- + USB 3.0 connection for the physical interface and power

### (E.g., https://p0d.b92.myftpupload.com/wp-content/uploads/2022/07/BEC-MX-100U\_DSv4.0\_

## <u>2022.pdf</u>).

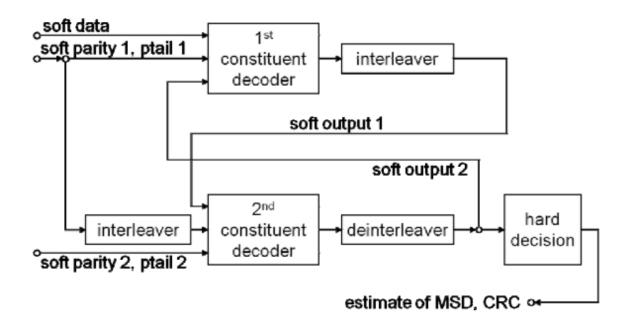

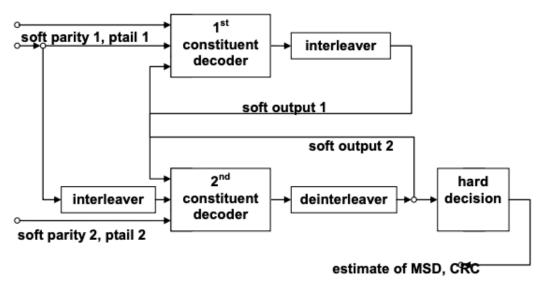

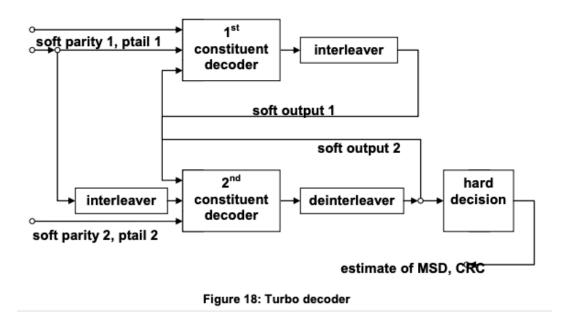

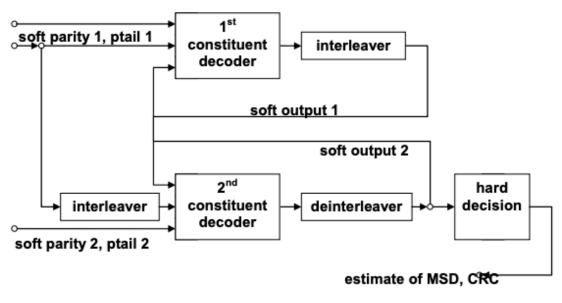

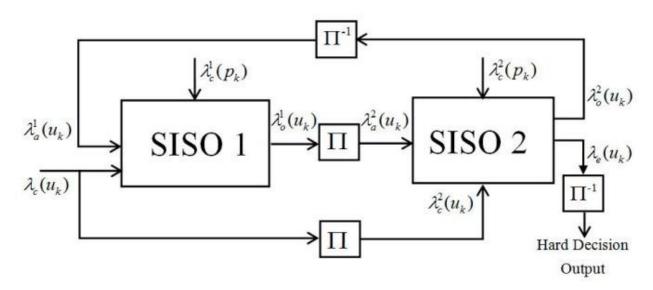

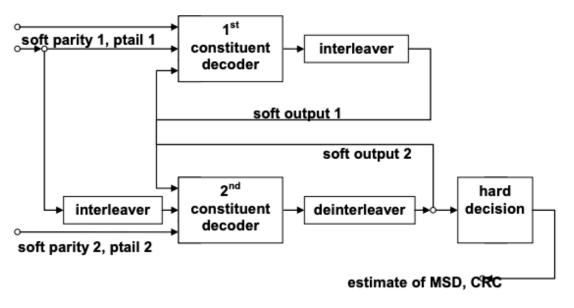

15. For example, each of the Accused Instrumentalities performed iterative decoding using at least the BCJR algorithm.

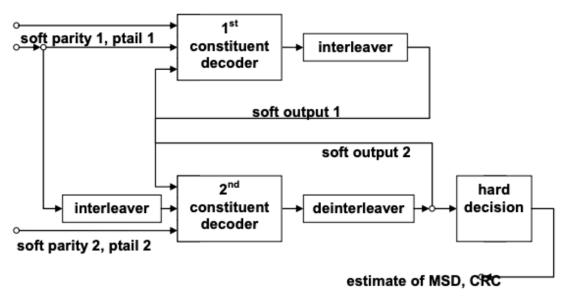

Figure 18: Turbo decoder

(See 3GPP TS 26.268 at 21 (v. 11), 17 (v. 8).).

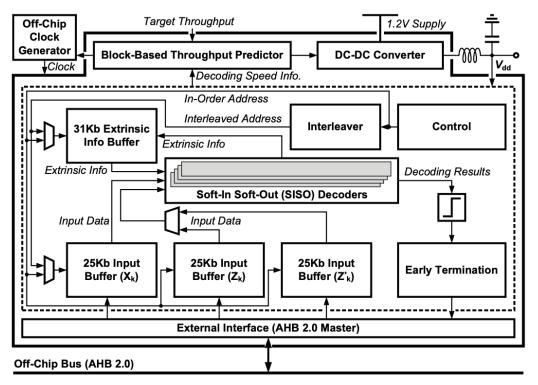

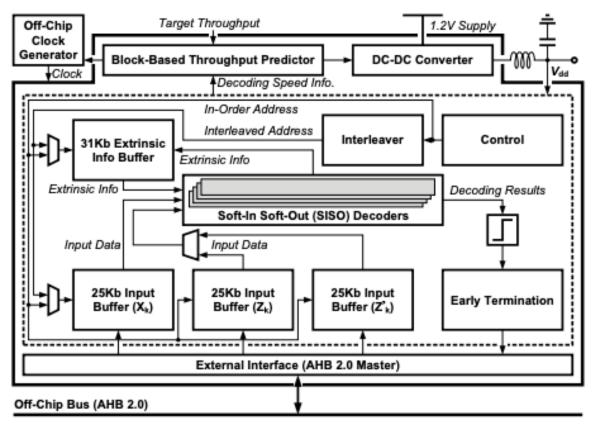

See Mansour et al., "VLSI Architectures for SISO-APP Decoders," IEEE Transactions On Very Large Scale Integration ("VLSI") Systems, Vol. 11, No. 4 (Aug. 2003), at 627, *available at* <u>http://shanbhag.ece.illinois.edu/publications/mansr-tvlsi-2003-2.pdf</u>: "The BCJR algorithm was generalized in [S. Benedetto *et al.*, "A Soft-Input Soft-Output Maximum a posteriori (Map) Module to Decode Parallel and Serial Concatenated Codes," JPL, TDA Progress Report 42-127, Nov. 1996] into a soft-input soft-output a posteriori probability (SISO- APP) algorithm to be used as a building block for iterative decoding in code networks with generic topologies...." *See also Cheng et. al.* "A 0.077 to 0.168 nj/bit/iteration Scalable 3GPP LTE Turbo Decoder with an Adaptive Sub-Block Parallel Scheme and an Embedded DVFS Engine," 2010 IEEE Custom

Integrated Circuits Conference (CICC) (19-22 Sept. 2010), at 3, *available at* https://dspace.mit.edu/bitstream/handle/1721.1/72198/Chandrakasan-

<u>a%200.077%20to%200.168.pdf?sequence=1&isAllowed=y</u> (citation omitted): "Figure 3 shows the system architecture. The blocks in the dashed box handle the turbo decoding operations, and those outside the dashed box belong to the DVFS scheme. Turbo decoding is an iterative process with several turbo iterations. Each turbo iteration comprises two soft-in, soft-out (SISO) decoding processes using BCJR algorithm with the first one performed on the input code block in the original order and the second one in an order generated by the interleaver block." *See also* "Digital cellular telecommunications system (Phase 2+); Universal Mobile Telecommunications System (UMTS); eCall data transfer; In-band modem solution; ANSI-C reference code (3GPP TS 26.268 version

11.0.0 Release 11)," at 14, *available at* https://www.etsi.org/deliver/etsi\_ts/126200\_126299/126268/11.00.00\_60/ts\_126268v110000p.p df ("3GPP TS 26.268 v. 11"); "Digital cellular telecommunications system (Phase 2+); Universal Mobile Telecommunications System (UMTS); eCall data transfer; In-band modem solution; ANSI-C reference code (3GPP TS 26.268 version 8.0.0 Release 8)," at 17, *available at* https://www.etsi.org/deliver/etsi\_ts/126200\_126299/126268/08.00.00\_60/ts\_126268v080000p.p df ("3GPP TS 26.268 v. 8"):

| Type/Constant            | Dimension | Description               |

|--------------------------|-----------|---------------------------|

| /* Synchronization */    |           |                           |

| const Int16 wakeupSin500 | [16]      | sine waveform at 500 Hz   |

| const Int16 wakeupCos500 | [16]      | cosine waveform at 500 Hz |

| const Int16 wakeupSin800 | [10]      | sine waveform at 800 Hz   |

| const Int16 wakeupCos800 | [10]      | cosine waveform at 800 Hz |

See also id. at 20 (v. 11), 16-17 (v. 8) and source code release accompanying 3GPP TS 26.268,

ecall\_fec.c, lines 232-268:

```

/*-----*/

/* PSAP FUNCTION: PsapReceiver

/*------

*/

__*/

*/

/* Description: PSAP receiver function (decoding is done outside)

/*

/* In: const ModState* ms -> modulator struct

/* const Int16* pcm -> input data for demodulation

/* Out: IntLLR* softBits <- demodulated soft bit sequence</pre>

/*

*/

*/

*/

*/

/*-----*/

void PsapReceiver(const ModState *ms, const Int16 *pcm, IntLLR *softBits)

/*_____

/* PSAP FUNCTION: SymbolDemod

*/

/*----*/

/* Description: symbol demodulator

*/

/*

*/

/* In: const ModState* ms -> modulator struct

/* const Int16* mPulse -> received pulse train

*/

*/

/* Out: IntLLR* softBits <- demodulated soft bit sequence */

/*-----*/

void SymbolDemod(const ModState *ms, const Int16 *mPulse, IntLLR *softBits)

```

(E.g., ecall\_fec.c line 163 Bool FecDecode(const IntLLR \*in, Int16 rv, Ord1 \*out)).

```

/*_____*

/* DECODER FUNCTION: FecDecode

*/

/*-----

_ _ * /

/* Description: decoding to find the MSD

*/

/*

*/

/* In: const IntLLR* in -> received soft bits

/* Int16 rv -> redundancy version

/* Out: Ord1* out <- decoded MSD in binary representation

/* Return: Bool <- result of CRC check

/*</pre>

*/

*/

*/

*/

/*-----*/

Bool FecDecode (const IntLLR *in, Int16 rv, Ord1 *out)

```

(E.g., ecall\_fec.c line 240 /\*iterative decoding \*/ for (i = 0;  $i < FEC_ITERATIONS$ ; i++)).<sup>1</sup>

*See also* May et al., "A 150Mbit/s 3GPP LTE Turbo code decoder," 2010 Design, Automation & Test in Europe Conference & Exhibition (March 8-12, 2010), *available at* <u>https://ieeexplore.ieee.org/document/5457035/authors#authors</u>: "3GPP long term evolution (LTE) enhances the wireless communication standards UMTS and HSDPA towards higher throughput.

<sup>&</sup>lt;sup>1</sup> All citations to source code refer to the source code release accompanying 3GPP TS 26.268, available at <u>https://portal.3gpp.org/desktopmodules/Specifications/SpecificationDetails.aspx?</u> <u>specificationId=1446</u>." Specific line citations for this and other source code are to the version accompanying Release 11, but substantially identical code is present in the version accompanying Release 8, available from the same hyperlink.

A throughput of 150 Mbit/s is specified for LTE using 2×2 MIMO. For this, highly punctured Turbo codes with rates up to 0.95 are used for channel coding, which is a big challenge for decoder design. This paper investigates efficient decoder architectures for highly punctured LTE Turbo codes. We present a 150 Mbit/s 3GPP LTE Turbo code decoder, which is part of an industrial SDR multi-standard baseband processor chip."

16. Additionally, or alternatively, the relevant standards bodies, such as 3GPP, provided specifications that specify virtually all aspects of turbo encoders (*i.e.*, turbo-code transmitters), turbo decoders (*i.e.*, turbo-code receivers) and specify minimum performance requirements for the receivers and decoders (as well as encoders and transmitters) so that arbitrary transmitter-receiver pairs can communicate seamlessly. *See, e.g.*, ROHDE & SCHWARZ, "Radio fundamentals for cellular networks White paper," 19 (Jan. 2019), *available at* https://www.elektronikfokus.dk/wp-content/uploads/sites/5/WhitePaper\_Radio-fundamentals-for-cellular-networks\_wp\_en\_5216-0467-52\_v0201.pdf.

17. On information and belief, each of the Accused Instrumentalities processed received baseband digital signals in an iterative manner. It was not commercially-feasible to implement turbo decoders in a non-iterative manner. No known commercial turbo decoder implementation used a pipeline of a SISO pair (with interleave/deinterleave operations) as replicated hardware blocks to fully replace iterations, and it is universally known in industry and academia that decoding of 3G/4G LTE turbo codes was explicitly and inherently iterative by both requirement and design. See, e.g., Dejan Spasov, "Decoding of LTE Turbo Codes Initialized with the Two Recursive Convolutional Codes," 2020 43rd International Convention on Information, Communication and Electronic Technology (MIPRO) (2020),available at https://ieeexplore.ieee.org/document/9245282 ("Turbo codes were the first error-correcting codes

#### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 21 of 54 PageID #: 21

that demonstrated reliable communications near the channel capacity with practically feasible hardware. Due to their excellent error-correcting capability, they are part of many modern communication technologies, like 3G, 4G, LTE, etc. .... The decoding of LTE Turbo codes is iterative."); Altera Corporation, "3GPP LTE Turbo Reference Design" (Jan. 2020), *available at* https://www.intel.com/content/dam/www/programmable

/us/en/pdfs/literature/an/an505.pdf ("A Turbo decoder consists of two single soft-in soft-out (SISO) decoders, which work iteratively."); Shuai Shao *et al.*, "Survey of Turbo, LDPC and Polar Decoder ASIC Implementations," IEEE Communications Surveys & Tutorials, 1 (Jan. 17, 2019), *available at https://eprints.soton.ac.uk/427712/1/Survey of Turbo LDPC and Polar Decoder\_ASIC\_Implementations.pdf* ("Both the turbo and LDPC codes employ an iterative decoding process, in which each successive attempt at decoding the information block informs the next, until the process converges to a legitimate codeword.").

18. In iterative turbo decoder implementations, each iteration provides a decoding pass step. At each moment, a given error environment has an associated optimal number of decoding pass steps to produce the best results. Thus, a permanently-fixed number of decoding pass steps incurs either wasted computation or degraded performance. (*See, e.g.*, A. Matache et al., "Stopping Rules for Turbo Decoders," TMO Progress Report 42-142 (Aug. 15, 2000), *available at* https://ipnpr.jpl.nasa.gov/progress\_report/42-142/142J.pdf). Because the number of decoding pass steps can be arbitrary and dynamically varied, stopping rules (dependent on real-time computational measurements) are used to determine the number of decoding pass steps.

19. Were a non-iterative (pipeline) implementation employed, a fixed or maximum number of decoding pass steps would have to be implemented, with each decoding pass step requiring extensive hardware, and in practice yielding at almost every instant either too few stages

21

#### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 22 of 54 PageID #: 22

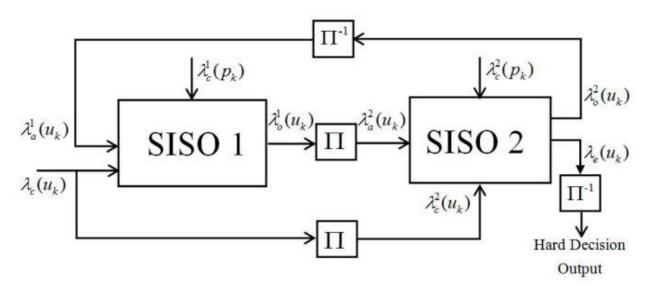

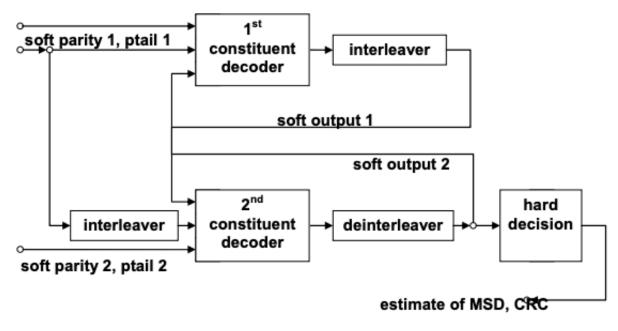

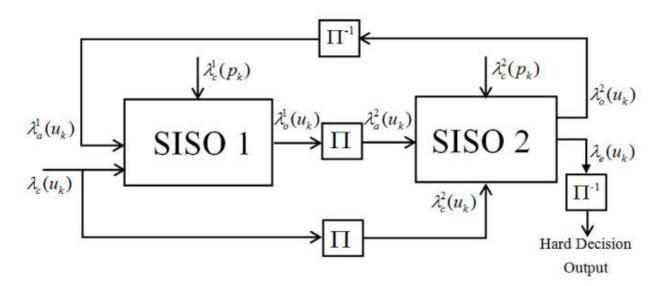

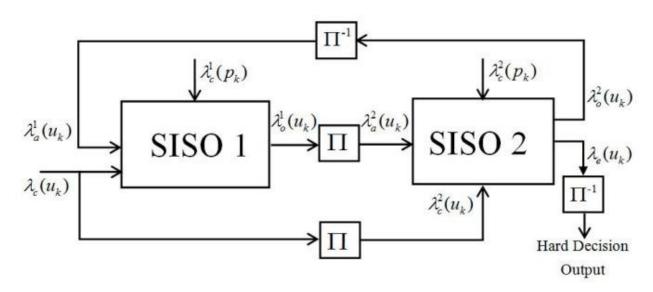

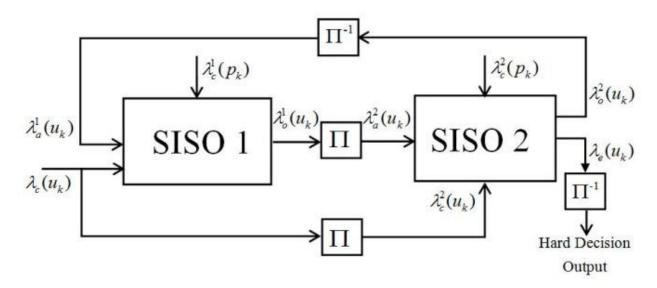

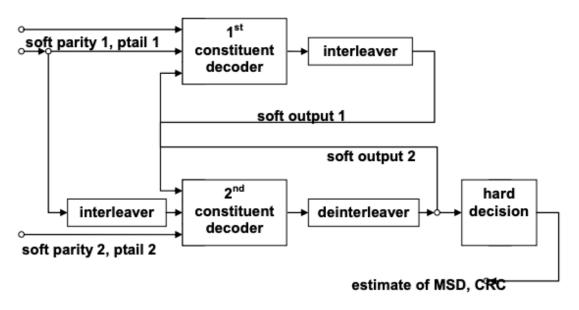

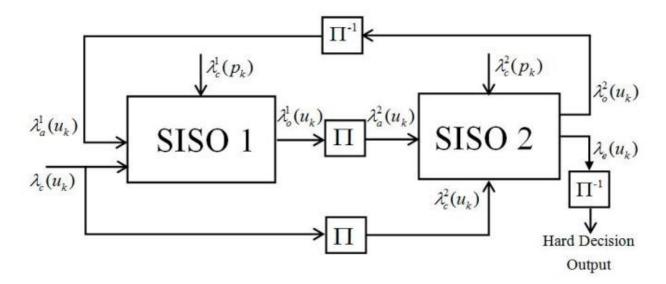

or too many stages. Thus, non-iterative implementations suffered disadvantages of higher costs, high power consumption, and lower average performance. In practice any commercial 4G LTE turbo decoder is necessarily recursive/iterative. While lower-level pipelines were employed in many hardware implementations of MAP computations *within* SISO elements, this is different in scope and method than a (non-iterative) pipeline of *full-scale SISO pair blocks* (with interleave/deinterleave operations) of replicated hardware to replace (SISO pair) iterations. All iterative implementations of 4G LTE turbo decoders were functionally equivalent to the figures below. The top of the figures below illustrates the feedback loop that forced 3G/4G LTE turbo decoders to be iterative. The iterative loop traversed elements SISO 1,  $\Pi$ , SISO 2,  $\Pi$ <sup>-1</sup>, and closed with the signal path return to the input of SISO 1.

(*E.g.*, *see* Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) (Aug. 20, 2019), *available at* <u>https://www.ncbi.nlm.nih.gov/pmc/articles/PMC7515343/</u>).

20. Upon information and belief, the Accused Instrumentalities provided an input buffer comprising at least three shift registers, for receiving an input signal and generating first, second, and third shifted input signals. The Accused Instrumentalities provided (e.g., via an input

buffer) input to the constituent decoders of the turbo decoder. The input buffer comprised at least three shift registers. The input buffer received an input signal, and first, second, and third shifted input signals were generated for input to a turbo decoder. The generated first, second, and third shifted input signals, shown as "soft data," "soft parity 1, ptail 1," and "soft parity 2, ptail 2," were input into the 1st constituent decoder and 2nd constituent decoder as shown below:

Figure 18: Turbo decoder

(*E.g.*, 3GPP TS 26.267, at 14 (v. 11, v. 8)).

21. Upon information and belief, the Accused Instrumentalities, each such buffer provided three sections based on operations of a turbo encoder. For example, an input buffer is denoted as Figure 7, labeled as a "channel coded bit buffer."

## Figure 7: Channel coded bit buffer

(See 3GPP TS 26.267, at 14 (v. 11, v. 8)). Note that the "soft data" of Figure 18 corresponds to the "MSD+CRC," "tail 1," and "tail 2" fields of Figure 7. Such a channel coded bit buffer could then be decoded using shifting to generate the first, second, and third shifted input signals, which were stored in registers for input into the turbo decoder: "6.1.3 Modulation: The encoded binary data stream bits  $b_i$  are grouped into symbols. Each symbol  $d_i$  carries 4 bits of information and modulates one basic downlink waveform... Table 4 describes the symbol modulation mapping between symbol and the downlink waveform. The downlink waveform is derived from the basic downlink waveform  $p_{DL}(n)$  by a cyclic right-shift by k samples, denoted by  $(p \rightarrow k)$ , and multiplication with a sign *q*." (See 3GPP TS 26.267, at 22 (v. 11), 21 (v. 8)). See also Cheng et. al. "A 0.077 to 0.168 nj/bit/iteration Scalable 3GPP LTE Turbo Decoder with an Adaptive Sub-Block Parallel Scheme and an Embedded DVFS Engine," 2010 IEEE Custom Integrated Circuits Conference available (CICC) (19-22) Sept. 2010), Fig. 3, at at https://dspace.mit.edu/bitstream/handle/1721.1/72198/Chandrakasan-<u>a%200.077%20to%200.168.pdf?sequence=1&isAllowed=y:</u>

Fig. 3. The system architecture.

See also 3GPP TS 26.268 at 21 (v. 11), 17 (v. 8) and source code release accompanying 3GPP TS 26.268 ecall\_fec.c line 200 void UpdateBuffer(IntLLR \*chLLRbuffer, const IntLLR \*softInBits, Int16 rv) ecall\_fec.c line 225 void DecodeBuffer(const IntLLR \*syst1, const IntLLR \*syst2, const IntLLR \*parity1, const IntLLR \*parity2, Ord1 \*decBits)).

22. Additionally, and alternatively, as discussed above, each of the Accused Instrumentalities processed received baseband digital signals in an iterative manner through its implementation of turbo decoding. Any turbo decoder implementation receiving and operating on an incoming input signal included an input buffer structure and three component shift registers to provide time-aligned values (*i.e.*, first, second, and third shifted input signals) needed for each SISO computation. To the extent that any of the Accused Instrumentalities did not implement shift register functions in hardware, it was a well-established convention to implement shift register functions via software. *See, e.g.*, Wikipedia, "Shift register," *available at*

#### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 26 of 54 PageID #: 26

23. Upon information and belief, the Accused Instrumentalities provided first and second soft decision decoders serially coupled in a circular circuit, wherein each decoder processed soft decision from the preceding decoder output data, and wherein the first decoder further received the first and second shifted input signals from the input buffer and the second decoder further received the third shifted input signal from the input buffer.

Figure 18: Turbo decoder

(*E.g.*, 3GPP TS 26.267, at 14 (v. 11, v. 8)).

24. In the example, the first soft decision decoder output soft decision that became "soft output 1" after exiting "interleaver." This "soft output 1" was fed as input into the second soft

#### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 27 of 54 PageID #: 27

decision decoder, "2nd constituent decoder," for the second decision decoder to process. The second soft decision decoder also received the "soft parity 2, ptail 2" input signal. The second soft decision decoder output soft decision that became "soft output 2" after exiting "deinterleaver." This "soft output 2" was fed as input into the first soft decision decoder for the first soft decision decoder to process. The first soft decision decoder, "1st constituent decoder," also received the "soft data" and "soft parity 1, ptail 1" input signals. *See also Cheng et. al.* "A 0.077 to 0.168 nj/bit/iteration Scalable 3GPP LTE Turbo Decoder with an Adaptive Sub-Block Parallel Scheme and an Embedded DVFS Engine," 2010 IEEE Custom Integrated Circuits Conference (CICC) (19-22 Sept. 2010), at 3, *available at*

https://dspace.mit.edu/bitstream/handle/1721.1/72198/Chandrakasan-

a%200.077%20to%200.168.pdf?sequence=1&isAllowed=y (citation removed): "Figure 3 shows the system architecture. The blocks in the dashed box handle the turbo decoding operations, and those outside the dashed box belong to the DVFS scheme. Turbo decoding is an iterative process with several turbo iterations. Each turbo iteration comprises two soft-in, soft-out (SISO) decoding processes using BCJR algorithm with the first one performed on the input code block in the original order and the second one in an order generated by the interleaver block." See also Valenti et al., "UMTS Turbo Code and an Efficient Decoder," International Journal of Wireless Information Vol. 8, Networks, No. 4 (Oct. 2001), 206, available at at https://community.wvu.edu/~mcvalenti/documents/valenti01.pdf at Page 206, section 5. THE MAX\* OPERATOR, 5.1. Log-MAP Algorithm, 5.2. Max-log-MAP Algorithm.

| /*<br>/* DECODER FUNCTION: Bcjr                          | =*/<br>*/ |

|----------------------------------------------------------|-----------|

| /*                                                       | -*/       |

| /* Description: BCJR algorithm                           | */        |

| /*                                                       | */        |

| /* In: const IntLLR* parity -> received parity soft bits | */        |

| /* InOut: IntLLR* extrinsic <-> extrinsic information    | */        |

| /*                                                       | -*/       |

| void Bcjr(const IntLLR *parity, IntLLR *extrinsic)       |           |

#### (*E.g.*, 3GPP TS 26.268 at 21 (v. 11), 17 (v. 8)).

25. Additionally, or alternatively, as explained above, all known commercial implementations of 4G LTE turbo decoders were iterative and functionally equivalent to the figures below. The figures below illustrate soft decision from the preceding decoder output (a posteriori information) being fed as an input (a priori information) in an iterative mode. The top of the figures below illustrates the feedback loop that forced 3G/4G LTE turbo decoders to be iterative. The iterative loop traversed elements SISO 1,  $\Pi$ , SISO 2,  $\Pi$ <sup>-1</sup>, and closed with the signal path return to the input of SISO 1 to form a circular circuit.

*See* Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) (Aug. 20, 2019), *available at* <u>https://www.ncbi.nlm.nih.gov/pmc/articles/</u> <u>PMC7515343/</u> ("The SISO decoder consists of three input ports, which are system

information  $\lambda_c(u_k)$ , parity information  $\lambda_c(p_k)$ , and a priori information  $\lambda_a(u_k)$  which is computed by another SISO decoder. Two output ports of the SISO decoder generate external information  $\lambda_e(u_k)$  and posteriori information  $\lambda_o(u_k)$ . The different superscripts represent information corresponding to different SISO decoders, and subscript *k* denotes *k*-th bit information of the current variable.").

26. As explained above, each of the Accused Instrumentalities processed received baseband digital signals in an iterative manner through its implementation of turbo decoding. Any turbo decoder implementation receiving and operating on an incoming input signal included an input buffer structure and three component shift registers to provide time-aligned values (*i.e.*, first, second, and third shifted input signals) needed for each SISO computation. To the extent that any of the Accused Instrumentalities did not implement shift register functions in hardware, it was a well-established convention to implement shift register functions via software. *See, e.g.*, Wikipedia, "Shift register," *available at* https://en.wikipedia.org/wiki/Shift\_register ("Many computer languages include instructions to 'shift right' and 'shift left' the data in a register, effectively dividing by two or multiplying by two for each place shifted."); GeeksforGeeks, "Left Shift and Right Shift Operators in C/C++," *available at* https://www.geeksforgeeks.org/left-shift-right-shift-operators-c-cpp/; mbedded.ninja, "Shift Registers," §5 (Apr. 8, 2020), *available at* https://blog.mbedded.ninja/electronics/components/shift-registers/.

27. Upon information and belief, the Accused Instrumentalities provided at least one memory module coupled to an output of each of the first and second soft decision decoders, wherein the output of the memory module associated with the second soft decision decoder was fed back as an input of the first soft decision decoder. For example, the Accused Instrumentalities included at least one memory module (*e.g.*, "interleaver" to the right of the "1st constituent

29

decoder" and "deinterleaver" in the figures below), that was electrically coupled to an output of a corresponding soft decision decoder (*e.g.*, "1st constituent decoder" and "2nd constituent decoder")), wherein the output of the memory module associated with the second soft decision decoder ("deinterleaver") was fed back as an input of the first soft decision decoder, as shown below:

## (*E.g.*, 3GPP TS 26.267, at 25 (v. 11), 24 (v. 8)).

28. In the example, the "deinterleaver" memory module was associated with the second soft decision decoder, "2nd constituent decoder." The output of the deinterleaver, "soft output 2," was fed back as an input of the first soft decision decoder, "1st constituent decoder." Additional evidence that the "interleaver" and "deinterleaver" comprised memory modules is shown in source code associated with the figure:

```

/* initialize memory */

Le12 = (IntLLR*)&decBits[0];

Le21 = (IntLLR*)&decBits[sizeof(IntLLR)*(NRB_INFO_CRC + NRB_TAIL)];

```

```

memset(Le12, 0, sizeof(IntLLR)*(NRB_INFO_CRC + NRB_TAIL));

memset(Le21, 0, sizeof(IntLLR)*(NRB_INFO_CRC + NRB_TAIL));

```

```

/* iterative decoding */

for (i = 0; i < FEC_ITERATIONS; i++) {

memcpy(Le12, Le21, sizeof(IntLLR)*(NRB_INFO_CRC + NRB_TAIL));</pre>

```

```

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB_INFO_CRC+NRB_TAIL; j++) {

temp = (Int32)Le12[j] + (Int32)syst1[j];

Le12[j] = (ABS(temp) < LLR_MAX) ?

(IntLLR)temp : (IntLLR)(SIGN(temp)*LLR_MAX);

}

/* decode code one (produces Le12) */

Bcjr(parity1, Le12);</pre>

```

```

/* interleave extrinsic information (produces interleaved Le12) */

Interleave(Le12, Le21);

```

```

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB_INFO_CRC; j++) {

temp = (Int32)Le21[j] + (Int32)syst1[interleaverSeq[j]];

Le21[j] = (ABS(temp) < LLR_MAX) ?

(IntLLR)temp : (IntLLR)((SIGN(temp))*LLR_MAX);

}

for (j = 0; j < NRB_TAIL; j++) {

Le21[j+NRB_INFO_CRC] = syst2[j];

}

}</pre>

```

```

/* decode code two (produces interleaved Le21) */

Bcjr(parity2, Le21);

```

```

/* deinterleave extrinsic information (produces Le21) */

Deinterleave(Le21);

}

```

(*E.g.*, source code release accompanying 3GPP TS 26.268, ecall\_fec.c, lines 232-268). *See also* Mansour et al., "VLSI Architectures for SISO-APP Decoders," IEEE Transactions On Very Large Scale Integration ("VLSI") Systems, Vol. 11, No. 4 (Aug. 2003) "Fig. 1. A (2, 1, 3) convolutional code. (a) An encoder with 2 memory delay elements (D) and modulo 2 adders, data symbol alphabet {0, 1}, code symbol alphabet {0, 1, 2, 3}, memory states {0, 1, 2, 3}, and code rate R = (1=2). (b) A trellis section where solid edges correspond to u = 0, and dashed edges correspond to u = 1. The output code symbols c are shown on the edges. The edges are numbered with black squares, and the edge starting and ending states are shown on the left and right, respectively." *See also id.* at FIG. 1:

*See also* Valenti et al., "UMTS Turbo Code and an Efficient Decoder," International Journal of Wireless Information Networks, Vol. 8, No. 4 (Oct. 2001), at 207, *available at* <u>https://community.wvu.edu/~mcvalenti/documents/valenti01.pdf</u>: "Two key observations should be pointed out before going into the details of the algorithm: (1) It does not matter whether the

forward sweep or the reverse sweep is performed first; and (2) while the partial path metrics for the entire first sweep (forward or backward) must be stored in memory, they do not need to be stored for the entire second sweep. This is because the LLR values can be computed during the second sweep, and thus partial path metrics for only two stages of the trellis (the current and previous stages) must be maintained during the second sweep." *See also Cheng et. al.* "A 0.077 to 0.168 nj/bit/iteration Scalable 3GPP LTE Turbo Decoder with an Adaptive Sub-Block Parallel Scheme and an Embedded DVFS Engine," 2010 IEEE Custom Integrated Circuits Conference (CICC) (19-22 Sept. 2010), at Fig. 3, *available at* <a href="https://dspace.mit.edu/bitstream/handle/1721.1/72198/Chandrakasan-a%200.077%20to%200.168.pdf?sequence=1&isAllowed=y:">https://dspace.mit.edu/bitstream/handle/1721.1/72198/Chandrakasan-a%200.077%20to%200.168.pdf?sequence=1&isAllowed=y:</a>

Fig. 3. The system architecture.

See also, source code release accompanying 3GPP TS 26.268, ecall\_fec.c, lines 232-268:

```

ecall_fec.c line 232

/* initialize memory */

Le12 = (IntLLR*)&decBits[0];

Le21 = (IntLLR*)&decBits[sizeof(IntLLR)*(NRB_INFO_CRC + NRB_TAIL)];

memset(Le12, 0, sizeof(IntLLR)*(NRB_INFO_CRC + NRB_TAIL));

memset(Le21, 0, sizeof(IntLLR)*(NRB_INFO_CRC + NRB_TAIL));

ecall_fec.c line 250

Bcjr(parity1, Le12); /*corresponding memory module Le12*/

ecall_fec.c line 265

Bcjr(parity2, Le21); /*corresponding memory module Le21*/

```

29. Additionally, or alternatively, as explained above, all known commercial implementations of 4G LTE turbo decoders were iterative and functionally equivalent to the figures below. The figures below illustrate output of the memory module associated with a last soft decision decoder fed back as an input to the first soft decision decoder via interleaving and/or de-interleaving (*e.g.*, the a posteriori output of SISO 2 was de-interleaved with the associated memory module and fed back as a priori input of SISO 1).

*See* Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) (Aug. 20, 2019), *available at* <u>https://www.ncbi.nlm.nih.gov/pmc/articles/</u> <u>PMC7515343/</u>) ("Π and Π–1 denote interleaving and de-interleaving, respectively.").

30. Upon information and belief, the Accused Instrumentalities processed systematic information data and extrinsic information data using the maximum a posteriori (MAP) probability algorithm, and/or logarithm approximation algorithm. For example, the Accused Instrumentalities used at least the BCJR algorithm for turbo decoding in accordance with the figures below:

Figure 18: Turbo decoder

(*E.g.*, 3GPP TS 26.267, at 25 (v. 11), 24 (v. 8)).

31. The source code associated with the figure indicates that it processes systematic

information data and extrinsic information data using the BCJR algorithm:

```

/* initialize memorv */

Le12 = (IntLLR^*) \& decBits[0];

Le21 = (IntLLR*)&decBits[sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL)];

memset(Le12, 0, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

memset(Le21, 0, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

/* iterative decoding */

for (i = 0; i < FEC \ ITERATIONS; i++)

memcpy(Le12, Le21, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB INFO CRC+NRB TAIL; j++)

temp = (Int32)Le12[j] + (Int32)syst1[j];

Lel2[i] = (ABS (temp) < LLR MAX)?

(IntLLR)temp : (IntLLR)(SIGN(temp)*LLR MAX);

}

/* decode code one (produces Le12) */

Bcjr(parity1, Le12):

```

```

/* interleave extrinsic information (produces interleaved Le12) */

Interleave(Le12, Le21);

```

```

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB_INFO_CRC; j++) {

temp = (Int32)Le21[j] + (Int32)syst1[interleaverSeq[j]];

Le21[j] = (ABS(temp) < LLR MAX) ?

(IntLLR)temp : (IntLLR)((SIGN(temp))*LLR_MAX);

}

for (j = 0; j < NRB TAIL; j++) {

Le21[j+NRB_INFO_CRC] = syst2[j];

}</pre>

```

```

/* decode code two (produces interleaved Le21) */

Bcjr(parity2, Le21);

```

```

/* deinterleave extrinsic information (produces Le21) */

Deinterleave(Le21);

}

```

(*E.g.*, *see*, source code release accompanying 3GPP TS 26.268, ecall\_fec.c, lines 232-268).

32. The BCJR algorithm is a MAP probability algorithm that processes systematic information data and extrinsic information data: "Turbo codes are composed of an interconnection of component codes through interleavers, typically convolutional codes, and their decoders consist of an equal number of component decoders each of which operates on its corresponding codeword and shares information with other component decoders iteratively according to the topology of the encoder. The decoding algorithm in the component decoders is the maximum a-posteriori probability (MAP) algorithm typically implemented in the form known as the Bahl-Cocke-Jelinek-Raviv (BCJR) algorithm. The main advantage of a MAP decoding algorithm over a maximum likelihood decoding algorithm such as the Viterbi algorithm is that it produces optimum soft information which is crucial to the operation of these decoders. The BCJR algorithm was generalized in [S. Benedetto et al., "A Soft-Input Soft-Output Maximum a posteriori (Map) Module to Decode Parallel and Serial Concatenated Codes," JPL, TDA Progress Report 42-127, Nov. 1996.] into a soft-input soft-output a posteriori probability (SISO-APP) algorithm to be used as a building block for iterative decoding in code networks with generic topologies. The advantages of the SISO-APP algorithm over other forms of the MAP algorithm is that it is independent of the code type (systematic/nonsystematic, recursive/nonrecursive, trellis with multiple edges), and it generates reliability information for code symbols as well as message symbols which makes it applicable irrespective of the concatenation scheme (parallel/serial/hybrid), and hence will be considered in this paper." See Mansour et al., "VLSI Architectures for SISO-APP Decoders," IEEE Transactions On Very Large Scale Integration ("VLSI") Systems, Vol. 11, No. 4 2003), 627, available (Aug. at at http://shanbhag.ece.illinois.edu/publications/mansr-tvlsi-2003-2.pdf (citations removed). See also *id.* at 629 ("The decoding problem can now be defined as follows: given a noisy version of  $\underline{c}$  denoted by  $\underline{y}=\Delta(y_1, \dots, y_k, \dots, y_L)$ , find the data sequence  $\underline{u}$ . There are two probabilistic solutions to this decoding problem. Maximum likelihood (ML) decoding determines the most likely connected path  $\underline{s}$  through the trellis that maximizes the probability  $P(\underline{y}|\underline{s})$ . From  $\underline{s}$ , the most likely data sequence  $\underline{u}$  is easily determined using (1). On the other hand, MAP decoding, which we consider here, determines  $\underline{u}$  by estimating each of the symbols  $u_k$  independently using the observations  $\underline{y}$ . The kth estimated symbol  $u_k$  is the one that maximizes the posterior probability  $P(u_k|\underline{y})$ , and hence the name symbol-by-symbol MAP. The SISO-APP algorithm, a generalized version of the BCJR-APP algorithm, is a probabilistic algorithm that solves the MAP decoding problem.") (citations removed).

33. Additionally, or alternatively, as explained above, all known commercial implementations of 4G LTE turbo decoders were iterative and functionally equivalent to the figures below. The figures below illustrate that each decoder processed systemic information data and extrinsic information data—system information  $\lambda_c(u_k)$ , parity information  $\lambda_c(p_k)$ , a priori information  $\lambda_a(u_k)$  and external information  $\lambda_e(u_k)$ :

See Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) (Aug. 20, 2019), available at <a href="https://www.ncbi.nlm.nih.gov/pmc/articles/">https://www.ncbi.nlm.nih.gov/pmc/articles/</a> PMC7515343/. See also, e.g., Guohui Wang et al., "High-throughput Contention-Free Concurrent Interleaver Architecture for Multi-standard Turbo Decoder," ASAP 2011—22nd IEEE International Conference on Application-specific Systems, Architectures and Processors 113 (Sept. 2011); Cristian Anghel et al., "CTC Turbo Decoding Architecture for LTE Systems Implemented on FPGA," ICN 2012: The Eleventh International Conference on Networks 199, 199-200 (2012).

34. Each soft decision decoder on all known commercial implementations of any turbo decoder processed systematic information data and extrinsic information data using a maximum a posteriori (MAP) probability algorithm and/or a logarithm approximation algorithm to yield posteriori information  $\lambda_0(u_k)$ . *See* Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) (Aug. 20, 2019), *available at* <u>https://www.ncbi.nlm.nih.gov/pmc/articles/PMC7515343/</u> (discussing use of a log maximum a posteriori decoding algorithm). *See also, e.g.*, Guohui Wang *et al.*, "High-throughput Contention-Free Concurrent Interleaver Architecture for Multi-standard Turbo Decoder," ASAP 2011—22nd IEEE International Conference on Application-specific Systems, Architectures and Processors 113 (Sept. 2011) (noting that MAP decoders are used as the component SISO decoders); Cristian Anghel et al., "CTC Turbo Decoding Architecture for LTE Systems Implemented on FPGA," ICN 2012: The Eleventh International Conference on Networks 199, 200 (2012) (describing ideal use of classic MAP algorithm and practical implementation of log-MAP algorithms).

35. Upon information and belief, the Accused Instrumentalities generated soft decision based on the maximum a posteriori (MAP) probability algorithm and/or logarithm approximation

39

algorithm. For example, the Accused Instrumentalities used at least the BCJR algorithm for decoding in accordance with the figures below:

Figure 18: Turbo decoder

(*E.g.*, 3GPP TS 26.267, at 25 (v. 11), 24 (v. 8)). The source code associated with the figure, for example, indicates that it generated soft decision based on the BCJR algorithm. Data processed by the BCJR algorithm was interleaved or deinterleaved, resulting in "soft output 1" or "soft output 2," respectively, as shown in the figure:

```

/* initialize memorv */

Le12 = (IntLLR^*) \& decBits[0];

Le21 = (IntLLR*)&decBits[sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL)];

memset(Le12, 0, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

memset(Le21, 0, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

/* iterative decoding */

for (i = 0; i < FEC \ ITERATIONS; i++)

memcpy(Le12, Le21, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB INFO CRC+NRB TAIL; j++)

temp = (Int32)Le12[j] + (Int32)syst1[j];

Lel2[i] = (ABS (temp) < LLR MAX)?

(IntLLR)temp : (IntLLR)(SIGN(temp)*LLR MAX);

}

/* decode code one (produces Le12) */

Bcjr(parity1, Le12):

```

```

/* interleave extrinsic information (produces interleaved Le12) */

Interleave(Le12, Le21);

```

```

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB_INFO_CRC; j++) {

temp = (Int32)Le21[j] + (Int32)syst1[interleaverSeq[j]];

Le21[j] = (ABS(temp) < LLR MAX) ?

(IntLLR)temp : (IntLLR)((SIGN(temp)))*LLR_MAX);

}

for (j = 0; j < NRB TAIL; j++) {

Le21[j+NRB_INFO_CRC] = syst2[j];

}</pre>

```

```

/* decode code two (produces interleaved Le21) */

Bcjr(parity2, Le21);

```

```

/* deinterleave extrinsic information (produces Le21) */

Deinterleave(Le21);

}

```

(E.g., see, source code release accompanying 3GPP TS 26.268, ecall\_fec.c, lines 232-268). The BCJR algorithm included a MAP probability algorithm which processed soft input to generate soft decision: "Turbo codes are composed of an interconnection of component codes through interleavers, typically convolutional codes, and their decoders consist of an equal number of component decoders each of which operates on its corresponding codeword and shares information with other component decoders iteratively according to the topology of the encoder. The decoding algorithm in the component decoders is the maximum a-posteriori probability (MAP) algorithm typically implemented in the form known as the Bahl–Cocke–Jelinek–Raviv (BCJR) algorithm. The main advantage of a MAP decoding algorithm over a maximum likelihood decoding algorithm such as the Viterbi algorithm is that it produces optimum soft information which is crucial to the operation of these decoders. The BCJR algorithm was generalized in [S. Benedetto et al., "A Soft-Input Soft-Output Maximum a posteriori (Map) Module to Decode Parallel and Serial Concatenated Codes," JPL, TDA Progress Report 42-127, Nov. 1996.] into a soft-input soft-output a posteriori probability (SISO-APP) algorithm to be used as a building block for iterative decoding in code networks with generic topologies. The advantages of the SISO-APP algorithm over other forms of the MAP algorithm is that it is independent of the code type (systematic/nonsystematic, recursive/nonrecursive, trellis with multiple edges), and it generates reliability information for code symbols as well as message symbols which makes it applicable irrespective of the concatenation scheme (parallel/serial/hybrid), and hence will be considered in this paper." See Mansour et al., "VLSI Architectures for SISO-APP Decoders," IEEE Transactions On Very Large Scale Integration ("VLSI") Systems, Vol. 11, No. 4 (Aug. 2003), at 627, available at http://shanbhag.ece.illinois.edu/publications/mansr-tvlsi-2003-2.pdf. See also id. at 629 ("The decoding problem can now be defined as follows: given a noisy version of  $\underline{c}$  denoted by

$\underline{y}=\Delta(y_1, \dots, y_k, \dots, y_L)$ , find the data sequence  $\underline{u}$ . There are two probabilistic solutions to this decoding problem. Maximum likelihood (ML) decoding determines the most likely connected path  $\underline{s}$  through the trellis that maximizes the probability  $P(\underline{y}|\underline{s})$ . From  $\underline{s}$ , the most likely data sequence  $\underline{u}$  is easily determined using (1). On the other hand, MAP decoding, which we consider here, determines  $\underline{u}$  by estimating each of the symbols  $u_k$  independently using the observations  $\underline{y}$ . The kth estimated symbol  $u_k$  is the one that maximizes the posterior probability  $P(u_k|\underline{y})$ , and hence the name symbol-by-symbol MAP. The SISO-APP algorithm, a generalized version of the BCJR-APP algorithm [6], is a probabilistic algorithm that solves the MAP decoding problem.").

36. Upon information and belief, the Accused Instrumentalities weighed and stored soft decision information into the corresponding memory module (*e.g.*, "interleaver" or "deinterleaver") as shown in the figures below:

Figure 18: Turbo decoder

(*E.g.*, 3GPP TS 26.267, at 25 (v. 11), 24 (v. 8)). The source code associated with the figure indicates use of the BCJR algorithm as shown below:

```

/* initialize memorv */

Le12 = (IntLLR^*) \& decBits[0];

Le21 = (IntLLR*)&decBits[sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL)];

memset(Le12, 0, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

memset(Le21, 0, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

/* iterative decoding */

for (i = 0; i < FEC \ ITERATIONS; i++)

memcpy(Le12, Le21, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB INFO CRC+NRB TAIL; j++)

temp = (Int32)Le12[j] + (Int32)syst1[j];

Lel2[i] = (ABS (temp) < LLR MAX)?

(IntLLR)temp : (IntLLR)(SIGN(temp)*LLR MAX);

}

/* decode code one (produces Le12) */

Bcjr(parity1, Le12):

```

```

/* interleave extrinsic information (produces interleaved Le12) */

Interleave(Le12, Le21);

```

```

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB_INFO_CRC; j++) {

temp = (Int32)Le21[j] + (Int32)syst1[interleaverSeq[j]];

Le21[j] = (ABS(temp) < LLR MAX) ?

(IntLLR)temp : (IntLLR)((SIGN(temp))*LLR_MAX);

}

for (j = 0; j < NRB TAIL; j++) {

Le21[j+NRB_INFO_CRC] = syst2[j];

}</pre>

```

```

/* decode code two (produces interleaved Le21) */

Bcjr(parity2, Le21);

```

```

/* deinterleave extrinsic information (produces Le21) */

Deinterleave(Le21);

}

```

(*E.g.*, *see*, source code release accompanying 3GPP TS 26.268, ecall\_fec.c, lines 232-268).

/\* normalization of betaQ \*/

for (i = 0; i < FEC\_STATES; i++) {

temp = (Int32)bTemp1[i] - (Int32)norm;

bTemp1[i] = (temp < (-LLR MAX)) ? (IntLLR)(-LLR MAX) : (IntLLR)temp;

}</pre>

/\* normalization of alphaQ \*/

for (i = 0; i < FEC STATES; i++) {

temp = (Int32)alpha2[i] - (Int32)norm;

alpha2[i] = (temp < (-LLR\_MAX)) ? (IntLLR)(-LLR\_MAX) : (IntLLR)temp;

}</pre>

(E.g., see, source code release accompanying 3GPP TS 26.268, ecall fec.c, lines 318-352). Data processed by the BCJR algorithm, for example, generates soft decision information. "Turbo codes are composed of an interconnection of component codes through interleavers, typically convolutional codes, and their decoders consist of an equal number of component decoders each of which operates on its corresponding codeword and shares information with other component decoders iteratively according to the topology of the encoder. The decoding algorithm in the component decoders is the maximum a-posteriori probability (MAP) algorithm typically implemented in the form known as the Bahl-Cocke-Jelinek-Raviv (BCJR) algorithm. The main advantage of a MAP decoding algorithm over a maximum likelihood decoding algorithm such as the Viterbi algorithm is that it produces optimum soft information which is crucial to the operation of these decoders. The BCJR algorithm was generalized in [S. Benedetto et al., "A Soft-Input Soft-Output Maximum a posteriori (Map) Module to Decode Parallel and Serial Concatenated Codes," JPL, TDA Progress Report 42-127, Nov. 1996.] into a soft-input soft-output a posteriori probability (SISO-APP) algorithm to be used as a building block for iterative decoding in code networks with generic topologies. The advantages of the SISO-APP algorithm over other forms of the MAP algorithm is that it is independent of the code type (systematic/nonsystematic, recursive/nonrecursive, trellis with multiple edges), and it generates reliability information for code symbols as well as message symbols which makes it applicable irrespective of the concatenation scheme (parallel/serial/hybrid), and hence will be considered in this paper." *See* Mansour et al., "VLSI Architectures for SISO-APP Decoders," IEEE Transactions On Very Large Scale Integration ("VLSI") Systems, Vol. 11, No. 4 (Aug. 2003), at 627, *available at* http://shanbhag.ece.illinois.edu/publications/mansr-tylsi-2003-2.pdf (citations removed).

37. As shown by the source code associated with the figure, the soft decision information was then normalized, or "weighted," and then output to either (1) the "interleaver" memory module if performed at the first soft decision decoder or (2) the "deinterleaver" memory module if performed at the second soft decision decoder shown in the figure. Note that the variables "betaQ" and "alphaQ" comprise examples of such soft decision information in the source code:

```

/* normalization of betaQ */

for (i = 0; i < FEC_STATES; i++) {

temp = (Int32)bTemp1[i] - (Int32)norm;

bTemp1[i] = (temp < (-LLR MAX)) ? (IntLLR)(-LLR MAX) : (IntLLR)temp;

}</pre>

```

...

```

/* normalization of alphaQ */

for (i = 0; i < FEC STATES; i++) {

temp = (Int32)alpha2[i] - (Int32)norm;

alpha2[i] = (temp < (-LLR_MAX)) ? (IntLLR)(-LLR_MAX) : (IntLLR)temp;

}</pre>

```

(E.g., see, source code release accompanying 3GPP TS 26.268, ecall\_fec.c, lines 318-352).

38. Additionally, or alternatively, as explained above, all known commercial implementations of 4G LTE turbo decoders were iterative and functionally equivalent to the figures below. The figures below illustrate that soft decision information was stored in the corresponding memory module (*e.g.*, the a posteriori output of SISO 1 is stored in the associated interleaver memory module  $\Pi$ , while the a posteriori output of SISO 2 is stored in the associated de-interleaver memory module  $\Pi^{-1}$ )

*See* Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) (Aug. 20, 2019), *available at* https://www.ncbi.nlm.nih.gov/pmc/articles/PMC7515343/.

39. On information and belief, use of any viable maximum a posteriori (MAP) probability algorithm and/or logarithm approximation algorithm necessarily required weighing (or "normalization"). See Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) 20. 2019), available (Aug. at https://www.ncbi.nlm.nih.gov/pmc/articles/PMC7515343/ (discussing use of a log maximum a posteriori decoding algorithm). See also, e.g., Guohui Wang et al., "High-throughput Contention-Free Concurrent Interleaver Architecture for Multi-standard Turbo Decoder," ASAP 2011-22nd

IEEE International Conference on Application-specific Systems, Architectures and Processors 113 (Sept. 2011) (noting that MAP decoders are used as the component SISO decoders); Cristian Anghel et al., "CTC Turbo Decoding Architecture for LTE Systems Implemented on FPGA," ICN 2012: The Eleventh International Conference on Networks 199, 200 (2012) (describing ideal use of classic MAP algorithm and practical implementation of log-MAP algorithms).

40. The Accused Instrumentalities performed, for a predetermined number of times, iterative decoding from the first to the last of multiple decoders, wherein an output from the last soft decision decoder was fed back as an input to the first soft decision decoder, then from the first to the second decoders, and propagated to the last decoder in a circular circuit, as shown in the figures below:

Figure 18: Turbo decoder

(*E.g.*, 3GPP TS 26.267, at 25 (v. 11), 24 (v. 8)). As shown in the example figure, decoding occurred from the first soft decision decoder, "1st constituent decoder," to the second, or last, soft decision decoder, "2nd constituent decoder." The second soft decision decoder outputs "soft output 2," which is fed as back as an input to the first soft decision decoder. The first soft decision

## Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 49 of 54 PageID #: 49

decoder outputs "soft output 1." This "soft output 1" is fed as input into the second soft decision decoder. The second soft decision decoder is the last soft decision decoder in a circular circuit propagating from the first soft decision decoder to the second soft decision decoder to the first ... to the second to the first to the second, etc. This process was performed a predetermined number of times as defined by the software governing the turbo decoding process. For example, the default number of iterations defined in the source code associated with the figure is 8 iterations, stored in the variable FEC\_ITERATIONS:

| #define | FEC_VAR        | (30206)    | variance: | 1/4550000 in Q37   |

|---------|----------------|------------|-----------|--------------------|

| #define | FEC_MEAN       | (0xB9999A) | mean: 5.8 | in Q21             |

| #define | FEC_ITERATIONS | (8)        | number of | decoder iterations |

| #define | FEC_STATES     | (8)        | number of | decoder states     |

(E.g., 3GPP TS 26.267, at 25 (v. 11), 24 (v. 8)). As another example, FEC\_ITERATIONS is used

during decoding process:

```

/* iterative decoding */

for (i = 0; i < FEC \ ITERATIONS; i++)

memcpy(Le12, Le21, sizeof(IntLLR)*(NRB INFO CRC + NRB TAIL));

/* add received systematic bits to extrinsic information */

for (i = 0; i < NRB INFO CRC+NRB TAIL; i++)

temp = (Int32)Le12[j] + (Int32)syst1[j];

Lel2[j] = (ABS(temp) < LLR MAX)?

(IntLLR)temp : (IntLLR)(SIGN(temp)*LLR MAX);

}

/* decode code one (produces Le12) */

Bcjr(parity1, Le12);

/* interleave extrinsic information (produces interleaved Le12) */

Interleave(Le12, Le21);

/* add received systematic bits to extrinsic information */

for (j = 0; j < NRB INFO CRC; j++)

temp = (Int32)Le21[j] + (Int32)syst1[interleaverSeq[j]];

Le21[j] = (ABS(temp) < LLR MAX)?

(IntLLR)temp : (IntLLR)((SIGN(temp))*LLR MAX);

for (j = 0; j < NRB_TAIL; j++) {

Le_{21}[i+NRB INFO CRC] = svst_{2}[i];

,

/* decode code two (produces interleaved Le21) */

Bcjr(parity2, Le21);

/* deinterleave extrinsic information (produces Le21) */

Deinterleave(Le21);

}

```

(*E.g.*, *see*, source code release accompanying 3GPP TS 26.268, ecall\_fec.c, lines 232-268).

41. Additionally, or alternatively, as above, all known commercial implementations of 4G LTE turbo decoders were iterative and functionally equivalent to the figures below. The figures below illustrates an output from the last soft decision decoder was fed back as an input to the first soft decision decoder, then from the first to the second decoders, and propagate to the last decoder in a circular circuit (*e.g.*, the a posteriori output of SISO 2 is de-interleaved with the associated

memory module and fed as a priori input of SISO 1, while the a posteriori output of SISO 1 is interleaved with the associated memory module and fed as a priori input of SISO 2).

(*E.g.*, Jun Li et al., "Turbo Decoder Design based on an LUT-Normalized Log-MAP Algorithm," Entropy (Basel) (Aug. 20, 2019), *available at* <u>https://www.ncbi.nlm.nih.gov/pmc/articles/</u><u>PMC7515343/</u>). Iterative turbo decoder implementations required completing a certain number of iterations to complete decoding a frame with a satisfactory degree of confidence. Iterative decoding must have therefore been performed a predetermined number of times according to a stopping rule. *See, e.g.*, A. Matache et al., "Stopping Rules for Turbo Decoders," TMO Progress Report 42-142 (Aug. 15, 2000), available at <u>https://ipnpr.jpl.nasa.gov/progress\_report/42-142/142J.pdf</u>.

42. Upon information and belief, Defendant was indirectly infringing by way of inducing infringement and contributing to the infringement of the asserted claim of the '742 Patent in the State of Texas, in this District, and elsewhere in the United States, by providing the Accused Instrumentalities for use as described above by Defendant's customers. Defendant advertised, offered for sale, and/or sold the Accused Instrumentalities to its customers for use in a manner that Defendant knew infringed at least one claim of the '742 Patent. For example, Defendant sold the

### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 52 of 54 PageID #: 52

Accused Instrumentalities advertising that the products operated using 3G and/or 4G-LTE. Defendant was a direct and indirect infringer, and its customers using the Accused Instrumentalities were direct infringers.

43. On information and belief, since becoming aware of the '742 Patent and of the infringement through advertising and offering for sale the Accused Instrumentalities for use by its customers, Defendant was committing the act of inducing infringement by specifically intending to induce infringement by providing the Accused Instrumentalities to its customers and by aiding and abetting its use in a manner known to infringe by Defendant. Since becoming aware of the infringing use of the Accused Instrumentalities, Defendant knew that the use of the Accused Instrumentalities by its customers for a method of iteratively decoding a plurality of sequences of received baseband signals as described in claim 6 constituted direct patent infringement. Despite this knowledge, Defendant continued to encourage and induce its customers to use the Accused Instrumentalities to infringe, including through advertisements. Defendant therefore knowingly induced infringement and specifically intended to encourage and induce the infringement of the '742 Patent by its customers.

44. On information and belief, Defendant committed the act of contributory infringement by intending to provide the identified Accused Instrumentalities to its customers knowing that it was a material part of the invention, knowing that its use was made and adapted for infringement of the '742 Patent as described above, and further knowing that the accused aspect of the Accused Instrumentalities described above were not a staple article or commodity of commerce suitable for substantially noninfringing use. As described above, Defendant was aware that all material claim limitations were satisfied by the use and implementation of the Accused

52

### Case 4:24-cv-00357-SDJ Document 1 Filed 04/25/24 Page 53 of 54 PageID #: 53