####

CLERK, U.S. DISTRICT COURT NORTHERN DISTRICT OF CALIFORNIA

Xiaohua Huang, *pro se* P.O. Box 1639, Los Gatos CA95031 Tel: 669 273 5633 Email: <u>paul-huang03@outlook.com</u>

FOR THE NORTHERN DISTRICT OF CALIFORNIA IN THE UNITED STATES DISTRICT COURT るも 07181 **SKO**

Xiaohua Huang Pro Se,

Civil Action No .:

TRIAL BY JURY DEMANDED

Plaintiff,

TetraMem, Inc.

۷.

Defendant.

### INFRINGEMENT OF PATENT PLAINTIFF XIAOHUA HUANG'S COMPLAINT FOR

("TetraMem" or "Defendant and respectfully alleges as follows: Complaint for Patent Infringement against Defendants, THAT'S TetraMem, Inc. Plaintiff, Xiaohua Huang ("Plaintiff" or "Huang"), hereby files his

# NATURE OF THE ACTION

illegal and unauthorized manner and without authorization and/or consent from hereto as Exhibit A and incorporated herein by reference, and pursuant to 35 U.S.C. Plaintiff, from U.S. Patent No. RE45259 (the "RE259patent" which is attached Inc. (hereinafter "TetraMem" or "Defendant") from infringing and profiting, in an United States, 35 U.S.C. §101, et seq., to prevent and enjoin Defendant TetraMem, 1 This is a civil action for patent infringement under the Patent Laws of the

§271, and to recover damages and costs

#### THE PARTIES

N 2000, one of those patents is US Patent RE45259 circuit and logic design to build high speed and low power IC chip since the year of Huang has developed the state of the art high speed and low power U.S. patented Xiaohua Huang is an individual, he currently resides at Campbell, CA95008

00 Lab. and continued in University of Massachusetts and University of Southern Mr. Joshua Yang address https://www.tetramem.com/. TetraMem is or purports to be a company having its head quarter office in: 4027 Clipper Ct, Fremont, CA 94538 with its website and Qiangfei Xia based on the ReRAM research initiated from TetraMem was founded by Mr.Glenn (Ning )Ge HP

# JURISDICTION AND VENUE

sued in this judicial district regular business and main office in 4027 Clipper Ct, Fremont, CA 94538 can be et seq. This Court has jurisdiction over the subject matter of this action pursuant to U.S.C. §§1391(b) - (c) and 28 U.S.C. § 1400(b) in that Defendant which has its 4 28 U.S.C. §§ 1331 and 1338(a). Venue is proper in this District pursuant to 28 This action arises under the patent laws of the United States, 35 U.S.C. § 101,

# BACKGROUND FACTUAL ALLEGATION

U1 A true and correct copy of the 'RE259patent is attached hereto as Exhibit A.

California

The RE259patent is valid and owned by Plaintiff Mr. Huang as the inventor patented high speed and low power IC design circuit and logic such as the circuit California. Huang developed advanced TCAM design in CMOS and invented many 29 of US patent RE45259 read the circuit and logic design found in the ReRAM IP and logic design claimed in the claim 29 of US patent RE45259. At least the claim <u></u> and chip which have been designed and made by TetraMem in its office in 4027 Clipper Ct, Fremont, CA 94538 In Nov. 2000 "Huang" found CMOS Micro Device Inc. ("CMOS") in Campbell,

7. by defendant's conduct, Plaintiff were prejudiced by the Court, plaintiff withdrew of the previous cases to defame Plaintiff and cheat the Court. The Court was biased Defendant's Counsel used all the erroneous information and the erroneous decision cv-1413 Mr. Xiaohua Huang v. Huawei Technologies Ltd. to prove that Plaintiff is a that complaint. In case 5:23-cv-04936-SVK defendant Counsels uses case No. 2:15-Roy Payne. Case No. 2:15-cv-1413 was my first case filed I have no any experience and knowledge of the Court and litigation. I collected and produced evidence that many chips used in Huawei's Internet router and switches infringes my asserted patents. Judge Roy Payne was very kind and nice to me and gave me two frivolous litigant because Plaintiff was sanctioned by Judge Judge Rodney Gilstrap/ month time to retain the counsels who are very experienced in the local court. counsels. After that Huawei used six its employees, one internal counsel and the have been grateful and felt in debt to Judge Payne although I failed to retain the In previous case 5:23-cv-04936-SVK, under Defendant's instruction

ω

Case 5:24-cv-07181-VKD Document 1 Filed 10/15/24 Page 4 of 66

the errors made by Judge. Some defendant counsels used what the Court taking the in debt to Hon. Judge Alsup and Kim. Everyone knows that my case with Huawei employees of MediaTek to make perjured declaration to cheat the Judge and win No. 2:15-cv-1413 was erroneously decided by the Courts. The court system tolerates the case. I should follow Judge Kim. Although losing the case but I am grateful and then Brandon Story imitated Huawei's case No. 2:15-cv-1413 and have the pay one-tenth of the amount that Judge Kim mediated. The case was not settled the mediation result. After that Brandon Story told me that his client only want to times more than the amount which Judge Kim mediated for me, so I did not accept defendant to pay me the particular amount to settle the case, that amount is many Counsel Brandon Stroy cheated me and said to me that he can help me to have the William Alsup assigned Magistrate Jude Kim to mediate the case. Defendant Inc., but MediaTek refused to pay anything to me, I filed complaint in 2018. Hon. TCAM for their networking chips, then the power consumption of MediaTek's chip taught the engineers of MediaTek how to use my patents to design the low power cv6654 Mr. Xiaohua Huang v. Nephos Inc. was the third case I filed. In 2014 I to judge me loose the case and have me sanctioned. Defendant Counsels uses case reduced from over 200watt to much less than 100 watt, and sold to Amazon.com, No. 3:18-cv-6654 Mr. Xiaohua Huang v. Nephos Inc. to defame me. Case No. 3:18material evidence the Court took Huawei's false statement and perjured declaration evidence to prove all the Huawei's declaration are contradictive to the public counsels to make false statement and perjured declaration. Although I produced the

objectively to make erroneous decision Serpent seduces Eve, to imitate case No. 2:15-cv-1413 rather than focus on the case statements and perjured declaration and successfully induced the trial court, as 1413 made erroneous judgment as reference example to attack me, make false false statements and perjured declaration in Xiaohua Huang v. Huawei No. 2:15-cv-

conduct descendants suffered such as the Jewish have suffered from King David's wrongful their personal interests , do not mention their conduct would have their NOVEMBER 20, 2023. Some attorneys even violates the law and commits crime for Disbarred in the Third Quarter of 2023 BY STATE BAR OF CALIFORNIA ON descendants suffer from their wrongful conduct. State Bar Announces 23 Attorneys violated their oath to the God, their conducts may have himself, his family and counselor at law to the best of my knowledge and ability. As an officer of the court, I Defendant Counsels such as PAUL J. ANDRE, LISA KOBIALKA, VIOLAINE have will strive to conduct myself at all times with dignity, courtesy, and integrity." support the Constitution of the United States and the Constitution of the State of GOD by putting his/her hand on bible "I solemnly swear (or affirm) that I will California, and that I will faithfully discharge the duties of an attorney and In California, before obtaining the permission, the lawyer solemnly declares to

their other unethical illegal conducts. Defendant and their founders filed many information to defame Plaintiff and cheat the Court are somehow consistent with Defendant's conduct of instructing their Counsels to lie, cheat and use false

Ś

science journal then obtained tens of million USD income (investment). TetraMem licensing sample chips, measured some data from those chips and published the papers on has offered to sell its ReRAM designed with using US patent RE45259 without and refuse to license. Defendants have used Plaintiff's patent to have built several patents to protect their own technology, but use Plaintiff's patent without licensing

product use "1T,1R" ReRAM structure. Plaintiff pointed out defendant RE45259 to one embodiment, but in the same time disclosed that defendant's sent Plaintiff an email in Exhibit 3 and tried to narrow the claim 29 of US patent on how defendant's products infringe the us patent RE45259 Exhibit X1. Defendant Defendant in Exhibit 3 that defendant's product is design with "1R 1T" structure which is consistent with the structure of Figure 2 and Figure 3 in plaintiff's analysis  $\infty$ The new complaint is also based on the new further information provided by

# MADE AND SOLD THE INFRINGING PRODUCTS WHICH DEFENDNAT MAY HAVE

counsel's cheating conduct with Exhibit 4 and Exhibit 5

page 6 of Exhibit 1 the joint news release made by TetraMem and Synopsys offer to IC with the function which read the claim 29 of US patent RE45259. In page 5 and TetraMem, including but not limited to embedded RRAM IP and chips contains the 9. Based on the information obtained that the products made by Defendant

X1. have infringed claim 29 of US patent RE45259 is analyzed and explained in Exhibit TetraMem's ReRAM employ "1T, 1R" (1 transistor, t resistor) which is consistent with Figure 2 and Figure 3 in Exhibit X1. How and why the RRAM of TetraMem RRAMbased in-memory computing technology .....". Exhibit 3 also claims that sell the RRAM of TetraMem with its marketing name "TetraMem's analog-

# **COUNT I: INFRINGEMENT OF U.S. PATENT NO. RE45259**

above. 10. Plaintiff refers to and incorporates herein the allegations of Paragraphs 1-9

in and to the 'RE259 patent and circuits." A true and correct copy of the 'RE259patent is attached hereto duly and legally issued for a "Hit ahead hierarchical scalable priority encoding logic 11. Exhibit A. Xiaohua Huang as inventor is the owner of all rights, title, and interest On November 25, 2014 U.S. Patent No. RE45259 (the"RE259Patent") was as

35 U.S.C. § 271(a), (b) and(c). and logic function which have infringed at least claim 29 of the 'RE259 patent under claims of the RE259 patent through making ReMAM IP and chips containing circuit to infringe directly, indirectly, literally, on Doctrine of Equivalent one or more of the 12. On information and belief, Defendant TetraMem has infringed and continue

~1

in prosecuting this action under35 U.S.C. § 285 Huang to recover damages under 35 U.S.C.§284 and to legal fees and costs incurred law, unless enjoined by this Court. Defendant's infringement entitle Xiaohua Xiaohua Huang, causing irreparable harm for which there is no adequate remedy at Xiaohua Huang exclusive rights under the 'RE259 patent will continue to damage wrongful acts in an amount subject to proof at trial. Defendant's infringement of 14. staple article or commodity of commerce suitable for substantial non-infringing use reading and writing data and information in accused devices are completely not a infringes the claim 29 of RE259 patent. The Customers of the Defendant uses the Defendant for the damages sustained by Xiaohua Huang as a result of Defendant's caused and logic reading the claim 29 of the 'RE259 patent. The using of function of function of reading and writing data and information which contains the circuit of Equivalent the claim 29 of the 'RE259 patent by using the devices which to have infringed and continue to infringe directly, indirectly, literally, on Doctrine 13. Defendant TetraMem's acts of infringement, inducing infringement have damage to Xiaohua Huang, and Xiaohua Huang is entitled to recover from On information and belief, Defendant TetraMem has induced its Customers

### **JURY DEMAND**

15. Pursuant to Fed. R. Civ. P. 38(b), Plaintiff Xiaohua Huang requests a trial

by jury on all issues.

# PRAYER FOR RELIEF

the 'RE259 patent under 35 U.S.C. § 284; (e). An assessment of interest on damages; (d). An accounting for damages resulting from Defendant's infringement of foregoing, from further acts of infringement of the 'RE259; attorneys and all others in active concert or participation with any of the subsidiaries, parents, officers, directors, agents, servants, employees, affiliates (c). An order preliminarily and permanently enjoining Defendant and its infringed and is infringing U.S. Patent No RE45259; (b). A judgment that the 'RE259 patent is valid and enforceable; (a). A judgment in favor of Xiaohua Huang that Defendant TetraMem has WHEREFORE, Xiaohua Huang prays for the following relief:

,

(g). Such other and further relief as this Court may deem just and

otherwise provided by law;

prosecuting this action, with interest pursuant to 35 U.S.C. § 285 and as

disbursements, expert witness fees, and legal fees and costs incurred in

(f). A judgment awarding damages to Xiaohua Huang for its costs

equitable.

.

Xiaohua Huang

P.O. Box 1639, Los Gatos CA95031 Tel: 669 273 5633 Email: <u>paul-huang03@outlook.com</u>

Exhibit A US patent RE45259 Exhibit 1 pre-suit background Exhibit 2 Tetramem-paper Exhibit 3 TetraMem letter Exhibit 4 Response to TetraMem letter Exhibit 5 TetraMem claimed info

Exhibit X1 Pre-suit analysis

.

# US patent RE45259

-

# (19) United States

# (12) Reissued Patent

#### Huang

### (10) Patent Number: US RE45,259 E (45) Date of Reissued Patent: Nov. 25, 2014

### HIT AHEAD HIERARCHICAL SCALABLE (56) PRIORITY ENCODING LOGIC AND

(<u>54</u>)

# U.S. 1

# **U.S. PATENT DOCUMENTS**

**References** Cited

| 7,464,217 B2*          | 7,043,601 B2 *         | 6,505,271 BI*      | 6,392,910 BI * | 6,307,767 BI * | 6,249,449 BI *         |

|------------------------|------------------------|--------------------|----------------|----------------|------------------------|

| 12/2008                | 5/2006                 | 1/2003             | 5/2002         | 10/2001        | 6/2001                 |

| Braceras et al 711/108 | McKenzie et al 711/108 | Lien et al 711/108 | Podaima et al  | Fuh            | Yoneda et al 365/49.18 |

#### \* cited by examiner

Primary Examiner — Han Yang

#### ABSTRACT

(57)

In this invention a hit ahead multi-level hierarchical scalable priority encoding logic and circuits are disclosed. The advantage of hierarchical priority encoding is to improve the speed and simplify the circuit implementation and make circuit design flexible and scalable. To reduce the time of waiting for previous level priority encoding result, hit signal is generated first in each level to participate next level priority encoding, and it is called Hit Ahead Priority Encoding (HAPE) encoding. The hierarchical priority encoding can be applied to the scalable architecture among the different sub-blocks and can also be applied with in one sub-block. The priority encoding and hit are processed completely parallel without correlation, and the priority encoding, hit generation, address encoding and MUX selection of the address to next level all share same structure of circuits.

### **36 Claims, 8 Drawing Sheets**

(Sg

Field of Classification Search

USPC

See application file for complete search history.

... 365/49.1, 230.01, 230.05, 230.06

(52)

U.S. CL

USPC .....

**365/49.1**; 365/230.01; 365/230.05; 365/230.06

(51)

Int. Cl. GIIC 15/00

(2006.01)

8

Provisional application No. 60/550,537, filed on Mar.

4, 2004.

U.S. Applications:

Appl. No.: Filed:

7,652,903 Jan. 26, 2010 11/073,116 Mar. 4, 2005

Reissue of: (64) Pater

Patent No .:

Issued:

(76) (22)

Filed:

Jan. 20, 2012

**Related U.S. Patent Documents**

Appl. No.: 13/355,449

Inventor:

Xiaohua Huang, San Jose, CA (US)

CIRCUITS

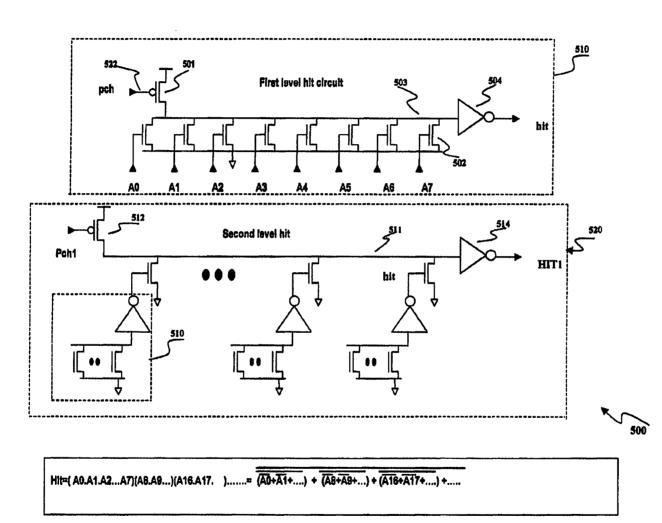

Figure 2b.

Nov. 25, 2014

14 Sheet 5 of 8

Figure 5

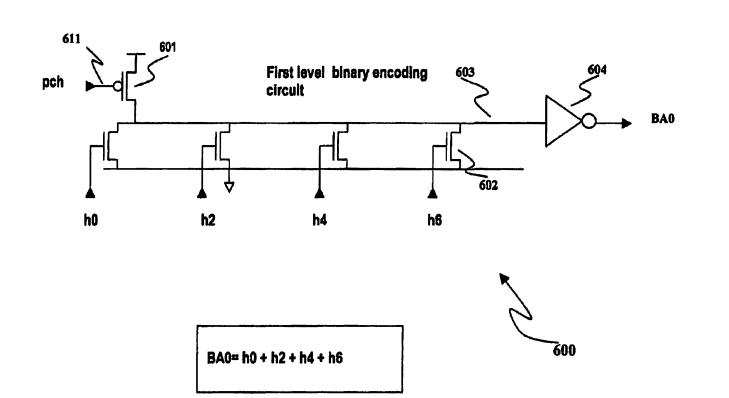

Figure 6

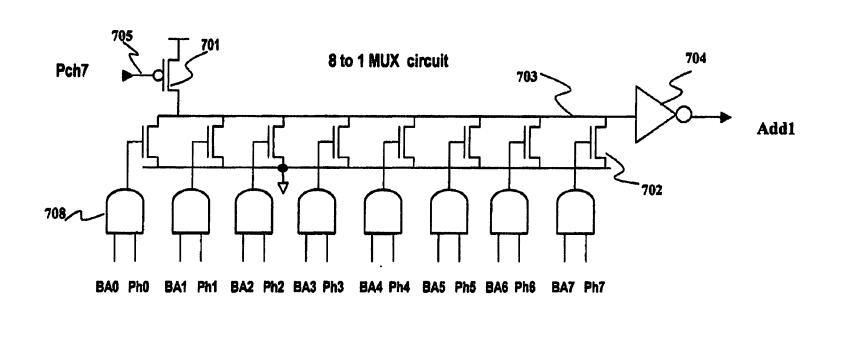

Figure 7

•

#### HIT AHEAD HIERARCHICAL SCALABLE PRIORITY ENCODING LOGIC AND CIRCUITS

tion; made Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specificamatter printed in italics indicates the additions by reissue.

herein by reference in its entirety for all purposes. This application claims the benefit of provisional U.S. Application Ser. No. 60/550,537, entitled "Priority encoding logic and Circuits," filed Mar. 4, 2004, which is incorporated

# FIELD OF THE INVENTION

priority encoding of match or hit address. particular, the present invention relates to logic and circuits of The presentation relates to content addressable memory. In

# BACKGROUND OF THE INVENTION

address is called priority encoding. priority address. In multi-hit case, one protocol was made to select the highest row matching the input content, it is called multi-hit or match cess, so some time in one comparison, there are more than one each row are compared in the searching or comparing pro-Б ternary content addressable memory, not every bit in The logic of selecting the highest priority

ity and  $A_m$  has the lowest priority. Assume some of  $\{A_0, A_1, \ldots, A_{m-1}, A_m\}$  are logic "1" and all of the others are logic "0", the priority encoding keen the history priority encoding the source of the bistory priority encoding the bistory e Assume we have  $\{A_0, A_1, \ldots, A_{n-1}\}$  hit signals from the corresponding addresses and define  $A_0$  has the highest priority and  $A_n$  has the lowest priority. Assume some of  $\{A_0, A_0, A_0\}$ this transform: "0", the priority encoding keep the highest priority "1" as "1" and convert all the other "1" into "0". The logic operation of

ŝ

#### Â, , Aj, ... $\mathbf{A}_{n-1}, \mathbf{A}_n \} \Longrightarrow \{\mathbf{h}_0, \mathbf{h}_1, \dots, \mathbf{h}_{n-1}, \mathbf{h}_n\}$

Ξ

ŧ

### can logically be expressed as:

| : | $h_2 = \overline{A}_0 * \overline{A}_1 * A_2$ | $h_l = \overline{A}_0 * A_l$ | $h_0 = A_0$ |  |

|---|-----------------------------------------------|------------------------------|-------------|--|

|   |                                               |                              | (2)         |  |

F  $=\overline{A}_0 * \overline{A}_1 * \overline{A}_2 \cdots A_{n-1} * \overline{A}_n$

otherwise no matter  $A_i=0$  or 1,  $h_i=0$ . Which means only when  $A_0$  to  $A_{t-1}$ , are all zero,  $h_i = A_i$ , SS

After the priority encoding, the hit address with the highest

calculation of priority logic (2) will take long time if we use If the entry N are large, say 1K to 128K or even 1M, the serial logic.

8

described in the following So we come out the inventions which will be

# SUMMERY OF THE INVENTION

scalable priority encoding. For example we make 8 entry as In this invention, we propose a multi-level hierarchical 55

> circuit implementation and make circuit design flexible and priority encoding is to improve the speed, and simplify the scalable 64 entry. Then we can make 8 second level as third level, total 512 entry, and so on. The advantage to make hierarchical one group as first level and 8 first level as a second level, total

Ahead Priority Encoding (HAPE) encoding. encoding result, we generate the hit signal first in each level to participate next level priority encoding, and we call it Hit To reduce the time of waiting for previous level priority

5

also be applied with in one sub-block. scalable architecture among the different sub-blocks and can The hierarchical priority encoding can be applied to the

# BRIEF DESCRIPTION OF THE DRAWINGS

15

described, by way of exa attached Figures, wherein: Preferred embodiments of the invention will now by way of example only, with reference to the ğ

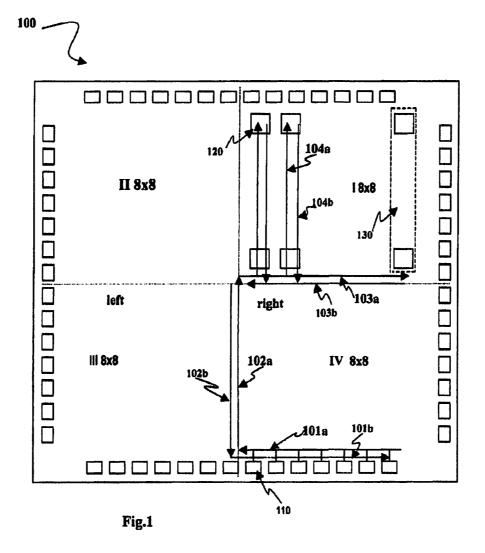

with many sub-block in accordance with one embodiment of the present invention. FIG. 1 is a block diagram of scalable architecture of CAM

20

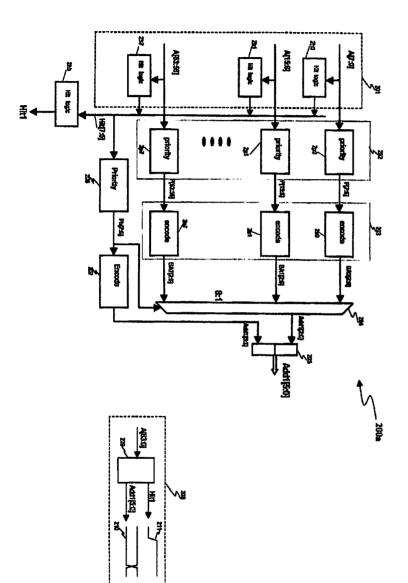

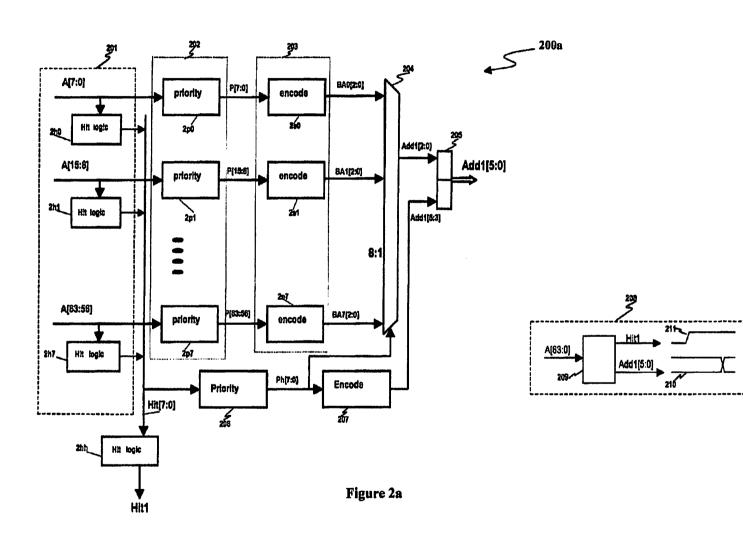

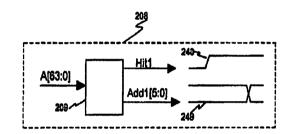

uon. block in accordance with one embodiment of present invenencoding and match address binary encoding within one sub-FIG. 2a is a logic block diagram of hierarchical priority

2

2b of present invention. FIG. 2b is the and timing diagram in accordance with FIG

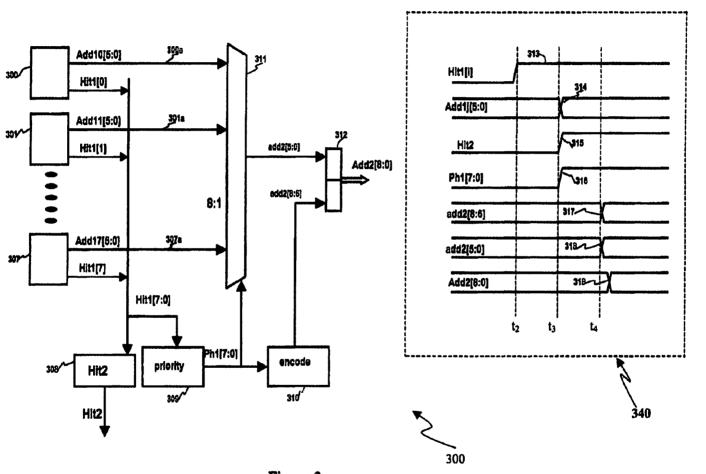

encoding and match address binary encoding in higher level or among the different sub-block and timing diagram in accordance with one embodiment of present invention FIG. 3 is a logic block diagram of hierarchical priority

ы

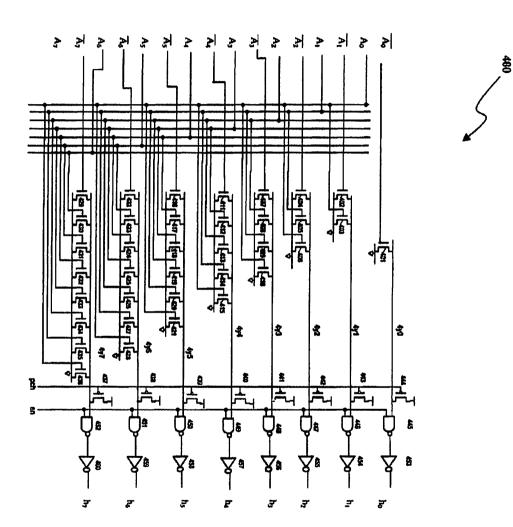

with 8 input address in accordance with one embodiment of FIG. 4 is the circuit implementation of priority encoding

present invention. logic address in accordance with one embodiment of present FIG. 5 is the circuit implementation of the HIT generation

logic in accordance with one embodiment of present inven-Invention FIG. 6 is the circuit implementation of binary encoding

LIOD accordance FIG. 7 is the circuit implementation of 8 to 1 mux in with one embodiment of present invention.

#### DETAILED DESCRIPTION OF THE INVENTIONS

\$

divided into four quadruple, each quadruple has 8x8=64 block and each block has 8x8=64 entry as shown in FIG. 1 To make the priority encoding logic calculation quicker, the entire CAM block can be divided into 256 block and with embodiment 100.

S

of the chip. If all of the data pad 110 are in one side or less than four side, the principle is same. Assume the data pad 110 are equally distributed in four side This is just to explain the principle, the entry number of each sub-block and the number of sub-block can be different.

8 column both upper part and down part shown as 104a in FIG. 1. Fifth step, the data to be compared are then sent to First step, route all the data signal in each side (only one side are drawn in the FIG. 1) to the middle point of that side, which is shown as route 101a in FIG. 1. Second step, route all each sub-block 120 in each column to perform the compariis shown in FIG. 1. Fourth step, send data to each one of the compared to both left and right side (only right side path 103a FIG. 1. Third step, in the center point send the data to be the data signal to the center of the chip shown as route 102a in

each 110 through path 101b. The priority encoding among upper muschangle and lower part quadruple can be performed path 102b. Last step the hit address are sent to the output pad priority encoding will be performed in the center of chip among four quadruple and the hit address will be sent through will be performed among 8 column 130 in each quadruple and the Hit address are sent out through path 103b. Next step the third level priority encoding and the hit address are sent out through path 104b. Next step fourth level priority encoding explained in details in FIG. consumption. After comparison with each entry inside each sub-block 120, the first level and second level priority encodthat case, the data path start from path 104a. If only some selected sub-block are searched or compared, the data to be compared will only be sent into those sub-block to save power ing and application, the entry number of TCAM is not very large. In son with each entry in every sub-block 120. In embedded column 130 among 8 sub-block will be performed as binary encoding are performed which will be d in details in FIG. 2, then the priority encoding in

ю

same as any block 2h0 to 2h7 and generate the next level Hit1. Both Add1[5:0] and Hit1 will be passed to the next level. 207 which is logically same as the binary encoding block from 2e0 to 2e7 to generate the address: Add1[5:3]. Add1[5: 3] and Add1[2:0] make Add1[5:0]. Hit[0] to Hit[7] further perform the logic function in block 2hh which is logically exact same as the priority encoding in each 8 entry group from 2p0 to 2p7. The Priority Hit Ph[7:0] from Hit[0] to Hit[7] will select the 8 to 1 mux 204 and select one three bit binary address from BA0[2:0] to BA7[2:0] and become Add1[2:0]. group. The eight signal of Hit[0] to Hit[7] from block 201 will each block from 2p0 to 2p7 of embodiment block 202 to generate P[63:0], then proceed binary encoding from 2e0 to 2e7 in embodiment block 203 to generate any three bit BA0 [2:0] to BA7[2:0] binary address if there is a hit in any 8 bit The priority encoding logic calculation block diagram for each 8x8=64 entry sub-block 120 are shown in FIG. 2a with embodiment 200a. Each 8 entry of 64 entry are grouped together to do hit logic function from 2h0 to 2h7 and generate The priority bit of Hit[0] to Hit[7] is binary encoded in block perform priority encoding in block 206 which is logically 64 entry are performed priority encoding logic calculation in Hit[0] to Hit[7] in block 201. In the same time each 8 entry of together in path 103b. \$ ы S 2 8

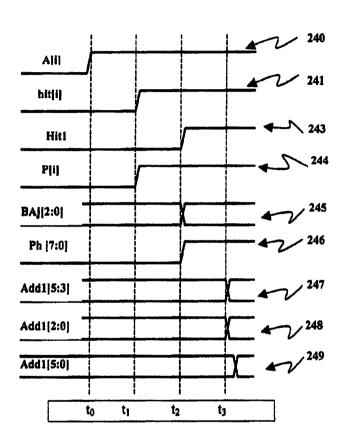

divided into eight group and priority encoded by block 2p0 to 2p7, generating P[0] to P[63] which are drawn as 244 and available at time  $t_1$ . The time delay of generating Ph[7:0] which are drawn as 246 and the time delay of generating BA0[2:0] to BA7[2:0] which are drawn as 245 are roughly signal 240 are available in time  $t_{00}$  the first level hit signal Hit[7:0] generated by block 2h0 to 2h7 are drawn as 241 The timing diagram of embodiment 200a is shown in FIG. 2b with embodiment 200b. Assume all the Hit or miss signal from TCAM comparison A[i] (A[63:0])which is drawn as Which is available at time  $t_1$ . In the same time A[63:0] are £

S

same and they are generated in time t<sub>2</sub>. So the Binary address Add1[2:0] which are drawn as 248 are selected by Ph[7:0] from the 8 group address BA0[2:0] to BA7[2:0] through an eight to one MUX 204 without any further delay except the delay of MUX itself which is  $(t_3-t_2)$ , and the address Add1 [5:3] which are drawn as 247, Add1 [2:0] and Add[5:0] which e drawn as 249 are available at time  $t_3$ . So the total delay from A[63:0] available to the output of 8 ŝ

delay of Hitl 243 is two stage delay. So the output of Hitl which is available at  $t_2$  which is one stage earlier than the ority 2p0, binary encoding 2e0 and 8 to 1 MUX 204), where we call each block(2p0, 2e0 and 204 etc) as one stage. The binary hit address Add1[5:0] is about three stage delay(pri-

ß

at t<sub>3</sub>. Only Hitl and Add1[5:0] are sent to the next level priority encoding. The entire sub-block are abstracted as symbol 208. The timing delay of hit, priority encoding, binary encoding and 8 to 1 mux will be analyzed in details. output of binary Hit address Add 1 [5:0] 249 which is available

MUX 311. signal Hit1[7:0] which is marked as 313 in FIG. 3 are one higher level among the eight group of 64 entry sub-block or [7:0] perform priority encoding in block 309, then the priority hit signal Ph1[7:0] will select Add2[5:0] from the eight input stage earlier than the binary hit address Add10[5:0] to Add17 [5:0] which are marked as 314. Eight bit HIT signal of Hit1 among the 8 sub-block in every column 130 in FIG. 1. The Hit FIG. 3 is the logic block diagram of priority encoding of

5

to wait for the selection signal. selection signal from the priority encoding among the hit signals is available one stage earlier and there is no extra delay [8:0] which is marked as 319 is an 8 to 1 MUX delay which is  $(t_4-t_3)$ , where i=0 to 7. In this hierarchical priority design, the delay on each level is an 8 to 1 MUX delay because the Add2[8:0]. From the timing diagram 340 in FIG. 3, the delay of binary hit address Add1i[5:0] which is signal 314 to Add2 time t<sub>3</sub> which is one stage earlier than Binary hit address Add2[8:0]. In block 308 eight input Hit1[7:0] generate Hit2 at Add2[8:6] in block 310. Add2[8:6] and Add2[5:0] make In the same time Ph1[7:0] are encoded into binary address

function block 206, 309 in each level are same that the simplicity of circuit design. We already see that each level shares the same logic and circuit design. Say, the priority circuit, which is shown in FIG. 4, embodiment 400. Another advantage of this hierarchical priority encoding is in logic

the priority logic equation (2) which can be deduced to equation (3), where n=7. Embodiment 400 in FIG. 4 is a sample implementation of

$$h_0 = A_0$$

$$h_1 = \overline{A_0 + A_1} = \overline{A_0 + \overline{A_1}}$$

(3)

$$h_2 = \overline{A_0} * \overline{A_1} * A_2 = \overline{A_0 + A_1 + \overline{A_2}}$$

$$\mathbf{h}_n = \overline{\mathbf{A}}_0 \ast \overline{\mathbf{A}}_1 \ast \overline{\mathbf{A}}_2 \ \dots \ \overline{\mathbf{A}}_{n-1} \ast \mathbf{A}_n = \overline{\mathbf{A}}_0 + \overline{\mathbf{A}}_1 \ \dots \ + \ \overline{\mathbf{A}}_{n-1} + \overline{\mathbf{A}}_n$$

en is set to logic zero which makes all the output of NAND gate 445 to 452 to logic one and then turn all the output of inverter 453 to 460 into logic zero. The input pch of the P transistors 437 to 444 are set to logic zero and the P transistor 437 to 444 are turned on, which make the line 4y0 to 4y7 signal among A0 to A7 will be logical zero at potential A7 will be logical "one" at potential Vdd and the before the TCAM comparison results  $A_0$  to  $A_7$  and their complementary  $\overline{A}_0$  and  $\overline{A}_7$  arrive. The Hit signal among A0 to potential level of line 4y0 to 4y7 up to Vdd, then the signal pch connecting to Vdd with low impedance and pre-charge the ground. Only the highest priority hit, the output of the NOR is turned into Vdd and turn off the P transistors 437 to zero which turn off all the N transistors and the enable signal beginning of each cycle, the gate input signals  $\overline{A_0}$  to  $\overline{A_7}$  and  $A_0$  to  $A_7$  of all the N transistor from 401 to 436 are set to logic NOR logic of N transistor connected to that N transistors and each line 4y0 to 4y7 is the output of dynamic The equation (3) is implemented as embodiment 400 in FIG. 4. Each line from 4y0 to 4y7 connect the drains of a few line. At the missed 4

**S** gates are logically high. For example,  $A_0=0$ ,  $A_1=0$ ,  $A_2=Vdd$ and  $A_3=Vdd$ , the highest priority hit is  $A_2$ . The input of N transistor 401 is Vdd and N transistor 401 is turned on and the node 4y0 is discharged to ground. The input of transistor 402 which is the complementary of  $A_1$  is also Vdd and the transistor 402 is ON, the node of 4y1 is also discharged to ground. Since  $A_0=0$ ,  $A_1=0$ ,  $A_2=Vdd$ ,  $\overline{A_2}=0$ , so the inputs of tran-

sistors 404, 405, 406 are all zero and the transistor 404, 405, 406 are all OFF and the node 4y2 will not be discharged and will be kept logically "one" at potential Vdd. Since  $A_2$ =Vdd, 10 the inputs of transistors 408, 413, 419, 426 and 434 will be Vdd and all the node 4y3, 4y4, 4y5, 4y6 and 4y7 will be pulled to ground no matter if  $A_3$ ,  $A_4$ ,  $A_5$ ,  $A_6$  and  $A_7$  are logically one or zero. The slowest path or worst case is only one input among eight N transistor 429, 430, 431, 432, 433, 434, 435 and 436 connected to node 4y7 is Vdd and all the others are zero, in that case one transistor need to discharge the drain parasitic capacitance of eight transistor and the metal wire capacitance connected to node 4y7. The signal en is characterized to turned to Vdd later then node 4y7 is discharged in 20 worst case. The worst case delay of eight input priority encoding is that one N transistor discharging the drain parasitic capacitance of eight same size N transistor down to ground plus the delay of one NAND gate and one inverter.

worst case, the delay of 510 is that one N transistor discharge the drain parasitic capacitance of the eight same size N tranin FIG. 5. The embodiment 510 is the circuit implementation of one block 2h0 and the embodiment 520 is the circuit implementation of both block 201 and block 2hh in FIG. 2a sistor down to ground plus the delay of one inverter among A0 to A7 is Vdd and all the others are zero, which is the and the output signal of inverter 504 is zero. If only one input the N transistors 502 are OFF and the node 503 is kept in Vdd transistor **S01** before the signal A0 to A7 arrive. If all the input A0 to A7 are zero, the input of N transistors are zero and all gate input S22 of P transistor S01 to zero to pre-charge the node 503 to Vdd, then turn 522 to Vdd and turn off the P to A7 are set to zero as in embodiment 400 in FIG. 4. 2) Set the together. The operation principle of 510 is: 1) all the input A0 in each level is also same and its logic and circuit are shown The logic of Hit function block 2h0, 2h1, ... 2hh and 308 8 ŝ ä 25

The binary encoding logic and circuit is shown as embodiment 600 in FIG. 6. The operation principle of 600 is: 1) all the input  $h_0$ ,  $h_2$ ,  $h_4$  and  $h_6$  are set zero. 2) Set the gate input 611 of P transistor 601 to zero to pre-charge the node 603 to Vdd, 45 then turn 611 to Vdd and turn off the P transistor 601 before the signal  $h_0$ ,  $h_2$ ,  $h_4$  and  $h_6$  arrive. If all the input signal  $h_0$ ,  $h_2$ ,  $h_4$  and  $h_6$  are zero, the input of N transistors are zero and all the N transistors 602 are OFF and the node 603 is kept in Vdd and the output signal of inverter 604 is zero. If only one input 50 among  $h_0$ ,  $h_2$ ,  $h_4$  and  $h_6$  is Vdd and all the others are zero, which is the worst case, the delay of 600 is that one N transistor discharging the drain parasitic capacitance of the four same size N transistor down to ground plus the delay of one

The MUX logic and circuit is shown in FIG. 7 as embodiment 700. The operation principle of 700 is: 1) the input signal Ph<sub>0</sub>, Ph<sub>1</sub>, Ph<sub>2</sub>, Ph<sub>3</sub>, Ph<sub>4</sub>, Ph<sub>5</sub>, Ph<sub>6</sub> and Ph<sub>7</sub> are set zero. 2) Set the gate input 705 of P transistor 701 to zero to precharge the node 703 to Vdd, then turn 705 to Vdd and turn off the P transistor 701 before the signal Ph<sub>0</sub>, Ph<sub>1</sub>, Ph<sub>2</sub>, Ph<sub>3</sub>, Ph<sub>4</sub>, Ph<sub>5</sub>, Ph<sub>6</sub> and P<sub>7</sub> arrive. Since Ph<sub>0</sub>, Ph<sub>1</sub>, Ph<sub>2</sub>, Ph<sub>3</sub>, Ph<sub>4</sub>, Ph<sub>5</sub>, Ph<sub>6</sub> and Ph<sub>7</sub> are from Priority encoding, only one signal among them is Vdd and all the other are zero if there is hit. After AND logic, only one output of the seven AND gate 708 is equal to 65 the input value which is the selected bit from Ba<sub>0</sub> to Ba<sub>7</sub>. If the

from Bao to Ba7 is zero, the node 703 is kept Vdd

and the output of inverter 704 is zero and the selected bit value zero is passed out. If the selected bit from Ba<sub>0</sub> to Ba<sub>2</sub> is Vdd, one N transistor among eight N transistor 702 is turned ON and the node 703 is discharged down to ground and the output of inverter 704 is Vdd(logical one) and the selected bit value Vdd is passed out, which is the worst case, the delay of 700 is one N transistor discharging the drain parasitic capacitance of the eight same size N transistor down to ground plus the delay of one inverter and one AND gate. Usually one AND gate includes one inverter and one NAND gate, so the delay of 700 is one N transistor discharging the drain parasitic capacitance of the eight same size N transistor down to the ground plus the delay of two inverter and one NAND gate.

The entire Priority encoding logic and circuit are simplified as a four basic building block of 400, 510, 600 and 700 in FIGS. 4, 5, 6 and 7. The delay of each block 400, 510, 600 and 700 are comparable and we call the time of delay of each block 400, 510, 600 and 700 one stage. If we define the delay of hit logic block 510 as  $T_{\mu}$ , one inverter delay is  $T_{\mu}$  and one NAND gate delay is  $T_{\mu}$ . The delay of priority encoding block 400 is  $(T_{\mu}+T_{\mu})$  since the delay of block 400 is one more NAND gate delay comparing with block 510. The delay of block 600 is roughly  $T_{\mu}$ . The delay of MUX block 700 is  $(T_{\mu}+T_{\mu}+T_{\mu})$ . The extra delay of each higher level priority encoding is a MUX 700 selection delay because that the Hit signal in each priority encoding level is generated one stage earlier than the binary hit address and the selection signal of the MUX is already available when the binary address to be selected arrive and will not suffer extra delay. The previous description of the disclosed embodiments is

The previous description of the disclosed embodiments is provided to enable any person skilled in the art to make or use the present invention. Various modifications to these embodiments will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other embodiments without departing from the spirit or scope of the invention. Thus, the present invention is not intended to be limited to the embodiments shown herein but is to be accorded the widest scope consistent with the principles and novel features disclosed herein.

What is claimed is:

1. A content address able memory(CAM) and hit ahead priority encoding(HAPE) logic, comprising: a group of blocks which is arranged in column and row,

"zero" which is called miss, each block generates block hit when there is at least one CAM match signal is high logic "one" within the block or block miss signal when a group column, a group of column generates a hit signa priority encoding logic of column hit or miss signals of signal within the column or column miss signal when column hit signal when there is at least one block hit miss signals of each column, each column generates all the CAM match signals are in low logic level "zero" which are the input signals of priority encoding logic, when there match signals of highest priority column there is only block miss signals within the column and within the block, a priority encoding logic of block hit or sponding to the CAM match signals of highest priority within the block and block binary address signal correlogic level "one" which is called hit or low logic level each CAM match signals or input signal has either high higher priority or from higher priority to lower priority. or input signals match signals within the block, the CAM match signals each block has same priority encoding logic of CAM each block has equal number of CAM match signals binary IS at least one column hit signal within address are arranged from lower priority to corresponding within the column, a 5 E e CAM Ē

SS

inverter

priority encoding(HAPE) logic of claim 1, further compris-Ņ signals of highest priority within the group column. A content address able memory(CAM) and hit ahead Ś

:Bur a block multiplexer to select the binary address from the block of highest priority hit within the column as less significant portion of the column binary address; and

priority encoding logic of block hit signals to generate the block multiplexer control signal which select the block of highest priority hit within the column, and a binary ority binary address. the more significant portion of the column highest priaddress encoding logic of block hit signals to generate 5 5

block comprises: priority encoding(HAPE) logic of claim 1, wherein each ω A content address able memory(CAM) and hit ahead

a group of sub-blocks, each sub-block has equal number of binary address encoding logic to highest priority binary address as pendently before sub-block binary address; and the sub-block hit or miss signal is generated indegenerating logic to generate sub-block hit or miss signal, input signals, each sub-block has priority encoding and generate sub-block well as hit or miss N 20

a block hit or miss generating logic to generate block hit or miss signal and block hit or miss signal is generated ated independently before the block binary address is gener-

ھ sub-block multiplexer to select the binary address from significant portion of block binary address; and the highest priority sub-block within the block as less

22 priority encoding logic of each sub-block hit signals to generate the control signal of sub-block multiplexer, and a binary address encoding logic of each sub-block hit signals to generate the more significant portion of block binary address. ш

the logic circuit of same structure. priority encoding(HAPE) logic of claim 3, wherein priority encoding logic, address encoding logic and multiplexer have 4 A content addressable memory(CAM) and hit ahead

\$

generating logic, priority encoding logic, address encoding logic and multiplexer have dynamic NOR logic. priority encoding(HAPE) logic of claim 4, wherein the hit 5. A content address able memory(CAM) and hit ahead £

same time that the less significant portion of the highest of controlling the multiplexer is generated before or in the priority encoding(HAPE) logic of claim 2, wherein the signal 6. A content address able memory(CAM) and hit ahead

S

priority local address is generated. 7. A content addressable memory (CAM) and hit ahead priority encoding (HAPE) logic, comprising:

a group of blocks which are arranged in columns and rows, high the block or a block miss signal when all the CAM match CAM match signal that is a high logic level "one" within to generate a block hit signal when there is at least one each CAM match signal or input signal being either a higher priority or from higher priority to lower priority, signals or input signals arranged from lower priority to nals which are the input signals of priority encoding logic, each block having a same priority encoding logic of CAM match signals within the block, the CAM match signals are a low logic level high logic level "one which is called hit or a low logic level "zero" which is called miss, each block configured each block having an equal number of CAM match sig-"zero " within the block and ŝ 8 S

00

2 2 a block binary address signal corresponding to the CAM match signals of highest priority within the block; priority encoding logic of block hit or miss signals of each priority encoding logic of column hit or miss signals of a group column binary address corresponding to the CAM only column miss signals within the group column and a within the group column or a miss signal when there are group column, the group column configured to generate a hit signal when there is at least one column hit signal column binary address corresponding to the CAM hit signal when there is at least one block hit signal match signals of highest priority within the column; and are only within the column or a column miss signal when there column, each column configured to generate a column block miss signals within the column and

8. The content addressable memory (CAM) and hit ahead priority encoding (HAPE) logic of claim 7, further comprisumn.

match signals of highest priority within the group col-

- ing: a block multiplexer configured to select a binary address address, column as a less significant portion of the column binary from the block having the highest priority hit within the

- the priority encoding logic of block hit signals being con-figured to generate a block multiplexer control signal for selecting the block having the highest priority hit within the column; and

- 9 binary address encoding logic of block hit signals con figured to generate a more significant portion of column binary address. ine

ы

block comprises: priority encoding (HAPE) logic of claim 7, wherein each 9. The content addressable memory (CAM) and hit ahead

- ۵ fo dnoug as well as hit or miss generating logic configured to generate a sub-block hit or miss signal, the sub-block hit or miss signal being generated independently before the encoding and binary address encoding logic configured sub-block binary address; to generate a sub-block highest priority binary address number of input signals, each sub-block having priority 'sub-blocks, each sub-block having an equal

- ۵ block hit or miss generating logic configured to generate a block hit or miss signal, the block hit or miss signal being generated independently before the block binary

- 2 address is generated; sub-block multiplexe address; and block as a less significant portion of the block binary address from a highest priority sub-block within multiplexer configured to select a binary the

- ۵ priority encoding logic of each sub-block hit signals configured to generate a control signal of the sub-block

- multiplexer; and a binary address encoding logic of the sub-block hit signals block binary address. configured to generate a more significant portion of the

multiplexer have logic circuitry of the same structure. priority encoding (HAPE) logic of claim 9, wherein the pri-ority encoding logic, the address encoding logic, and the 10. The content addressable memory (CAM) and hit aheaa

priority encoding (HAPE) logic of claim 8, wherein a signal for controlling the multiplexer is generated before or at the priority encoding (HAPE) logic of claim 10, wherein the hit encoding logic, and the multiplexer have dynamic NOR logic generating logic, the priority encoding logic, 12. The content addressable memory (CAM) and hit ahead 11. The content addressable memory (CAM) and hit ahead multiplexer is generated before or the address

6

prising: priority local address is generated. same time that the less significant portion of the highest 13. A content addressable memory (CAM) system, com-

one 8 segments, at least one of the circuit segments configured inputs received by the at least one of the circuit segments whether at least one of a plurality of circuit segment or more columns comprising a plurality of circuit generate a fust circuit segment output based on

R or more of a plurality of second input signals. in response to a first input signal, and to subsequently change the node to a fourth logic level in response to one generate first address information based on a selected corresponds to a first logic level, to a second logic level, to set a node to a third logic level one of the first circuit segment outputs that corresponds least one of the one or more columns configured to IJ 10

segment output represents circuit segment hit information. 14. The CAM system of claim 13, wherein the first circuit

information. of the plurality of circuit segment inputs represents match 15. The CAM system of claim 13, wherein the at least one

20

ond logic level the first circuit segment outputs that corresponds to the secof the first circuit segment outputs is a highest priority one of 16. The CAM system of claim 13, wherein the selected one 2

17. The CAM system of claim 13, wherein:

rality of columns and a plurality of rows. 18. The CAM system of claim 13, wherein: the one or more columns are a plurality of columns, and the plurality of circuit segments are arranged in the plu-

30

the one or more columns are a group of columns;

each column in the group configured to generate a column least one of the circuit segments; output based on the first circuit segment output of the at . and ŝ

the group configured to generate second address informacorresponds to a fifth logic leve tion based on a selected one of the column outputs that

19. The CAM system of claim 13, wherein: the at least one of the one or more columns is configured to pre-charge the node in response to the first input signal; ana \$

the at least one of the one or more columns is configured to subsequently discharge the node in response to the one 45

or more of the plurality of second input signals. 20. The CAM system of claim 13, wherein the first input signal is configurable independently of the one or more of the plurality of second input signals.

level and the second logic level are the same logic level. 22. The CAM system of claim 13, wherein the one or more 21. The CAM system of claim 13, wherein the first logic 20

columns comprise: a first logic circuit configured to generate a first logic circuit output based on the selected one of the first circuit segment outputs that corresponds to the second logic SS

second logic circuit configured to generate a second logic circuit output based on whether the first circuit segment level

third logic circuit configured to generate the first address segment outputs level information based on the selected one of the first circuit output corresponds to the second logic level; and that corresponds to the second logic 8

first logic circuit, the second logic circuit, and the third logic circuit is configured to set the node to the third logic level in response to 23. The CAM system of claim 22, wherein at least one of the the first input signal, and to subsequently change ŝ

10

more of the plurality of second input signals. the node to the fourth logic level in response to the one 9

24. The CAM system of claim 22, wherein:

the at least one of the circuit segments is configured to second address information; and generate a second circuit segment output representing

Ś

the one or more columns further comprise:

a fourth logic circuit configured to select one of the second circuit segment outputs as a less significant

portion of the first address information; and a fifth logic circuit configured to generate a more significant portion of the first address information.

fourth logic circuit and the fifth logic circuit is configured to second input signals. logic level in response to the one or more of the plurality of signal, and to subsequently change the node to the fourth set the node to the third logic level in response to the first input 25. The CAM system of claim 24, wherein at least one of the

claim 24, wherein the one or more columns are each configoutput is generated. before or at the same time when the second circuit segment ured to generate a control input for the third logic circuit 26. The content addressable memory (CAM) system of

claim 22, wherein: 27. The content addressable memory (CAM) system of

the plurality of circuit segment inputs is divided into a plurality of subsets of the circuit segment inputs; and

the first logic circuit comprises: a plurality of fourth logic circuits each configured to generate a fourth logic circuit output level; and circuit segment inputs corresponds to the first logic whether at least one of a corresponding subset of the based 20

a fifth logic circuit configured to generate the first circuit segment output based on whether at least one of the logic level. fourth logic circuit outputs corresponds to the first

28. The CAM system of claim 27, wherein:

at least one of the fourth logic circuit and the fifth logic circuit is configured to set the node to the third logic level in response to the first input signal, and to subsequently ana the one or more of the plurality of second input signals; change the node to the fourth logic level in response to

the fourth logic circuit output is an input to the fifth logic circuit.

prising: 29. A content addressable memory (CAM) system, com-

a circuit segment configured to generate a circuit segment circuit segment inputs received by the circuit segment output based on whether at least one of a plurality of

corresponds to a first logic level, the circuit segment configured to set a node to a second quently change the node to a third logic level in response logic level in response to an input signal, and to subseto the plurality of circuit segment inputs,

the circuit segment output corresponding to said third logic level

plurality of circuit segment inputs corresponds to a match line 30. The CAM system of claim 29, wherein at least one of the

output. 31. The CAM system of claim 29, wherein the circuit seg-

plurality of circuit segment inputs represents match informa ment output represents circuit segment hit information. 32. The CAM system of claim 29, wherein at least one of the

tion.

#### 11

33. The CAM system of claim 29, wherein: the circuit segment is configured to pre-charge the node in response to the input signal; and the circuit segment is configured to subsequently discharge the node in response to the plurality of circuit segment

Ś

inputs. 34. The CAM system of claim 29, wherein the input signal is configurable independently of the plurality of circuit seg-ment inputs. 35. The CAM system of claim 29, wherein the first logic 10 level and the third logic level are the same logic level. 36. The CAM system of claim 29, wherein the circuit seg-ment is a first circuit segment, and further comprising a second circuit segment configured to generate address infor-mation based on the circuit segment output.

\*

\*

\*

.

# Exhibit X1

# Plaintiff's infringement analysis prior to file complaint

US patent RE45259. embedded RRAM IP offering to sell, TetraMem's RRAM has read the claim 29 of developed the multi-level resistance state resistor storage element and designed Based on the information in Exhibit 1 and public information TetraMem has

showed me their test chip manufactured and the measurement result. the use of ADC (analog to digital circuit design) to read the multi-level resistance their multi-state resistance value resistor storage element has the best quality and ADC and memory read circuit design capability, they have designed. the test chip value of the resistor. The CEO of TetraMem told me that TetraMem has very good with their multi-level resistance value resistor and ADC. The CEO of TetraMem linearity. The CEO of TetraMem introduced to me their RRAM circuit design and value resistor storage is not something new, the CEO of TetraMem told me that with multi-state resistance value resistor storage element. Multi-state resistance In the year of 2000 the CEO of TetraMem introduced their RRAM (ReRAM)

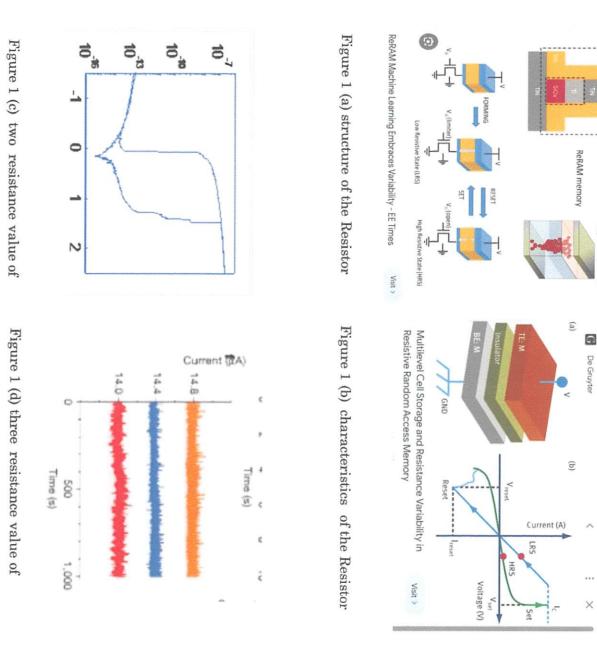

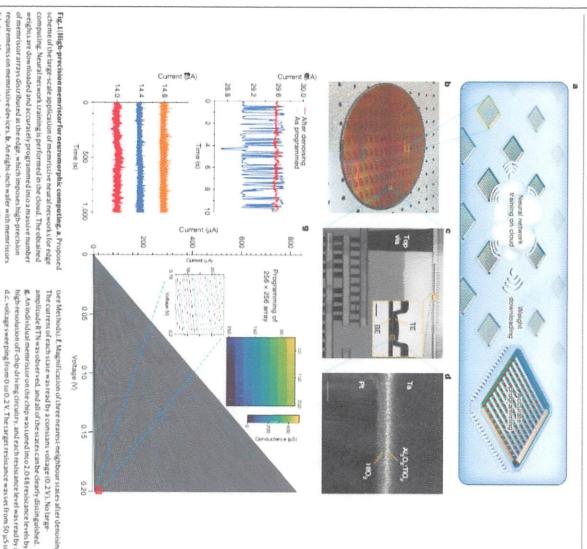

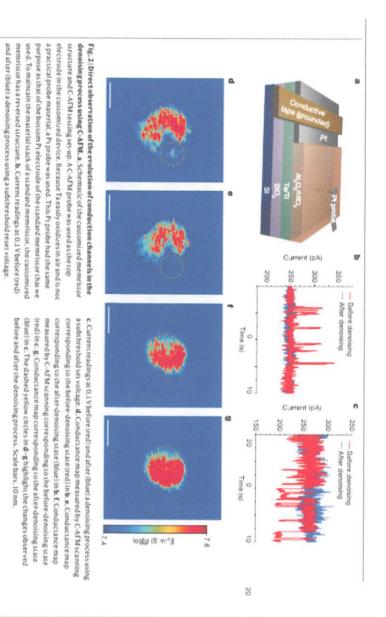

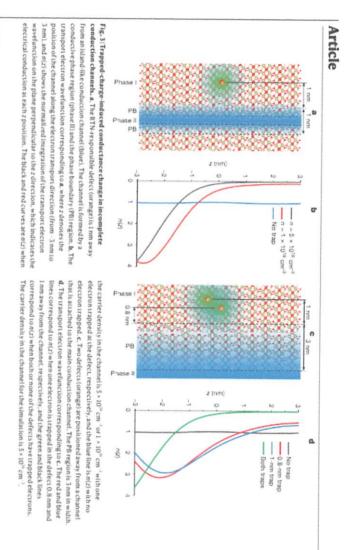

three resistance value in the multi-state-value resistor of TetraMem in Exhibit 2. transfer diagram curve when applying current and voltage to the resistor. Figure resistance random accessible memory (RRAM). Figure 1(b) is the resistance state be used to record and store the data and information. This is the basic principle of the resistor to conduct with different resistance values. the value of the resistor can electrodes, some special isolate material and some special metal electrode can make 1(c) is the two resistance value of the two state-value resistor. Figure 1(d) is the the structure of the resistor, it is an isolator material sandwiched with two metal with the different states of the resistor to store the binary data. Figure 1(a) shows The following Figure1 is the basic of RRAM (ReRAM) which is an memory

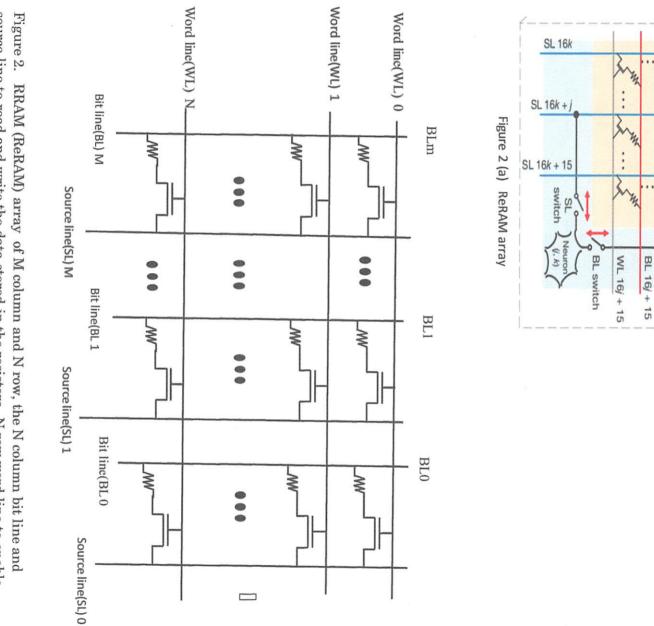

Figure 2 is the array of resistance memory schematic (RRAM)

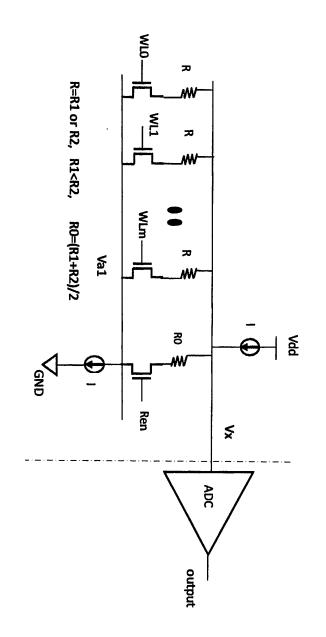

resistance value of resistor storage element in TrtraRam Figure 3 shows the major part of read circuit of RRAM with multi-state

the two level Resistor

the multi-level Resistor of TetraMem in Exhibit 2

element used in the RRAM (ReRAM)

co

reading and writing of the data stored in the resistors. source line to read and write the data stored in the resistors, N row word line to enable

..

.

:

WL 16j

BL 16*j* + *k* WL 16*j* + *k*  BL 16j

Figure 3 The read circuit of RRAM of TetraMem

2, it was turned with 90 degree. The left side of the dot line is the reading circuit Figure 3 is the circuit of reading one column in the RRAM( ReRAM ) in Figure

resistors an ADC ( analog signal to digital signal converter) is used. line. But for the TetraMem's RRAM (ReRAM) using multi-level resistance of two level resistance usually use an amplifier on the right side of the vertical dot of the RRAM(ReRAM) used in the available RRAM. For RRAM of resistors with

When starting reading,

transistor, R0, and two current source I. controlled by "Ren" signal is On, the node Vx is set to voltage V0 through the N Step 1: Switch read enable signal "Ren" signal to V-read, the N transistor

element controlled by WL0, each bit voltage of ADC's output reflects the value of V2, resistance of resistor storage element, the voltage of Vx will change to one of V1, connected to the transistor controlled by WLO, in the RRAM having multi-level transistor of WL0 is ON and transistor of Ren is OFF: in the RRAM with two Vx which corresponds to the information of the resistance value being read. V1 or V2 which corresponds to the resistance state of the resistor storage element level resistance of the resistor storage element, the voltage of Vx will change to low voltage to high voltage and switch Ren from high voltage to low voltage, the Step2 V3 ..... which corresponds to the resistance state of the resistor storage If read the data controlled by WL0, simultaneously switch WL0 from

RRAM of TetraMem " of Figure 1. Claim chart of Claim 29 of US Patent RE45259 read "The read circuit of

| This claim section read the schematic in Figure 3 because the generating output of the read circuit is                                                                                                                                                                                                                               |                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| vx will change to one of v1, v2, v3 which<br>corresponds to the resistance state of the resistor<br>storage element controlled by WL0, each bit voltage<br>of ADC's output reflects the value of Vx which<br>corresponds to the information of the resistance<br>value being read.                                                   |                                                                                                                           |

| voltage and switch Ren from high voltage to low<br>voltage, the transistor of WL0 is ON and transistor<br>of Ren is OFF: in the RRAM having multi-level<br>resistance of resistor storage element, the voltage of                                                                                                                    | circuit segment<br>corresponds to a first<br>logic level,                                                                 |

| Step 1: Switch read enable signal "Ren" signal to<br>V-read, the N transistor controlled by "Ren" signal<br>is On, the <b>node Vx is set to voltage V</b> <sup>0</sup> through the<br>N transistor, R0, and two current source I.<br>Step2 If read the data controlled by WL0,<br>simultaneously switch WL0 from low voltage to high | circuit segment output<br>based on whether at<br>least one of a plurality<br>of circuit segment<br>inputs received by the |

| The read operation of RRAM of TetraMem in<br>Figure 3 is explained in page 5, cited as follows:                                                                                                                                                                                                                                      | comprising:<br>(1) a circuit segment<br>configured to generate a                                                          |

| This is preamble                                                                                                                                                                                                                                                                                                                     | A content addressable<br>memory (CAM) system,                                                                             |

| This claim 29 reads on schematic of "the read circuit<br>of RRAM of TetraMem" in FIG.3                                                                                                                                                                                                                                               | Claim 29 <i>of</i> US patent<br>RE45259                                                                                   |

| Accused device: RRAM IP which TetraMem has been<br>developing and offering to sell. RRAM IP which<br>TetraMem have the read circuit shown in Figure 3                                                                                                                                                                                | claim                                                                                                                     |

| lity in de                                                                                                                                                           | the resistance value being read.                                                                  |                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------|

| lity in de                                                                                                                                                           | value of Vx which corresponds to the information of                                               | third logic level.         |

| nent<br>a node<br>evel in<br>o a<br>urality                                                                                                                          | state of the resistor storage element controlled by                                               | corresponding to said      |

| nent<br>node<br>evel in<br>o a<br>urality                                                                                                                            | V2, V3 which corresponds to the resistance                                                        | segment output             |

| nent<br>node<br>evel in<br>o a<br>urality                                                                                                                            | element, the voltage of Vx will change to one of V1,                                              | inputs, the circuit        |

| nent<br>node<br>evel in<br>o a<br>ut<br>urality                                                                                                                      | ON and transistor of Ken is OFF: in the KKAM<br>having multi-level resistance of resistor storage | of circuit segment         |

| H OC II<br>H OC II                                                                                                                                                   | high voltage to low voltage, the transistor of WL0 is                                             | response to the pitramty   |

| ji ode nt<br>in                                                                                                                                                      | low voltage to high voltage and switch Ren from                                                   |                            |

| L od nt<br>H de t                                                                                                                                                    | Ren, subsequently simultaneously switch WL0 from                                                  | third logic level in       |

| uit segment<br>to set a node<br>logic level in<br>an input<br>quently                                                                                                | after (in step 1) node $V_x$ was set to voltage $V_0$ by                                          | change the node to a       |

| uit segment<br>to set a node<br>logic level in<br>an input                                                                                                           | (3) This section claim read step 2.                                                               | (3) to subsequently        |

| uit segment<br>to set a node<br>logic level in<br>an input                                                                                                           | input voltage of Ken.                                                                             |                            |

| uit segment<br>to set a node<br>logic level in<br>an input                                                                                                           | THE TO STATES OF TIONS AN IS SEE DESCRIPTION                                                      |                            |

| uit segment<br>to set a node<br>logic level in<br>an input                                                                                                           | Figure 3 voltage of node Vy is set based on the                                                   |                            |

| uit segment<br>to set a node<br>logic level in<br>an input                                                                                                           | This section claim read the RRAM of TetraMem in                                                   |                            |

| uit segment<br>to set a node<br>logic level in<br>an input                                                                                                           | N transistor, R0, and two current source I.                                                       |                            |

| J in                                                                                                                                                                 | is On, the node Vx is set to voltage V <sub>0</sub> through the                                   | signal, and                |

|                                                                                                                                                                      | V-read, the N transistor controlled by "Ren" signal                                               | response to an input       |

|                                                                                                                                                                      | Step 1: Switch read enable signal "Ren" signal to                                                 | to a second logic level in |

|                                                                                                                                                                      | Figure 3 is explained in page 5, cited as follows:                                                | configured to set a node   |

| its voltage level from low to high and switch on the<br>controlled transistor and read the connected<br>( controlled) resistance and generate the output<br>voltage. |                                                                                                   | (2) the circuit segment    |

| its voltage level from low to high and switch on the<br>controlled transistor and read the connected<br>( controlled) resistance and generate the output             | voltage.                                                                                          |                            |

| its voltage level from low to high and switch on the<br>controlled transistor and read the connected                                                                 | ( controlled) resistance and generate the output                                                  |                            |

| its voltage level from low to high and switch on the                                                                                                                 | controlled transistor and read the connected                                                      |                            |

| based off at reast offe of WILD, WILL,, WILH CHARDE                                                                                                                  | its voltage level from low to high and switch on the                                              |                            |

| hased on at least one of WTO WT 1 WT m change                                                                                                                        | based on at least one of WL0, WL1,, WLm change                                                    |                            |

### Exhibit 1

TetraMem prior to complaint as well as the information of Plaintiff's knowledge and effort to discussion

ADC and memory read circuit design capability, they have designed. the test chip value of the resistor. linearity. The CEO of TetraMem introduced to me their RRAM circuit design and suitable to be used in the AI or in memory computing. Multi-state resistance value showed me their test chip manufactured and the measurement result with their multi-level resistance value resistor and ADC. The CEO of TetraMem the use of ADC (analog to digital circuit design) to read the multi-level resistance multi-state resistance value resistor storage element has the best quality and resistor storage is not something new, the CEO of TetraMem told me that their "state 1" through applying different voltage and current on it, which is more Ge, multi-resistance levels storing multi-states data rather than only "state 0" and resistance level of storage resistor, one level is at low resistance storing "state 1" Market , The storage resistor used in the TetraMem's RMAM can be programed to and the other level is at high resistance storing "state 0", used in the RRAM in the patented RRAM technology which TetraMem used. Comparing with the two the CEO of TetraMem, Inc. at TetraMem's office. Around February 1,2020, I was referred by some one to meet Dr. Glenn (Ning) The CEO of TetraMem told me that TetraMem has very good Dr. Glenn Ge explained the

of storage resistor competitive value of his company as a start-up is its patented multi-level resistance designers and design capability. resistor memory company, his company is also a chip company with circuit and logic Dr. Ge said that his company has more value because his company is not only a I said to Dr. Glenn Ge that the unique

5 Glenn (Ning) Ge, the CEO of TetraRam On September 9, 2023 I sent the following message through LinkedIn network

# LinkedIn Member 2nd

Paul Huang • 9;44 PM Hi Dr. Ge,

How are you. I am writing to you to notify that I found that your company product RERAM read the claim 29 of US patent No. RE45259 which is attached here. The detail analysis would be provided upon you intend to resolve the disputes out of the Court. looking forward to hearing from you. my email address is : paulhuang03@outlook.com Best Regards Paul Huang RE45259.pdf

SEP 10

LinkedIn Member • 10:25 PM

I don't know why you bring up this, but 1) We even don't have a production yet; 2) Our technology is not related to your claim, esp. claim 29 of CAM

message through LinkedIn network On September 10, Glenn(Ning) Ge CEO of TetraRam replied me the above

and can only view him as LinkedLn Member In the same time he dragged me into black name list and I can not see his name

On September 21, 2023 I called Ning Ge, he did not answer my call.

person and chat. Thank You. Paul". He did not reply. On September 21, I sent Ning Ge a text message: "Hi Dr.Ge, May we meet in

On October 11,2023 I sent Mr. Ning (Glen) Ge a text message in Chinese :

special place and moment. this to you with very good wishes. Maybe "sesame open the door" is valuable at design etc. can be purchased or developed through hiring regular engineers." I said developed, the other stuff such as phase lock loop and analog to digital converter most value technology of your company is the technology of resistor your company Hi Dr, Ge, Three years ago We met each other, at that time I said to you:" the

Dr. Ge still did not reply my request.

and joint development offering. The following content is the public release on the RRAM information, offering

### Analog In-Memory Computing Development of Groundbreaking AI Accelerator Chips with TetraMem and Synopsys Collaborate to Accelerate

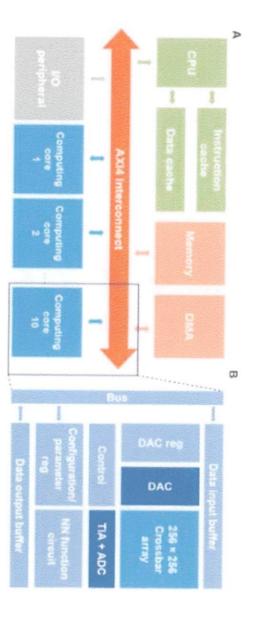

~Dr. Glenn (Ning) Ge, CEO & Cofounder, TetraMem Inc. infrastructure resources, we can tape out quickly and efficiently." sites. Synopsys Cloud has played a pivotal role in helping us accomplish our mission by reliable, robust, and flexible engineering tools and collaboration across global working 5 With scalable access to EDA software, pre-configured end-to-end flows, and providing seamless access to a highly secure and complete SoC design environment. new possibilities for AI everywhere. Designing for a radically different system requires human brain, changes the paradigm of how AI computations are performed, launching TetraMem's analog-RRAM-based in-memory computing technology, inspired by the

:

success-story.pdf https://www.synopsys.com/content/dam/synopsys/cloud/success-story/tetramem-Read the full Success Story at

" TetraMem's analog-RRAM-based in-memory computing technology, inspired by quickly and efficiently." pre-configured end-to-end flows, and infrastructure resources, we can tape out complete SoC design environment. With scalable access to EDA software, us accomplish our mission by providing seamless access to a highly secure and across global working sites. Synopsys Cloud has played a pivotal role in helping system requires reliable, robust, and flexible engineering tools and collaboration the human brain, changes the paradigm of how AI computations are performed, launching new possibilities for AI everywhere. Designing for a radically different

~Dr. Glenn (Ning) Ge, CEO & Cofounder, TetraMem Inc.

TetraMem

#### Business

tanging from proprietory computing memory devices to nove computing and electures liteam invite at t<mark>etramem.com</mark> and follow featured in the March 30, 2003 edition of Nature. Our team brings together complett entary skill sets and technological know how bridensty muthexe. ARAM taria computing memoratori hased acceletation is commencial foundries. memory computing (MC) technology for efficient Arispotications. Tetra Marrillo the world's only company to produce a high TetraMem too a USbased company founded in Silicon Valley in 2018 is posed to deliver the industry's most disruptive us us on LinkedIn The technicity was

#### Challenges

- Having a global team scread acrocy continents requires a seamleds, unded mixed signal SoC design environment for efficient collationation

- CAO setup. flows and on-demand coalable and elastic (Treseurces are needed

- The All accelerator's complex design records smooth integration and ventication of analog in memory computing and the dig tal RISUV processor with orbical time to market targets

### Exhibit **@**

### TetraMem about TetraMem The public information claimed by and its products

### Dr. Glenn NingGe, CEO

widely embracing these innovations, but not without their share of challenges. cities, and cybersecurity industries Healthcare, autonomous vehicles, smart bringing revolutions to various industries the AI computing hardware realm Recent breakthroughs in data algorithms have ignited transformat tation in and are

processing and memory unit leads to As Dr. Glenn Ning Ge, CEO of TetraMem says, "Relying on traditional computing methodologies involving separate applications, which can result in reduced iggravated by the surge in data-cent applications significant time and energy moving data ron Neumann bottlenecks and memory ralls, where the system spends ethodologies putation capabilities." the matrix-based This issue involving deep-learning is further separate

field.

Suida

≥ networks, require massive Wer models, particularly for vector-matrix deep multiplication neural

applications. Now, the

IMC using TetraMem's hardware SDK software, giving them development and research of analog Academic and industry partners and researchers are exploring the earlystage transform how Al models are used customers to test its capabilities, the chipset is a gateway for numerous opportunity to delve into this em groundbreaking TetraMem® MX100 SoC (system times Currently delivered as chipset consumes edge devices. Given its architecture, the in-memory computing chip is designed to accelerate AI algorithms, particularly for analog in-memory computing chip, IP and customizable design solutions, and its TetraMem ingrains all these features into chip), an evaluation kit designed software toolkit and support. This analog suite of solutions, comprising and provides faster processing giving innovations significantly them the less that the for 3 75 8

of Business

ecosystem when we have a chance to re-design the new AI computing system, from materials and devices to algorithms and with emerging devices" consider the entire Al computing hardware—it's a six-dimension co-design and co-optimization," says Dr. Ge. "We "Our platform isn't just about the erging computing paradigm meets software, ensuring optimized ince across the board where the 타

> master's degrees including a MBA from The University of Michigan Ross School Dr. Ge himself holds a PhD and three innovation and excellence ensures that it does not just meet, but exceeds client A comprehensive solutions, and a client centric approach sets TetraMem apart and partner expectations. For instance. The blend of unway aring commit deep expe nent

innovation, guaranteeing we're laurels is not an option. We encourage a culture of continuous learning and 'The tech landscape is fast ahead of the curve," says Dr. Ge. everevolving, and resting on always one's and

processing and memory unit leads to von Neumann traditional computing methodologies memory walls, where for the matrix-based significant time and energy moving data the system spends involving separate bottlenecks and deep-learning

### Share this Article N Post Share O Share

#### Company TetraMem

Management Dr. Glenn NingGe, CEO