# IN THE UNITED STATES DISTRICT COURT FOR THE WESTERN DISTRICT OF TEXAS MIDLAND-ODESSA DIVISION

POLARIS INNOVATIONS LIMITED, a Delaware Corporation,

Plaintiff

CIVIL ACTION NO. 7:24-cv-00296

v.

QUALCOMM INCORPORATED and QUALCOMM TECHNOLOGIES, INC., both Delaware Corporations, JURY TRIAL DEMANDED

Defendants

# PLAINTIFF'S COMPLAINT FOR PATENT INFRINGEMENT

Plaintiff Polaris Innovations Limited ("Polaris") files this Complaint against Defendants Qualcomm Incorporated and Qualcomm Technologies, Inc. (together, "Qualcomm" or "Defendants") for infringement of U.S. Patent No. 7,184,339 (the "339 Patent"); U.S. Patent No. 7,499,371 (the "371 Patent"); U.S. Patent No. 7,872,936 ("the '936 Patent"); and U.S. Patent No. 8,161,344 (the "344 Patent"), collectively, the "Asserted Patents."

# THE PARTIES

1. Polaris Innovations Limited is a corporation organized and existing under the laws of Ireland, with its principal place of business at 77 Lower Camden Street, Dublin D02 XE80, Ireland.

2. Defendant Qualcomm Incorporated ("QCI") is a corporation organized and existing under the laws of Delaware and maintains established places of business at 9600 N. Mopac, Suite 900, Stonebridge Plaza II, Austin, Texas 78759 and 13929 Center Lake Drive, Parmer Building 1 Austin, Texas 78753. QCI may be served in Texas via its registered agent Prentice Hall Corp. System, 211 E. 7th Street, Suite 620, Austin, TX 78701-3218.

#### Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 2 of 52

3. Defendant Qualcomm Technologies, Inc. ("QTI") is a corporation organized and existing under the laws of Delaware and maintains established places of business at 9600 N. Mopac, Suite 900, Stonebridge Plaza II, Austin, Texas 78759 and 13929 Center Lake Drive, Parmer Building 1, Austin, Texas 78753. QTI may be served in Texas via its registered agent Corporation Service Company d/b/a CSC-Lawyers Incorporating Service Company, 211 E. 7th Street, Suite 620, Austin, TX 78701.

4. QTI is a wholly-owned subsidiary of QCI and, together with its affiliates, serves and performs substantially all of Qualcomm's research and development efforts, its engineering operations, and its products and services businesses. *See* <u>https://www.qualcomm.com/company</u>. Relevant QTI-affiliated companies include, at least, Qualcomm CDMA Technologies and Qualcomm CDMA Technologies Asia Pacific Pte. Ltd.

5. Qualcomm is one of the world's premier manufacturers of integrated circuits for the wireless device industry. Its website states that "[r]eferences to 'Qualcomm' may mean Qualcomm Incorporated, or subsidiaries or business units within the Qualcomm corporate structure, as applicable." *Id.* Qualcomm's website further states that "Qualcomm Technologies, Inc., a subsidiary of Qualcomm Incorporated, operates, along with its subsidiaries, substantially all of our engineering, research and development functions, and substantially all of our products and services businesses, including our QCT semiconductor business." *Id.*

6. QCI, QTI, and their subsidiaries and related companies share the same management, common ownership, advertising platforms, facilities, distribution and sales channels, and accused products and product lines. In this way, QCI, QTI, and their subsidiaries and related companies operate as a singular, unitary business enterprise and are, thus, jointly, severally and communally liable for the acts of patent infringement detailed below.

7. QCI, QTI, and their subsidiaries and related companies are doing business collectively, directly and through agents, on a persistent and ongoing basis in this District and elsewhere in the United States, and they each have regular and established places of business here.

## JURISDICTION AND VENUE

This is an action for patent infringement arising under the patent laws of the United

States, 35 U.S.C. §§ 1, et seq. This Court has jurisdiction over this action pursuant to 28 U.S.C. §§

1331 and 1338(a).

9. This Court has personal jurisdiction over Qualcomm because it has engaged, and continues to engage, in continuous, systematic, and substantial activities within this State, including the substantial marketing and sale of products and services within this State and this District. Indeed, this Court has personal jurisdiction over Qualcomm because it has committed acts giving rise to Polaris' claims for patent infringement within and directed to this District, has derived substantial revenue from its goods and services provided to individuals and entities in this State and this District, and maintains regular and established places of business in this District, including at least its two brick-and-mortar locations in Austin, Texas:<sup>1</sup>

|                   | 🕷 / Company / Offices     |                                 |

|-------------------|---------------------------|---------------------------------|

| USA · All reg     | ions  V All localities  V | ices ? Headquarters ?           |

|                   |                           |                                 |

| 73 Offices in US/ |                           | 0                               |

| 73 Offices in USA | A<br>© once<br>Austin     | . ♥ <sub>Office</sub><br>Austin |

<sup>&</sup>lt;sup>1</sup> See https://www.qualcomm.com/company/facilities/offices?country=USA&page=2.

## Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 4 of 52

10. Relative to patent infringement, Qualcomm has committed and continues to commit acts in violation of 35 U.S.C. § 271, and has made, used, offered for sale, sold, and imported infringing products, systems, and services in this State, including this District, and has otherwise engaged in infringing conduct within and directed at, or from, this District. Infringing products, systems, and services (collectively, the "Accused Instrumentalities") include Qualcomm processors such as the Qualcomm Snapdragon 4, 6, 7, 8, and X Series products and other processors and platforms offered and sold by Qualcomm as described further below.

11. Qualcomm's infringing activities have caused harm to Polaris in this District. Qualcomm and/or its partners and agents offer to sell and sell the Accused Instrumentalities within this District, and on information and belief, Qualcomm, its partners and agents, and/or their customers use the Accused Instrumentalities in this District in infringing ways. These are purposeful acts and transactions in this State and this District such that Qualcomm reasonably should know and expect that it can be haled into this Court to answer for its actions.

12. Moreover, this Court maintains personal jurisdiction over Qualcomm because Qualcomm conducts business in this State by, among other things, "recruit[ing] Texas residents, directly or through an intermediary located in this State, for employment inside or outside this State." Tex. Civ. Prac. & Rem. Code § 17.042(3). For instance, Qualcomm lists dozens of job openings in Texas (as of Oct. 29, 2024):<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> https://careers.qualcomm.com/careers?location=Austin%2C%20Texas%2C%20United%20 States%20of%20America&pid=446697682796&domain=qualcomm.com&sort\_by=relevance&l ocation\_distance\_km=8&triggerGoButton=true

| obs at Qualcomm                            |                              |                           |           |                |                               |  |

|--------------------------------------------|------------------------------|---------------------------|-----------|----------------|-------------------------------|--|

| rior to uploading your resume, please ensu | e your location is included. |                           |           |                |                               |  |

|                                            |                              |                           |           |                |                               |  |

| Search                                     | Q Austin, Texas, United      | d States of America 💿 × 5 | ▼ mi ▼ Go | ) 🛛 🖓 Job Cart | Advanced Options $\checkmark$ |  |

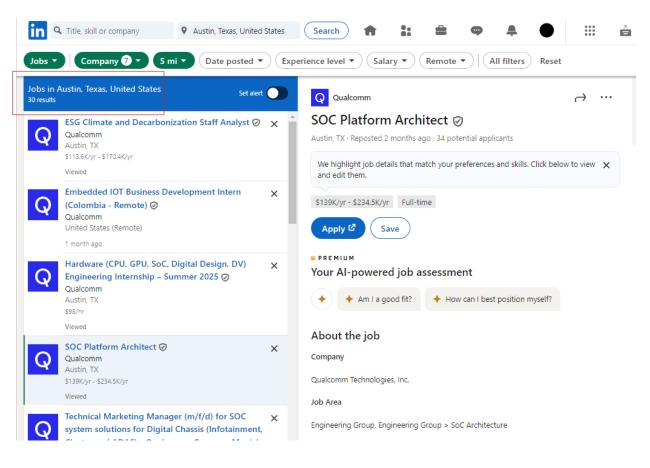

# 13. Qualcomm also lists its job openings in Texas on LinkedIn (as of Oct. 24, 2024):<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>https://www.linkedin.com/jobs/search/?currentJobId=3991694727&distance=5&f\_C=2017%2C 154985%2C162572%2C2923434%2C38387%2C595224%2C75115234&f\_CR=103644278&ge oId=104472865&origin=JOB\_SEARCH\_PAGE\_JOB\_FILTER&refresh=true&sortBy=R

14. Further, on Qualcomm's LinkedIn page, it boasts 603 "associated members" in its Texas offices (as of Oct. 24, 2024):<sup>4</sup>

| Q Engine                                                                                                                                                                                                                                                                                                                                                            | LICCONNA<br>ering Human Progress                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| munications - San Diego, CA - 2M followers - 1<br>Follow Contact us 🖉                                                                                                                                                                                                                                                                                               | IOK+ employees                                                                                                                                                                                                                                                                                                                                                                                                                            |

| About Posts Jobs Life                                                                                                                                                                                                                                                                                                                                               | People Insights                                                                                                                                                                                                                                                                                                                                                                                                                           |

| associated members                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| s, United States × Clear all                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Q. Search<br>Qualcomm                                                                                                                                                                                                                                                                                                                                               | Home My Network Jobs                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Qualcomm<br>ome About Posts Jobs                                                                                                                                                                                                                                                                                                                                    | Home My Network Jobs                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Qualcomm<br>Ome About Posts Jobs<br>10,244   San Diego, CA                                                                                                                                                                                                                                                                                                          | Home My Network Jobs Life People Insights 21   The University of Texas at Dallas                                                                                                                                                                                                                                                                                                                                                          |

| Qualcomm<br>ome About Posts Jobs<br>10,244   San Diego, CA<br>6,734   Kamataka, India                                                                                                                                                                                                                                                                               | Home My Network Jobs                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Qualcomm       ome     About     Posts     Jobs       10.244   San Diego, CA       6,734   Karnataka, India       6,619   Greater Bengaluru Area                                                                                                                                                                                                                    | Home         My Network         Jobs           Life         People         Insights           21         The University of Texas at Dallas           21         Georgia Institute of Technology                                                                                                                                                                                                                                           |

| Qualcomm       ome     About     Posts     Jobs       10,244     San Diego, CA       6,734     Karnataka, India       6,619     Greater Bengaluru Area       6,337     Bengaluru                                                                                                                                                                                    | Home         My Network         Jobs           Life         People         Insights           21         The University of Texas at Dallas         21           21         Georgia Institute of Technology         15           15         Jawaharlal Nehru Technological University                                                                                                                                                      |

| Qualcomm                                                                                                                                                                                                                                                                                                                                                            | Home     My Network     Jobs       Life     People     Insights       21     The University of Texas at Dallas       21     Georgia Institute of Technology       15     Jawaharlal Nehru Technological University       13     The University of Texas at Arlington                                                                                                                                                                      |

| Qualcomm       Iome     About     Posts     Jobs       10,244     San Diego, CA       6,734     Karnataka, India       6,619     Greater Bengaluru Area       6,337     Bengaluru       5,907     Telangana, India                                                                                                                                                  | Home     My Network     Jobs       Life     People     Insights       21     The University of Texas at Dallas       21     Georgia Institute of Technology       15     Jawaharlal Nehru Technological University       13     The University of Texas at Arlington       10     Indian Institute of Technology, Madras                                                                                                                  |

| Qualcomm       Iome     About     Posts     Jobs       10,244      San Diego, CA       6,734      Karnataka, India       6,619      Greater Bengaluru Area       6,337      Bengaluru       5,907      Telangana, India       5,827      Greater Hyderabad Area                                                                                                     | Home     My Network     Jobs       Life     People     Insights       21     The University of Texas at Dallas       21     Georgia Institute of Technology       15     Jawaharlal Nehru Technological University       13     The University of Texas at Arlington       10     Indian Institute of Technology, Madras       9     Birla Institute of Technology and Science, Pil                                                       |

| Qualcomm       Iome     About     Posts     Jobs       10,244      San Diego, CA                                                                                                                                                                                                                                                                                    | Life People Insights<br>21   The University of Texas at Dallas<br>21   Georgia Institute of Technology<br>15   Jawaharlal Nehru Technological University<br>13   The University of Texas at Arlington<br>10   Indian Institute of Technology, Madras<br>9   Birla Institute of Technology and Science, Pil<br>8   University of Michigan                                                                                                  |

| Qualcomm       Iome     About     Posts     Jobs       10,244   San Diego, CA       6,734   Karnataka, India       6,737   Bengaluru       6,619   Greater Bengaluru Area       6,337   Bengaluru       5,907   Telangana, India       5,827   Greater Hyderabad Area       5,553   Hyderabad       2,118   San Francisco Bay Area       667   Uttar Pradesh, India | Home     My Network     Jobs       Life     People     Insights       21     [The University of Texas at Dallas       21     [Georgia Institute of Technology       15     [Jawaharlal Nehru Technological University]       13     [The University of Texas at Arlington]       10     Indian Institute of Technology, Madras       9     [Birla Institute of Technology and Science, Pil]       8     University of Southern California |

<sup>&</sup>lt;sup>4</sup> https://www.linkedin.com/company/qualcomm/people/?facetGeoRegion=102748797

#### Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 7 of 52

15. Venue is proper in this District under 28 U.S.C. §§ 1391 and 1400(b) because Qualcomm has at least two regular and established places of business in Austin, which is in this District. Venue is further proper in this District because Qualcomm has directly infringed and/or induced the infringements of others, including its customers, in this District by offering for sale and selling Accused Instrumentalities in this District, using Accused Instrumentalities in infringing ways in this District, and inducing infringing customer use of Accused Instrumentalities in this District.

## THE ASSERTED PATENTS

16. Polaris is the sole and exclusive owner of all right, title, and interest in the'339 Patent, the '371 Patent, the '936 Patent, and the '344 Patent and holds the exclusive right to take all actions necessary to enforce its rights in, and to, the Asserted Patents, including the filing of this patent infringement lawsuit. Polaris also has the right to recover all damages for past, present, and future infringements of the Asserted Patents and to seek injunctive relief as appropriate under the law.

17. The '339 Patent is titled, "Semi-conductor component, as well as a process for the in-or output of test data." The '339 Patent issued on February 27, 2007 and stems from U.S. Patent Application No. 11/253,807, which was filed on October 20, 2005.

18. The '371 Patent is titled "Semiconductor memory system with a variable and settable preamble f." The '371 Patent issued on March 3, 2009 and stems from U.S. Patent Application 11/288,941, which was filed on November 28, 2005.

19. The '936 Patent is titled "System and method for packaged memory." The '936 Patent issued January 18, 2011 and stems from U.S. Patent Application No. 12/212,400 which was filed on September 17, 2008.

7

#### Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 8 of 52

20. The '344 Patent is titled "Circuits and methods for error coding data blocks." The '344 Patent issued April 17, 2012 and stems from U.S. Patent Application No. 12/046,099 which was filed on March 11, 2008.

21. Polaris and its predecessors complied with the requirements of 35 U.S.C. § 287, to the extent necessary, such that Polaris may recover pre-suit damages.

22. The claims of the Asserted Patents are directed to patent-eligible subject matter under 35 U.S.C. § 101. They are not directed to abstract ideas, and the technologies covered by the claims comprise systems and/or consist of ordered combinations of features and functions that, at the time of invention, were not, alone or in combination, well-understood, routine, or conventional.

## **DEFENDANTS' PRE-SUIT KNOWLEDGE OF ITS INFRINGEMENTS**

23. Prior to the filing of this Complaint, Polaris sent letters to Qualcomm notifying Qualcomm that various exemplary products infringe at least one or more claims of the'339 Patent, the '371 Patent, the '936 Patent, and the '344 Patent and that Qualcomm needs to take a license. *See* Aug. 9, 2024 Letter (and accompanying claim charts); *see also* October 13, 2015 Letter. Qualcomm has not agreed to license the Asserted Patents, and Polaris brought this action to protect its rights.

24. The Accused Products include, but are not limited to, the exemplary products identified in Polaris' letters to Qualcomm. Qualcomm's past and continuing sales of the Accused Products: (i) willfully infringe the Asserted Patents; and (ii) impermissibly usurp the significant benefits of Polaris' patented technologies without fair compensation.

8

## COUNT I

# (INFRINGEMENT OF U.S. PATENT NO. USP 7,184,339)

25. Plaintiff incorporates the preceding paragraphs herein by reference.

26. This cause of action arises under the patent laws of the United States, and, in particular, 35 U.S.C. §§ 271, *et seq*.

27. Polaris is the owner of all substantial rights, title, and interest in and to the '339 Patent including the right to exclude others and to enforce, sue, and recover damages for past and future infringements.

28. The '339 Patent is valid, enforceable, and was duly and legally issued by the United States Patent and Trademark Office on February 27, 2007, after full and fair examination.

29. Qualcomm has and continues to directly and/or indirectly infringe (by inducing infringement) one or more claims of the '339 Patent in this District and elsewhere in Texas and the United States by making, using, selling, offering to sell, and/or importing, and by actively inducing others to make, use, sell, offer to sell, and/or import, Qualcomm products, their components and processes, and/or products containing the same, that incorporate the fundamental technologies covered by the '339 Patent, including, but not limited to, its Snapdragon 4, 6, 7, 8, and X Series products incorporating LPDDR4/X or LPDDR5/5X memory (collectively, "the '339 Accused Products").

# Direct Infringement (35 U.S.C. § 271(a))

30. Qualcomm has directly infringed and continues to directly infringe one or more claims of the '339 Patent in this District and elsewhere in Texas and the United States.

9

31. Qualcomm has directly infringed and continues to directly infringe, either by itself or via its agent(s), at least Claim 1 of the '339 Patent<sup>5</sup> as set forth under 35 U.S.C. § 271(a) by making, offering for sale, selling, and/or importing the '339 Accused Products. Furthermore, Qualcomm makes and sells the '339 Accused Products outside of the United States and either delivers those products to its customers, distributors, and/or subsidiaries in the United States or, in the case that it delivers the '339 Accused Products outside of the United States, does so intending and/or knowing that those products are destined for the United States and/or designed and designated for sale in the United States, thereby directly infringing the '339 Patent. *See, e.g., Lake Cherokee Hard Drive Techs., L.L.C. v. Marvell Semiconductor, Inc.*, 964 F. Supp. 2d 653, 658 (E.D. Tex. 2013).

32. Furthermore, Qualcomm directly infringes the '339 Patent through its direct involvements in, and control of, the activities of subsidiaries and agents. Subject to Qualcomm's direction and control, the subsidiaries and agents conduct activities that constitute direct infringement of the '339 Patent under 35 U.S.C. § 271(a) by making, using, offering for sale, selling, and/or importing Accused Instrumentalities. Qualcomm receives direct financial benefit from such infringements by its U.S.-based subsidiaries and agents.

33. By way of illustration only, the '339 Accused Products perform each and every element of Claim 1 of the '339 Patent. The '339 Accused Products perform "[a] process for inputting and/or outputting test data and/or semi-conductor component operating control data into

<sup>&</sup>lt;sup>5</sup> Throughout this Complaint, wherever Polaris identifies specific claims of the Asserted Patents infringed by Qualcomm, Polaris expressly reserves the right to identify additional claims and products in its infringement contentions in accordance with applicable local rules and the Court's case management order. Specifically identified claims throughout this Complaint are provided for notice pleading only.

## Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 11 of 52

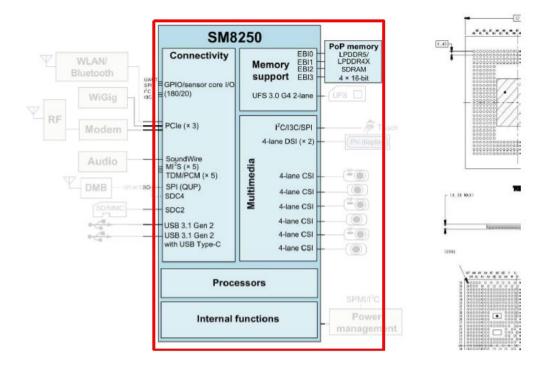

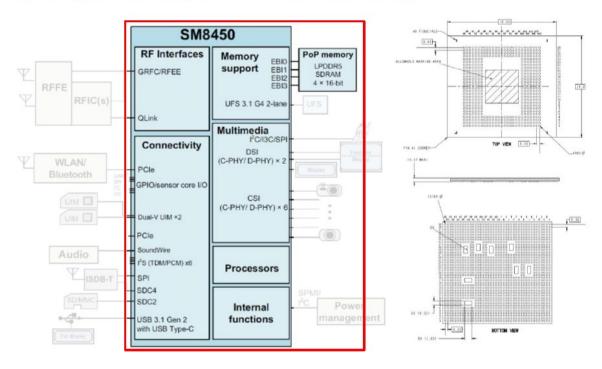

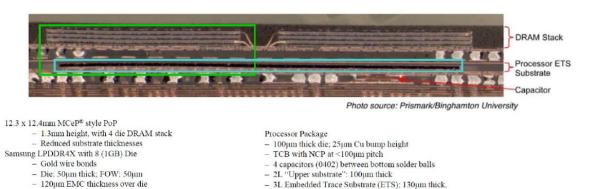

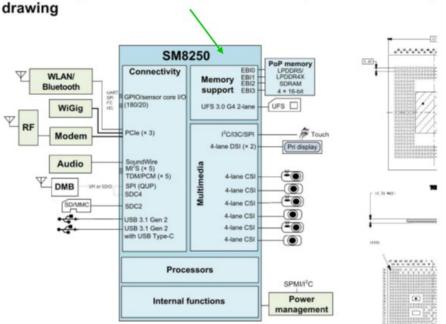

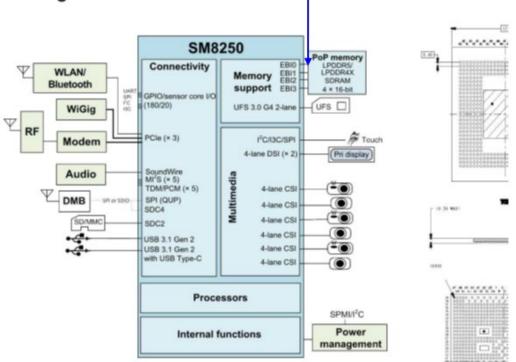

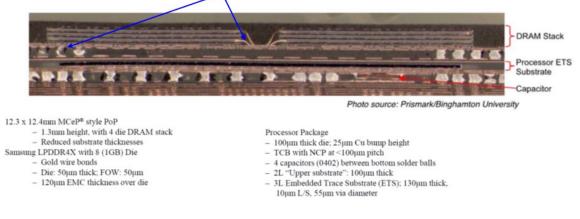

or from a semi-conductor component, whereby the semi-conductor component comprises one or more useful data memory cells for storing useful data, and one or more test data and/or semi-conductor component operating control data registers for storing test data and/or semi-conductor component operating control data, comprising" the steps of Claim 1. For instance, the '339 Accused Products, such as the SM8250, incorporate LPDDR4/4X or LPDDR5/5X memory that comply with JEDEC standards and perform the steps described below:

# Qualcom

SM8250 Device Specification 80-PL546-1 Rev. R

#### Qualcomm Technologies, Inc.

#### Device description

SM8250 is the new generation Qualcomm<sup>®</sup> Snapdragon<sup>™</sup> premium-tier processor with external 4G/5G modem (SDX55M). It is designed with the 7 nm process, for superior performance and power efficiency. SM8250 includes the following key components:

- Qualcomm<sup>®</sup> Kryo<sup>™</sup> 585 CPU built on Arm Cortex technology

- Qualcomm<sup>®</sup> Adreno<sup>™</sup> 650 GPU for the highest in graphics performance and power efficiency

- Qualcomm<sup>®</sup> Hexagon<sup>™</sup> DSP with quad Hexagon Vector eXtensions (HVX) processor for vision processing and machine learning

- Qualcomm Spectra<sup>™</sup> 480 image processing engine for the ultimate photography and videography experiences

- Adreno 665 VPU for high-quality, ultra HD video encode and decode

- Adreno 995 DPU for on-device and external ultra HD display support

- Low-power audio subsystem combined with the Qualcomm Aqstic<sup>™</sup> Audio Technologies WCD9380/WCD9385 audio codec for low power voice processing and audiophile quality audio playback

- Qualcomm<sup>®</sup> Sensing Hub for contextual awareness and always-on sensor support

- Qualcomm<sup>®</sup> Secure Processing Unit (SPU240) for advanced secure use cases

- Qualcomm<sup>®</sup> Neural Processing Unit (NPU230) for high-performance machine learning use cases

- External 802.11ax, 2 × 2 MIMO, and Bluetooth 5.1

- Quad-channel package-on-package (PoP) high-speed LPDDR5/LPDDR4X SDRAM

# (80\_PL546\_1\_R\_SM8250\_DEVICE\_SPECIFICATION.PDF)

34. The '339 Accused Products perform a process that includes "applying a control signal to the semi-conductor component for switching over the semi-conductor component from a first to a second operating mode." For instance, the '339 Accused Products that incorporate LPDDR5/5X memory apply a control signal to the semi-conductor component for switching over the semi-conductor component from a first to a second operating mode when a Mode Register Write-1 command issued by the memory controller to the LPDDR5/5X memory causes the

following command to write to the addressed mode register (a second operating mode) instead of the memory array (a first operating mode):

| SDRAM<br>COMMAND | BK<br>ORG<br>(BG,<br>16B, | SDR<br>CMD<br>PIN |     |     | DDR | COMMAN | ND PINS |     |     | CK_t<br>edge | Notes    |

|------------------|---------------------------|-------------------|-----|-----|-----|--------|---------|-----|-----|--------------|----------|

|                  | 8B)                       | CS                | CA0 | CA1 | CA2 | CA3    | CA4     | CA5 | CA6 |              |          |

| MACK             | Any                       | н                 | L   | Н   | L   | C0     | C3      | C4  | C5  | R1           |          |

| MASK<br>WRITE    | BG                        |                   | BA0 | BA1 | BG0 | BG1    |         |     |     |              | 1, 2, 3, |

| (MWR)            | 16B                       | X                 | BA0 | BA1 | BA2 | BA3    | C1      | C2  | AP  | 🖌 🖌 🕹        | 6,7      |

|                  | 8B                        |                   | BA0 | BA1 | BA2 | V      |         |     |     |              |          |

| WRITE            | Any                       | н                 | L   | Н   | H   | C0     | C3      | C4  | C5  | R1           |          |

| (WR16 or         | BG                        |                   | BA0 | BA1 | BG0 | BG1    |         |     |     |              | 1, 2, 3, |

| WR)              | 16B                       | X                 | BA0 | BA1 | BA2 | BA3    | C1      | C2  | AP  | 🛛 💽 🖌 F1     | 6, 7, 8  |

| (VIC)            | 8B                        |                   | BA0 | BA1 | BA2 | V      |         |     |     |              |          |

|                  | -                         |                   |     |     |     |        |         |     |     |              |          |

Table 201 — Command Truth Table (cont'd)

|                                | 1   |   |     | 1   | 1   |     |     |     |     |              |      |

|--------------------------------|-----|---|-----|-----|-----|-----|-----|-----|-----|--------------|------|

| MODE                           |     | н | L   | L   | L   | Н   | н   | L   | Н   | _ R1         |      |

| REGISTER<br>WRITE-1<br>(MRW-1) | Any | × | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | <b>−€</b> F1 | 1, 2 |

| MODE                           |     | Н | L   | L   | L   | H   | L   | L   | OP7 | _ <b>R</b> 1 |      |

| REGISTER<br>WRITE-2<br>(MRW-2) | Any | х | OP0 | OP1 | OP2 | OP3 | OP4 | OP5 | OP6 | <b>₹</b> F1  | 1, 2 |

| MODE                           |     | н | L   | L   | L   | Н   | н   | L   | L   | R1           |      |

| REGISTER<br>READ (MRR)         | Any | х | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | <b>₹</b> F1  | 1, 2 |

|                                |     |   |     |     |     |     |     |     |     |              |      |

(JEDEC Standard No. 209-5C, Page 190)

35. As another example, the '339 Accused Products that incorporate LPDDR4/4X memory apply a control signal to the semi-conductor component for switching over the semi-conductor component from a first to a second operating mode when a Mode Register Write-1 command issued by the memory controller to the LPDDR4/4X memory causes the following command to write to the addressed mode register (a second operating mode) instead of the memory array (a first operating mode):

|                       | SDR Com-<br>mand Pins |     |     |     |     |     |     |              |           |

|-----------------------|-----------------------|-----|-----|-----|-----|-----|-----|--------------|-----------|

| SDRAM Command         | cs                    | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CK_t<br>edge | Notes     |

|                       |                       |     |     |     | v   |     |     | 112          |           |

|                       | н                     | L   | L   | Н   | L   | L   | BL  | R1           | 1,2,3,6,7 |

| Write -1 (WR-1)       | L                     | BA0 | BA1 | BA2 | V   | C9  | AP  | R2           | ,9        |

| Self Refresh Exit     | н                     | L   | L   | н   | L   | н   | V   | R1           | 10        |

| (SRX)                 | L                     |     |     | ١   | /   |     |     | R2           | 1,2       |

| Mask Write -1         | н                     | L   | L   | н   | н   | L   | L   | R1           | 1,2,3,5,6 |

| (MWR-1)               | L                     | BA0 | BA1 | BA2 | V   | C9  | AP  | R2           | ,9        |

| DELL                  | н                     | L   | L   | н   | н   | н   | V   | R1           | 10        |

| RFU                   | L                     |     |     | ١   | /   |     |     | R2           | 1,2       |

| Deed 4 (DD 4)         | н                     | L   | н   | L   | L   | L   | BL  | R1           | 1,2,3,6,7 |

| Read -1 (RD-1)        | L                     | BA0 | BA1 | BA2 | V   | C9  | AP  | R2           | ,9        |

|                       |                       |     |     |     |     |     |     |              |           |

| Mode Register Write - | н                     | L   | н   | Н   | L   | L   | OP7 | R1           |           |

| 1 (MRW-1)             | L                     | MAO | MA1 | MA2 | MA3 | MA4 | MA5 | R2           | 1,11      |

| Mode Register Write-  | н                     | L   | н   | н   | L   | н   | OP6 | R1           |           |

| 2 (MRW-2)             | L                     | OP0 | OP1 | OP2 | OP3 | OP4 | OP5 | R2           | 1,11      |

| Mode Register Read-   | н                     | L   | н   | н   | н   | L   | V   | R1           | 4.0.40    |

| 1 (MRR-1)             | L                     | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | R2           | 1,2,12    |

## Table 169 — Command Truth Table

(JEDEC Standard No. 209-4C, Pages 270 and 271)

36. The '339 Accused Products perform a process that includes "applying an address signal to the semi-conductor component." For instance, the '339 Accused Products that incorporate LPDDR5/5X memory apply an address signal to the semi-conductor component on lines CA0 to CA6:

| SDRAM<br>COMMAND | BK<br>ORG<br>(BG,<br>16B, | SDR<br>CMD<br>PIN |     |     |     | DDR COMMAND PINS CK_t<br>edge |     |     |     |              | Notes    |

|------------------|---------------------------|-------------------|-----|-----|-----|-------------------------------|-----|-----|-----|--------------|----------|

|                  | 8B)                       | CS                | CA0 | CA1 | CA2 | CA3                           | CA4 | CA5 | CA6 | 1            |          |

| MACK             | Any                       | н                 | L   | н   | L   | CU                            | C3  | C4  | C5  | _ <b>R</b> 1 |          |

| MASK<br>WRITE    | BG                        |                   | BA0 | BA1 | BG0 | BG1                           |     |     |     |              | 1, 2, 3, |

| (MWR)            | 16B                       | X                 | BA0 | BA1 | BA2 | BA3                           | C1  | C2  | AP  | 🖌 💽 F1       | 6,7      |

|                  | 8B                        |                   | BA0 | BA1 | BA2 | V                             |     |     |     |              |          |

| WOITE            | Any                       | Н                 | L   | Н   | Н   | C0                            | C3  | C4  | C5  | _ <b>R</b> 1 |          |

| WRITE            | BG                        |                   | BA0 | BA1 | BG0 | BG1                           |     |     |     |              | 1, 2, 3, |

| (WR16 or<br>WR)  | 16B                       | X                 | BA0 | BA1 | BA2 | BA3                           | C1  | C2  | AP  | 🖌 💽 F1       | 6, 7, 8  |

| (VVIC)           | 8B                        |                   | BA0 | BA1 | BA2 | V                             |     |     |     |              |          |

#### Table 201 — Command Truth Table (cont'd)

| MODE                           |     | н | L   | L   | L   | Н   | Н   | L   | Н   | <b>_</b> R1  |      |

|--------------------------------|-----|---|-----|-----|-----|-----|-----|-----|-----|--------------|------|

| REGISTER<br>WRITE-1<br>(MRW-1) | Any | × | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | <b>₹</b> F1  | 1, 2 |

| MODE                           |     | Н | L   | L   | L   | Н   | L   | L   | OP7 | R1           |      |

| REGISTER<br>WRITE-2<br>(MRW-2) | Any | х | OP0 | OP1 | OP2 | OP3 | OP4 | OP5 | OP6 | <b>−₹</b> F1 | 1, 2 |

| MODE                           |     | н | L   | L   | L   | н   | н   | L   | L   | R1           |      |

| REGISTER<br>READ (MRR)         | Any | х | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | <b>₹</b> F1  | 1, 2 |

(JEDEC Standard No. 209-5C, Page 190)

37. As another example, the '339 Accused Products that incorporate LPDDR4/4X

memory apply an address signal to the semi-conductor component on lines CA0 to CA5:

|                       | SDR Com-<br>mand Pins |     | SDR CA Pins (6) |          |     |     |     |              |           |

|-----------------------|-----------------------|-----|-----------------|----------|-----|-----|-----|--------------|-----------|

| SDRAM Command         | CS                    | CA0 | CA1             | CA2      | CA3 | CA4 | CA5 | CK_t<br>edge | Notes     |

|                       |                       |     |                 |          | v   |     |     | 112          |           |

|                       | Н                     | L   | L               | н        | L   | L   | BL  | R1           | 1,2,3,6,7 |

| Write -1 (WR-1)       | L                     | BA0 | BA1             | BA2      | V   | C9  | AP  | R2           | ,9        |

| Self Refresh Exit     | н                     | L   | L               | н        | L   | н   | V   | R1           | 4.0       |

| (SRX)                 | L                     |     |                 | <u>ا</u> | V   |     |     | R2           | 1,2       |

| Mask Write -1         | н                     | L   | L               | н        | н   | L   | L   | R1           | 1,2,3,5,6 |

| (MWR-1)               | L                     | BA0 | BA1             | BA2      | V   | C9  | AP  | R2           | ,9        |

| DELL                  | н                     | L   | L               | н        | н   | н   | V   | R1           | 10        |

| RFU                   | L                     |     |                 | · · · ·  | V   |     |     | R2           | 1,2       |

| Bood 4 (BD 4)         | н                     | L   | н               | L        | L   | L   | BL  | R1           | 1,2,3,6,7 |

| Read -1 (RD-1)        | L                     | BA0 | BA1             | BA2      | V   | C9  | AP  | R2           | ,9        |

|                       | _                     |     |                 |          |     |     |     |              |           |

| Mode Register Write - | Н                     | L   | Н               | н        | L   | L   | OP7 | R1           |           |

| 1 (MRW-1)             | L                     | MAO | MA1             | MA2      | MA3 | MA4 | MA5 | R2           | 1,11      |

| Mode Register Write-  | н                     | L   | н               | н        | L   | н   | OP6 | R1           |           |

| 2 (MRW-2)             | L                     | OP0 | OP1             | OP2      | OP3 | OP4 | OP5 | R2           | 1,11      |

| Mode Register Read-   | н                     | L   | н               | н        | н   | L   | V   | R1           | 10.10     |

| 1 (MRR-1)             | L                     | MAO | MA1             | MA2      | MA3 | MA4 | MA5 | R2           | 1,2,12    |

(JEDEC Standard No. 209-4C, Pages 270 and 271)

#### Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 15 of 52

38. In the '339 Accused Products, "in the second operating mode one or more of the test data and/or semi-conductor component operating control data registers of the semi-conductor component is addressed by the address signal, and in the first operating mode one or more of the useful data memory cells." For instance, in the '339 Accused Products that incorporate LPDDR5/5X memory, once the Mode Register Write-1 command is issued by the memory controller to the LPDDR5/5X memory, the following command Mode Register Write-2 writes the data to the register addressed by the address signal MA0 to MA6:

| SDRAM<br>COMMAND  | BK<br>ORG<br>(BG,<br>16B, | SDR<br>CMD<br>PIN |     | DDR COMMAND PINS CK_t<br>edge |     |     |     |     | Notes |        |          |

|-------------------|---------------------------|-------------------|-----|-------------------------------|-----|-----|-----|-----|-------|--------|----------|

|                   | 8B)                       | CS                | CA0 | CA1                           | CA2 | CA3 | CA4 | CA5 | CA6   |        |          |

| MACK              | Any                       | н                 | L   | Н                             | L   | C0  | C3  | C4  | C5    | _ 🖌 R1 |          |

| MASK<br>WRITE     | BG                        |                   | BA0 | BA1                           | BG0 | BG1 |     |     |       |        | 1, 2, 3, |

| (MWR)             | 16B                       | X                 | BA0 | BA1                           | BA2 | BA3 | C1  | C2  | AP    | 🖌 🖌 🕹  | 6,7      |

|                   | 8B                        | 1                 | BA0 | BA1                           | BA2 | V   |     |     |       |        |          |

| WDITE             | Any                       | Н                 | L   | Н                             | Н   | C0  | C3  | C4  | C5    | R1     |          |

| WRITE<br>(WR16 or | BG                        |                   | BA0 | BA1                           | BG0 | BG1 |     |     |       |        | 1, 2, 3, |

|                   | 16B                       | X                 | BA0 | BA1                           | BA2 | BA3 | C1  | C2  | AP    | 🖌 🖌 🕹  | 6, 7, 8  |

| WR)               | 8B                        |                   | BA0 | BA1                           | BA2 | V   |     |     |       |        |          |

|   | MODE                           |     | Н | L   | L   | L   | Н   | Н   | L   | Н   | _ R1         |      |

|---|--------------------------------|-----|---|-----|-----|-----|-----|-----|-----|-----|--------------|------|

|   | REGISTER<br>WRITE-1<br>(MRW-1) | Any | х | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | <b>₹</b> F1  | 1, 2 |

|   | MODE                           |     | Н | L   | L   | L   | н   | L   | L   | OP7 | R1           |      |

|   | REGISTER<br>WRITE-2<br>(MRW-2) | Any | х | OP0 | OP1 | OP2 | OP3 | OP4 | OP5 | OP6 | <b>−₹</b> F1 | 1, 2 |

| T | MODE                           |     | н | L   | L   | L   | н   | н   | L   | L   | R1           |      |

|   | REGISTER<br>READ (MRR)         | Any | х | MA0 | MA1 | MA2 | МАЗ | MA4 | MA5 | MA6 | <b>₹</b> F1  | 1, 2 |

(JEDEC Standard No. 209-5C, Page 190)

39. The LPDDR5/5X Mode Registers 31 to 34 are test data registers used for DQ Calibration operation, and other registers, for example Mode Registers 35 to 40 are operating control data registers. And the LPDDR5/5X memory is addressed by the address signals, for example during the write commands MWR, WR16, WR:

| MR# | MA[6:0]         | Access | OP[7] | OP[6]                                                  | OP[5]      | OP[4]       | OP[3]        | OP[2]       | OP[1] | OP[0] |  |  |  |

|-----|-----------------|--------|-------|--------------------------------------------------------|------------|-------------|--------------|-------------|-------|-------|--|--|--|

| 31  | 1Fн             | W      |       | Lower-Byte per-bit control Register for DQ Calibration |            |             |              |             |       |       |  |  |  |

| 32  | 20н             | W      |       | Upper-By                                               | yte per-bi | t control I | Register fo  | r DQ Calibr | ation |       |  |  |  |

| 33  | 21н             | W      |       |                                                        | DQ         | Calibratio  | n Pattern "  | A"          |       |       |  |  |  |

| 34  | 22н             | W      |       |                                                        | DQ         | Calibratio  | n Pattern "  | 'B"         |       |       |  |  |  |

| 35  | 23 <sub>H</sub> | R      |       |                                                        | WCK2D      | QI Oscill   | ator Count   | - LSB       |       |       |  |  |  |

| 36  | 24 <sub>H</sub> | R      |       |                                                        | WCK2D      | QI Oscilla  | ator Count   | - MSB       |       |       |  |  |  |

| 37  | 25н             | R/W    |       | W                                                      | CK2DQI     | interval ti | mer run tin  | ne setting  |       |       |  |  |  |

| 38  | 26 <sub>H</sub> | R      |       |                                                        | WCK2D      | QO Oscil    | lator Count  | t - LSB     |       |       |  |  |  |

| 39  | 27н             | R      |       | WCK2DQO Oscillator Count - MSB                         |            |             |              |             |       |       |  |  |  |

| 40  | 284             | R/W    |       | W                                                      |            | interval t  | imer run tir | ne setting  |       |       |  |  |  |

|     |                 |        |       |                                                        |            | -           |              |             |       |       |  |  |  |

# Table 58 — Mode Register Assignment in LPDDR5 SDRAM (MR8 OP[1:0]=00<sub>B</sub>)<sup>1,2,3,4,5</sup> (cont'd)

# (JEDEC Standard No. 209-5C, Page 127)

| SDRAM<br>COMMAND         | BK<br>ORG<br>(BG,<br>16B, | SDR<br>CMD<br>PIN |     |     |     |     |     |     |     | CK_t<br>edge | Notes    |

|--------------------------|---------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|--------------|----------|

|                          | 8B)                       | CS                | CA0 | CA1 | CA2 | CA3 | CA4 | CA5 | CA6 |              |          |

| MACK                     | Any                       | Н                 | L   | Н   | L   | C0  | C3  | C4  | C5  | R1           |          |

| MASK<br>WRITE            | BG                        | ×                 | BA0 | BA1 | BG0 | BG1 | C1  | C2  |     |              | 1, 2, 3, |

| (MWR)                    | 16B                       |                   | BA0 | BA1 | BA2 | BA3 |     |     | AP  | 🖌 F1         | 6, 7     |

|                          | 8B                        |                   | BA0 | BA1 | BA2 | V   |     |     |     |              |          |

| WDITE                    | Any                       | Н                 | L   | Н   | H   | C0  | C3  | C4  | C5  | R1           |          |

| WRITE<br>(WR16 or<br>WR) | BG                        |                   | BA0 | BA1 | BG0 | BG1 |     |     |     |              | 1, 2, 3, |

|                          | 16B                       | X                 | BA0 | BA1 | BA2 | BA3 | C1  | C2  | AP  | <b>▼</b> F1  | 6, 7, 8  |

| WR)                      | 8B                        |                   | BA0 | BA1 | BA2 | V   |     |     |     |              |          |

| - 1 |                                |     |   |     |     | 1   |     | 1   |     |     |              |      |

|-----|--------------------------------|-----|---|-----|-----|-----|-----|-----|-----|-----|--------------|------|

|     | MODE                           |     | Н | L   | L   | L   | Н   | Н   | L   | Н   | _ R1         |      |

|     | REGISTER<br>WRITE-1<br>(MRW-1) | Any | × | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | <b>₹</b> F1  | 1, 2 |

|     | MODE                           |     | Н | L   | L   | L   | Н   | L   | L   | OP7 | <b>_</b> R1  |      |

|     | REGISTER<br>WRITE-2<br>(MRW-2) | Any | х | OP0 | OP1 | OP2 | OP3 | OP4 | OP5 | OP6 | <b>−e</b> F1 | 1, 2 |

|     | MODE                           |     | н | L   | L   | L   | Н   | н   | L   | L   | <b>€</b> R1  |      |

|     | REGISTER<br>READ (MRR)         | Any | х | MA0 | MA1 | MA2 | MA3 | MA4 | MA5 | MA6 | <b>₹</b> F1  | 1, 2 |

|     |                                |     |   |     |     |     |     |     |     |     |              |      |

(JEDEC Standard No. 209-5C, Page 190)

40. As another example, in the '339 Accused Products that incorporate LPDDR4/4X memory, once the Mode Register Write-1 command is issued by the memory controller to the LPDDR4/4X memory, the following command Mode Register Write-2 writes the data to the register addressed by the address signal MA0 to MA5:

|                       | SDR Com-<br>mand Pins |     |     | SDR CA | Pins (6) |     |     |              |           |

|-----------------------|-----------------------|-----|-----|--------|----------|-----|-----|--------------|-----------|

| SDRAM Command         | CS                    | CA0 | CA1 | CA2    | CA3      | CA4 | CA5 | CK_t<br>edge | Notes     |

|                       |                       |     |     |        | v        |     |     | 112          |           |

|                       | н                     | L   | L   | Н      | L        | L   | BL  | R1           | 1,2,3,6,7 |

| Write -1 (WR-1)       | L                     | BA0 | BA1 | BA2    | V        | C9  | AP  | R2           | ,9        |

| Self Refresh Exit     | н                     | L   | L   | н      | L        | н   | V   | R1           | 10        |

| (SRX)                 | L                     |     | R2  | 1,2    |          |     |     |              |           |

| Mask Write -1         | Н                     | L   | L   | н      | н        | L   | L   | R1           | 1,2,3,5,6 |

| (MWR-1)               | L                     | BA0 | BA1 | BA2    | V        | C9  | AP  | R2           | ,9        |

| DELL                  | н                     | L   | L   | н      | н        | н   | V   | R1           | 1,2       |

| RFU                   | L                     | V   |     |        |          |     |     |              | 1,2       |

| Bood 1 (BD 1)         | н                     | L   | н   | L      | L        | L   | BL  | R1           | 1,2,3,6,7 |

| Read -1 (RD-1)        | L                     | BA0 | BA1 | BA2    | V        | C9  | AP  | R2           | ,9        |

|                       | _                     |     |     |        |          |     |     |              |           |

| Mode Register Write - | н                     | 1   | н   | н      | 1        | 1   | OP7 | R1           |           |

| 1 (MRW-1)             | L                     | MAO | MA1 | MA2    | MA3      | MA4 | MA5 | R2           | 1,11      |

| Mode Register Write-  | н                     | L   | н   | н      | L        | н   | OP6 | R1           |           |

| 2 (MRW-2)             | L                     | OP0 | OP1 | OP2    | OP3      | OP4 | OP5 | R2           | 1,11      |

| Mode Register Read-   | н                     | L   | н   | н      | н        | L   | V   | R1           | 10.10     |

| 1 (MRR-1)             | L                     | MA0 | MA1 | MA2    | MA3      | MA4 | MA5 | R2           | 1,2,12    |

(JEDEC Standard No. 209-4C, Pages 270 and 271)

41. The LPDDR4/4X Mode Registers 32 and 40 are test data registers used for DQ Calibration operation, and other registers, for example Mode Registers 0 to 4 are operating control data registers. And the LPDDR4/4X memory is addressed by the address signals, for example during the write commands WR-1, MWR-1, and the read command RD-1:

| MR#       | OP[7]                                         | OP[6]  | OP[5] OP[4]  |                   | OP[3]             | OP[2]  | OP[1]        | OP[0]           |  |  |  |  |  |

|-----------|-----------------------------------------------|--------|--------------|-------------------|-------------------|--------|--------------|-----------------|--|--|--|--|--|

| 0         | CATR                                          | RFU    | RFU          | RZ                | ZQI               | RFU    | Latency Mode | Retresn<br>mode |  |  |  |  |  |

| 1         | RPST                                          |        | nWR (for AP) |                   | RD-PRE            | WR-PRE | B            | L               |  |  |  |  |  |

| 2         | WR Lev                                        | WLS    |              | WL                |                   |        | RL           |                 |  |  |  |  |  |

| 3         | DBI-WR                                        | DBI-RD |              | PDDS              |                   | PPRP   | WR PST       | PU-CAL          |  |  |  |  |  |

| 4         | TUF Thermal Offset PPRE SR Abort Refresh Rate |        |              |                   |                   |        |              |                 |  |  |  |  |  |

|           |                                               |        |              |                   |                   |        |              |                 |  |  |  |  |  |

| 32        |                                               |        | DQ C         | alibration Patte  | rn "A" (default = | 5AH)   |              |                 |  |  |  |  |  |

| 33        |                                               |        |              | R                 | FU                |        |              |                 |  |  |  |  |  |

| 34        |                                               |        |              | R                 | FU                |        |              |                 |  |  |  |  |  |

| 35        |                                               |        |              | R                 | FU                |        |              |                 |  |  |  |  |  |

| 36        |                                               |        |              | R                 | FU                |        |              |                 |  |  |  |  |  |

| 37        |                                               |        |              | R                 | FU                |        |              |                 |  |  |  |  |  |

| 38        |                                               |        |              | R                 | FU                |        |              |                 |  |  |  |  |  |

| 39        |                                               |        | Rese         | erved for testing | I - SDRAM will i  | anore  |              |                 |  |  |  |  |  |

| 40        |                                               |        | DQ C         | alibration Patte  | rn "B" (default = | 3CH)   |              |                 |  |  |  |  |  |

| · · · · · |                                               |        |              |                   |                   |        |              |                 |  |  |  |  |  |

Table 13 — Mode Register Assignment in LPDDR4 SDRAM

|                                       | SDR Com-<br>mand Pins |     |     | SDR CA | Pins (6) |     |     |              |           |

|---------------------------------------|-----------------------|-----|-----|--------|----------|-----|-----|--------------|-----------|

| SDRAM Command                         | CS                    | CA0 | CA1 | CA2    | CA3      | CA4 | CA5 | CK_t<br>edge | Notes     |

| · · · · · · · · · · · · · · · · · · · |                       |     |     |        |          |     |     | 112          |           |

| Write -1 (WR-1)                       | н                     | L   | L   | н      | L        | L   | BL  | R1           | 1,2,3,6,7 |

| Wille -1 (WK-1)                       | L                     | BA0 | BA1 | BA2    | V        | C9  | AP  | R2           | ,9        |

| Self Refresh Exit                     | н                     | L   | L   | н      | L        | Н   | V   | R1           | 10        |

| (SRX)                                 | 1                     |     |     | \      | /        |     |     | R2           | 1,2       |

| Mask Write -1                         | н                     | L   | L   | н      | н        | L   | L   | R1           | 1,2,3,5,6 |

| (MWR-1)                               | L                     | BA0 | BA1 | BA2    | V        | C9  | AP  | R2           | ,9        |

| DELL                                  | н                     | L   | L   | н      | н        | н   | V   | R1           | 4.0       |

| RFU                                   | 1                     | V   |     |        |          |     |     |              | 1,2       |

|                                       | н                     | L   | н   | L      | L        | L   | BL  | R1           | 1,2,3,6,7 |

| Read -1 (RD-1)                        | L                     | BA0 | BA1 | BA2    | V        | C9  | AP  | R2           | ,9        |

|                                       |                       |     |     |        |          |     |     |              |           |

| Mode Register Write -                 | н                     | L   | Н   | н      | L        | L   | OP7 | R1           |           |

| 1 (MRW-1)                             | L                     | MAO | MA1 | MA2    | MA3      | MA4 | MA5 | R2           | 1,11      |

| Mode Register Write-                  | н                     | L   | н   | н      | L        | н   | OP6 | R1           |           |

| 2 (MRW-2)                             | L                     | OP0 | OP1 | OP2    | OP3      | OP4 | OP5 | R2           | 1,11      |

| Mode Register Read-                   | н                     | L   | н   | н      | н        | L   | V   | R1           | 4.0.40    |

| 1 (MRR-1)                             | L                     | MAO | MA1 | MA2    | MA3      | MA4 | MA5 | R2           | 1,2,12    |

(JEDEC Standard No. 209-4C, Pages 270 and 271)

# Indirect Infringement (Inducement – 35 U.S.C. § 271(b))

42. In addition and/or in the alternative to its direct infringements, Qualcomm has indirectly infringed and continues to indirectly infringe one or more claims of the '339 Patent by knowingly and intentionally inducing others, including its subsidiaries, agents, distributors, affiliates, retailers, suppliers, integrators, importers, customers, and/or consumers, to directly infringe by making, using, offering to sell, selling and/or importing into the United States the '339 Accused Products.

43. At a minimum, Qualcomm has knowledge of the '339 Patent since being served with this Complaint. Qualcomm also had knowledge of the '339 Patent since receiving letters from Polaris providing details of its infringements prior to the filing of this Complaint. Since receiving notice of its infringements, Qualcomm has actively induced the direct infringements of its subsidiaries, agents, distributors, affiliates, retailers, suppliers, integrators, importers, customers, and/or consumers as set forth under U.S.C. § 271(b). Such inducements have been committed with

#### Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 19 of 52

the knowledge, or with willful blindness to the fact, that the acts induced constitute infringements of the '339 Patent. Indeed, Qualcomm has intended to cause, continues to intend to cause, and has taken and continues to take, affirmative steps to induce infringement by, among other things, creating and disseminating advertisements and instructive materials that promote the infringing use of the '339 Accused Products; creating and/or maintaining established distribution channels for the '339 Accused Products into and within the United States; manufacturing the '339 Accused Products in conformity with U.S. laws and regulations; distributing or making available datasheets supporting use of the '339 Accused Products that promote their features, specifications, and applications; promoting the incorporation of the '339 Accused Products into end-user products; and providing technical support and/or related services for these products to purchasers in the United States.

## Damages

44. On information and belief, despite having knowledge of the '339 Patent and knowledge that it is directly and/or indirectly infringing one or more claims of the '339 Patent, Qualcomm has nevertheless continued its infringing conduct and disregarded an objectively high likelihood of infringement. Qualcomm infringing activities relative to the '339 Patent have been, and continue to be, willful, wanton, malicious, in bad-faith, deliberate, consciously wrongful, flagrant, characteristic of a pirate, and an egregious case of misconduct beyond typical infringement such that Polaris is entitled to enhanced damages under 35 U.S.C. § 284 up to three times the amount found or assessed.

45. Polaris has been damaged as a result of Qualcomm's infringing conduct described in this Count. Qualcomm is, thus, liable to Polaris in an amount that adequately compensates Polaris for Qualcomm's infringements, which, by law, cannot be less than a reasonable royalty, together with interest and costs as fixed by this Court under 35 U.S.C. § 284.

## COUNT II

## (INFRINGEMENT OF U.S. PATENT NO. 7,499,371)

46. Plaintiff incorporates the preceding paragraphs herein by reference.

47. This cause of action arises under the patent laws of the United States, and, in particular, 35 U.S.C. §§ 271, *et seq*.

48. Polaris is the owner of all substantial rights, title, and interest in and to the '371 Patent including the right to exclude others and to enforce, sue, and recover damages for past and future infringements.

49. The '371 Patent is valid, enforceable, and was duly and legally issued by the United States Patent and Trademark Office on March 3, 2009, after full and fair examination.

50. Qualcomm has and continues to directly and/or indirectly infringe (by inducing infringement) one or more claims of the '371 Patent in this District and elsewhere in Texas and the United States by making, using, selling, offering to sell, and/or importing, and by actively inducing others to make, use, sell, offer to sell, and/or import, Qualcomm products, their components and processes, and/or products containing the same that incorporate the fundamental technologies covered by the '371Patent, including, but not limited to, its Snapdragon 8 and X series products that incorporate LPDDR5/5X memory (collectively, "the '371 Accused Products").

## Direct Infringement (35 U.S.C. § 271(a))

51. Qualcomm has directly infringed and continues to directly infringe one or more claims of the '371 Patent in this District and elsewhere in Texas and the United States.

52. Qualcomm has directly infringed and continues to directly infringe, either by itself or via its agent(s), at least Claim 6 of the '371 Patent as set forth under 35 U.S.C. § 271(a) by making, offering for sale, selling, and/or importing the '371 Accused Products. Furthermore, Qualcomm makes and sells the '371 Accused Products outside of the United States and either

#### Case 7:24-cv-00296 Document 1 Filed 11/19/24 Page 21 of 52

delivers those products to its customers, distributors, and/or subsidiaries in the United States or, in the case that it delivers the '371 Accused Products outside of the United States, does so intending and/or knowing that those products are destined for the United States and/or designed and designated for sale in the United States, thereby directly infringing the '371 Patent. *See, e.g., Lake Cherokee Hard Drive Techs., L.L.C. v. Marvell Semiconductor, Inc.*, 964 F. Supp. 2d 653, 658 (E.D. Tex. 2013).

53. Furthermore, Qualcomm directly infringes the '371 Patent through its direct involvements in, and control of, the activities of subsidiaries and agents. Subject to Qualcomm's direction and control, the subsidiaries and agents conduct activities that constitute direct infringement of the '371 Patent under 35 U.S.C. § 271(a) by making, using, offering for sale, selling, and/or importing Accused Instrumentalities. Qualcomm receives direct financial benefit from such infringements by its U.S.-based subsidiaries and agents.

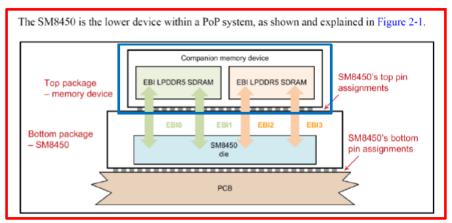

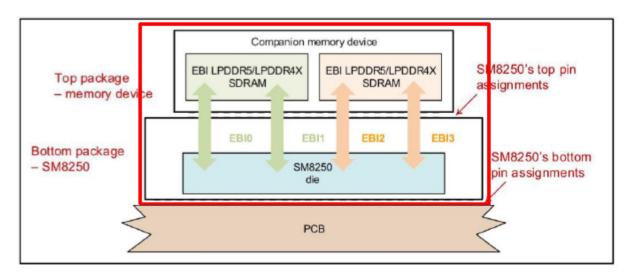

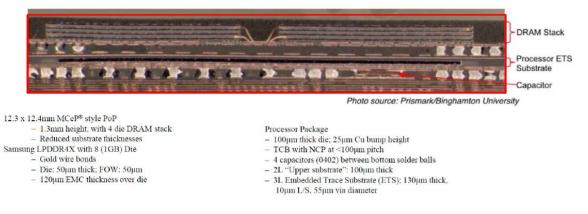

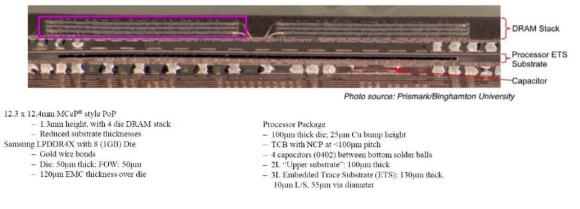

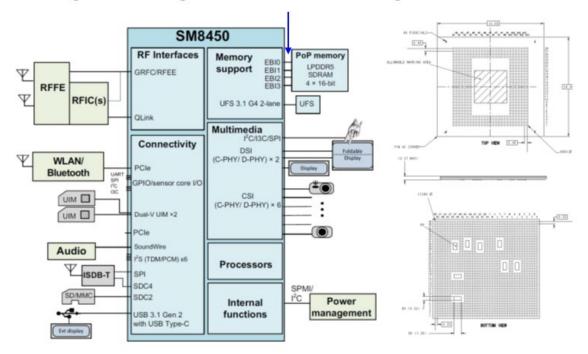

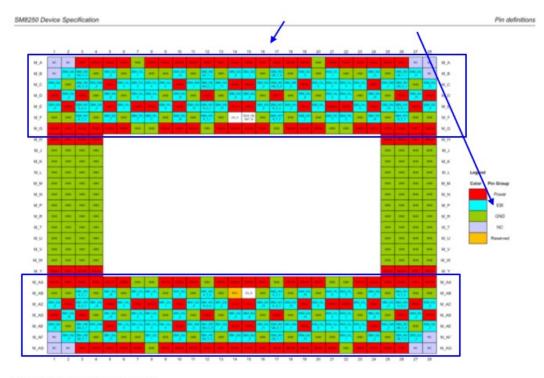

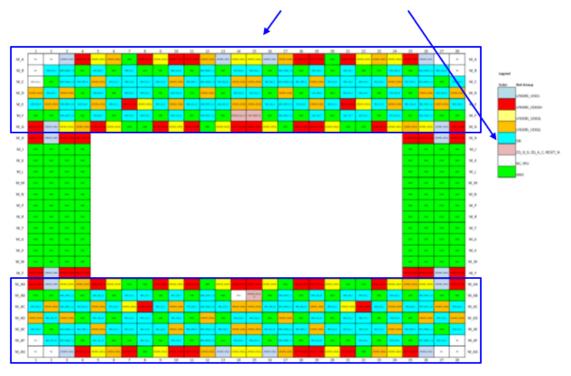

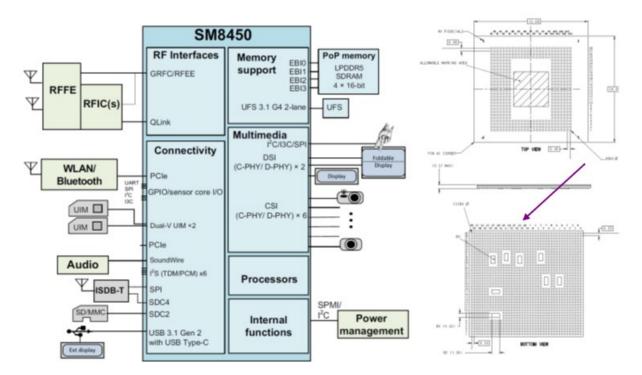

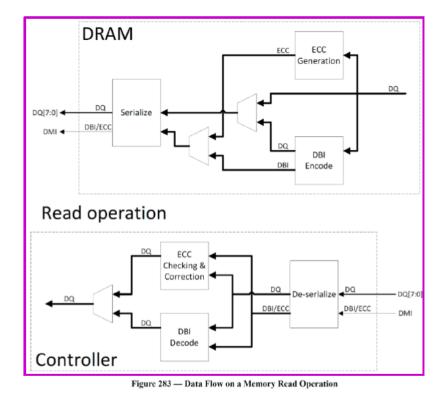

54. By way of illustration only, the '371 Accused Products include each and every element of Claim 6 of the '371 Patent. The '371 Accused Products are a "system" that comprise the limitations of Claim 6. For instance, the '371 Accused Products comprise "a semiconductor memory apparatus" as shown below from the data sheet for the SM8450:

Figure 2-1 PoP system pin assignments

(80-11140-1 SM8450 SM8450P Data Sheet.pdf, Page 13)

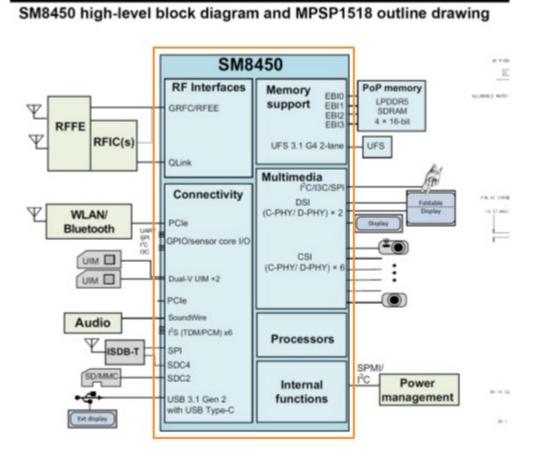

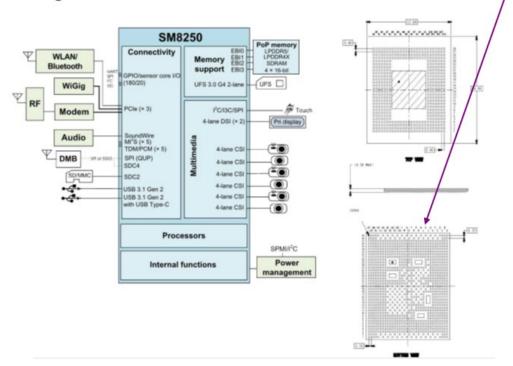

55. The '371 Accused Products further comprise "a processor unit which is configured to: transmit a command instruction to the semiconductor memory apparatus, wherein the command instruction is at least one of a write instruction and a read instruction." For instance, the '371 Accused Products such as the SM8450 incorporate a processor unit which is configured to transmit a command instruction to the semiconductor memory apparatus:

(80-11140-1 SM8450 SM8450P Data Sheet.pdf, Page 1)

Pin definitions

## 2.3.2 Pin descriptions: MSM top

Descriptions of top pins are presented in Table 2-5 and Table 2-6.

Table 2-5 MSM top pin descriptions - general pins

| Pad # | Pad name        | Pad characte | ristics 1 | Functional description                    |

|-------|-----------------|--------------|-----------|-------------------------------------------|

| Pau # | and/or function | Voltage      | Туре      | Functional description                    |

| 4_F15 | DDR_RESET_N     | PX1          | DO        | LPDDR5 reset (shared by EBIs)             |

| M_C6  | EBIO_CA_0       | EBI          | DO        | EBI0 LPDDR5 command/address bit 0         |

| M_E6  | EBI0_CA_1       | EBI          | DO        | EBI0 LPDDR5 command/address bit 1         |

| M_D7  | EBI0_CA_2       | EBI          | DO        | EBI0 LPDDR5 command/address bit 2         |

| M_D8  | EBIO_CA_3       | EBI          | DO        | EBI0 LPDDR5 command/address bit 3         |

| М_СВ  | EBIO_CA_4       | EBI          | DO        | EBI0 LPDDR5 command/address bit 4         |

| M_E9  | EBIO_CA_5       | EBI          | DO        | EBI0 LPDDR5 command/address bit 5         |

| M_C9  | EBIO_CA_6       | EBI          | DO        | EBI0 LPDDR5 command/address bit 6         |

| M_F8  | EBI0_CK_C       | EBI          | DO        | EBI0 LPDDR5 differential clock - negative |

| M_F7  | EBI0_CK_T       | EBI          | DO        | EBI0 LPDDR5 differential clock - positive |

| M_C7  | EBIO_CS_0       | EBI          | DO        | EBI0 LPDDR5 chip select 0                 |

| M_B7  | EBI0_CS_1       | EBI          | DO        | EBI0 LPDDR5 chip select 1                 |

| M_C4  | EBIO_DMI_0      | EBI          | DO        | EBI0 LPDDR5 data mask for byte 0          |

| M_C11 | EBI0_DMI_1      | EBI          | DO        | EBI0 LPDDR5 data mask for byte 1          |

| M_E1  | EBI0_DQ_0       | EBI          | В         | EBI0 LPDDR5 data bit 0                    |

| M_C1  | EBI0_DQ_1       | EBI          | В         | EBI0 LPDDR5 data bit 1                    |

(80-11140-1 SM8450 SM8450P Data Sheet.pdf, Page 52)

(JEDEC Standard No. 209-5C, Page 25)

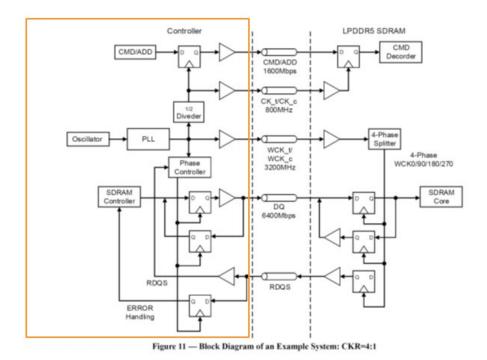

56. The '371 Accused Products processor unit is further configured to "communicate a data signal with the semiconductor memory apparatus" and "transmit a data clock signal to latch the data signal." For instance, the '371 Accused Products such as the SM8450 incorporate a processor unit that is configured to communicate a data signal with the semiconductor memory apparatus and transmit a data clock signal to latch the data signal:

| B14   | EBI0_DQ_9  | EBI | В | EBI0 LPDDR5 data bit 9  |  |

|-------|------------|-----|---|-------------------------|--|

| 1_D14 | EBI0_DQ_8  | EBI | В | EBI0 LPDDR5 data bit 8  |  |

| M_F5  | EBI0_DQ_7  | EBI | В | EBI0 LPDDR5 data bit 7  |  |

| M_D5  | EBI0_DQ_6  | EBI | В | EBI0 LPDDR5 data bit 6  |  |

| M_B5  | EBI0_DQ_5  | EBI | В | EBI0 LPDDR5 data bit 5  |  |

| M_E4  | EBI0_DQ_4  | EBI | В | EBI0 LPDDR5 data bit 4  |  |

| M_B2  | EBI0_DQ_3  | EBI | В | EBI0 LPDDR5 data bit 3  |  |

| M_D2  | EBI0_DQ_2  | EBI | В | EBI0 LPDDR5 data bit 2  |  |

| 1_F10 | EBI0_DQ_15 | EBI | В | EBI0 LPDDR5 data bit 15 |  |

| 1_D10 | EBI0_DQ_14 | EBI | В | EBI0 LPDDR5 data bit 14 |  |

| 1_B10 | EBI0_DQ_13 | EBI | В | EBI0 LPDDR5 data bit 13 |  |

| 1_E11 | EBI0_DQ_12 | EBI | В | EBI0 LPDDR5 data bit 12 |  |

| I_C13 | EBI0_DQ_11 | EBI | В | EBI0 LPDDR5 data bit 11 |  |

| 1_E13 | EBI0_DQ_10 | EBI | В | EBI0 LPDDR5 data bit 10 |  |

| M_C1  | EBI0_DQ_1  | EBI | В | EBI0 LPDDR5 data bit 1  |  |

| M_E1  | EBI0_DQ_0  | EBI | В | EBIO LPDDR5 data bit 0  |  |

| Pad # | Pad name        | Pad characte | ristics 1 | Functional description                                             |

|-------|-----------------|--------------|-----------|--------------------------------------------------------------------|

| Pau # | and/or function | Voltage      | Туре      | Functional description                                             |

| M_B12 | EBI0_RDQS_T_1   | EBI          | В         | EBI0 LPDDR5 differential read data strobe for byte 1 -<br>negative |

| M_E3  | EBI0_WCK_C_0    | EBI          | DO        | EBI0 LPDDR5 differential data clock for byte 0 - positive          |

| M_E12 | EBI0_WCK_C_1    | EBI          | DO        | EBI0 LPDDR5 differential data clock for byte 1 - positive          |

| M_F3  | EBI0_WCK_T_0    | EBI          | DO        | EBI0 LPDDR5 differential data clock for byte 0 - negative          |

| M_F12 | EBI0_WCK_T_1    | EBI          | DO        | EBI0 LPDDR5 differential data clock for byte 1 - negative          |

| M_AE9 | EBI1_CA_0       | EBI          | DO        | EBI1 LPDDR5 command/address bit 0                                  |

(80-11140-1 SM8450 SM8450P Data Sheet.pdf, Page 52 and 53)

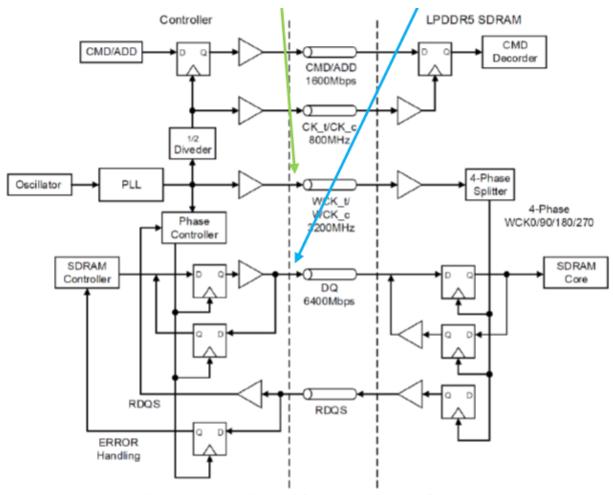

Figure 11 - Block Diagram of an Example System: CKR=4:1

(JEDEC Standard No. 209-5C, Page 25)

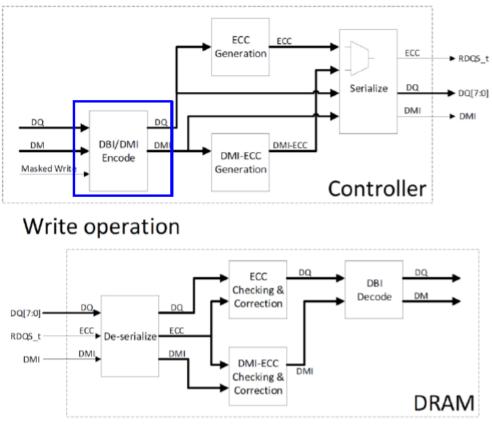

57. The '371 Accused Products processor unit is further configured to "set a preamble, wherein the preamble is a period of time between a first edge of the data clock signal and a first bit of the data signal." For instance, the '371 Accused Products such as the SM8450 incorporate a processor unit that sets a preamble, wherein the preamble is a period of time between a first edge of the data clock signal and a first bit of the data signal, and wherein the data clock signal is present only during a read or write operation initiated by the command instruction and during which data is read or written from or to the semiconductor memory apparatus, wherein the preamble is set by

setting a number of clock cycles of the data clock signal in the period of time defined by the preamble:

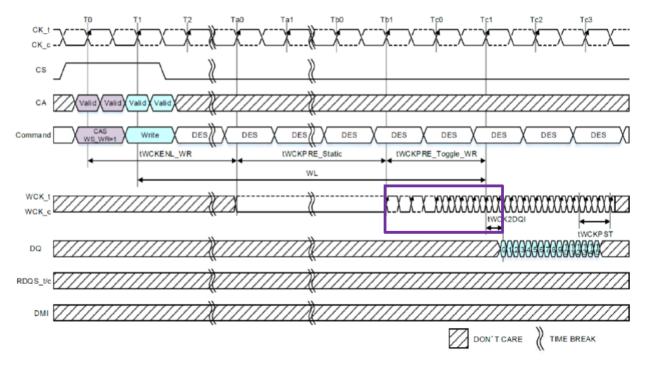

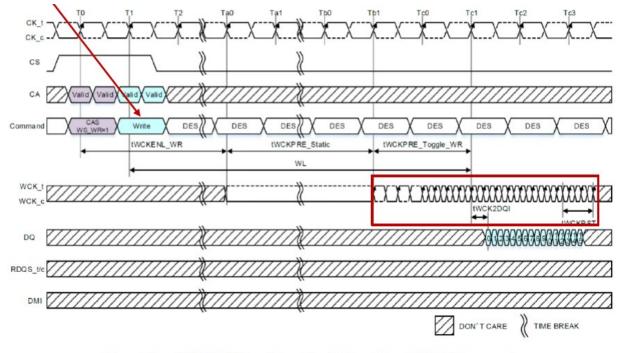

Figure 71 - WCK2CK Sync Operation Followed by a WRITE Command

(JEDEC Standard No. 209-5C, Page 197)

58. The '371 Accused Products processor unit is further configured "wherein the data clock signal is present only during a read or write operation initiated by the command instruction and during which data is read or written from or to the semiconductor memory apparatus." For instance, the '371 Accused Products such as the SM8450 incorporate a processor unit wherein the data clock signal is present only during a read or write operation initiated by the command instruction and during which data is read or write operation initiated by the command instruction and during which data is read or written from or to the semiconductor memory apparatus:

Figure 71 - WCK2CK Sync Operation Followed by a WRITE Command

(JEDEC Standard No. 209-5C, Page 197)

59. The '371 Accused Products processor unit is further configured "wherein the preamble is set by setting a number of clock cycles of the data clock signal in the period of time defined by the preamble." For instance, the '371 Accused Products such as the SM8450 incorporate a processor unit wherein the preamble is set by setting a number of clock cycles of the data clock signal in the period of time defined by the preamble:

| WCK:CK | Data<br>[Mb       |                   | CK Fre<br>[Mb     |                   | WL(SetA)                | WL(SetB)         | tWCKENL<br>_WR(SetA) | tWCKENL<br>WR(SetB) | tWCKPRE<br>Static | tWCKPRE<br>toggle_WR | tWCKPRE<br>total_WR |

|--------|-------------------|-------------------|-------------------|-------------------|-------------------------|------------------|----------------------|---------------------|-------------------|----------------------|---------------------|

| Ratio  | Lower<br>Limit(>) | Upper<br>Limit(≤) | Lower<br>Limit(>) | Upper<br>Limit(≤) | [nCK]                   | [nCK]            | [nCK]                | [nCK]               | [nCK]             | [nCK]                | [nCK]               |

|        | 40                | 533               | 10                | 133               | 4                       | 4                | 1                    | 1                   | 1                 | 3                    | 4                   |

|        | 533               | 1067              | 133               | 267               | 4                       | 6                | 0                    | 2                   | 2                 | 3                    | 5                   |

|        | 1067              | 1600              | 267               | 400               | 6                       | 8                | 1                    | 3                   | 2                 | 4                    | 6                   |